quartus的使用流程

第一步 创建project

file -> new project

设置保存路径以及project的名字。

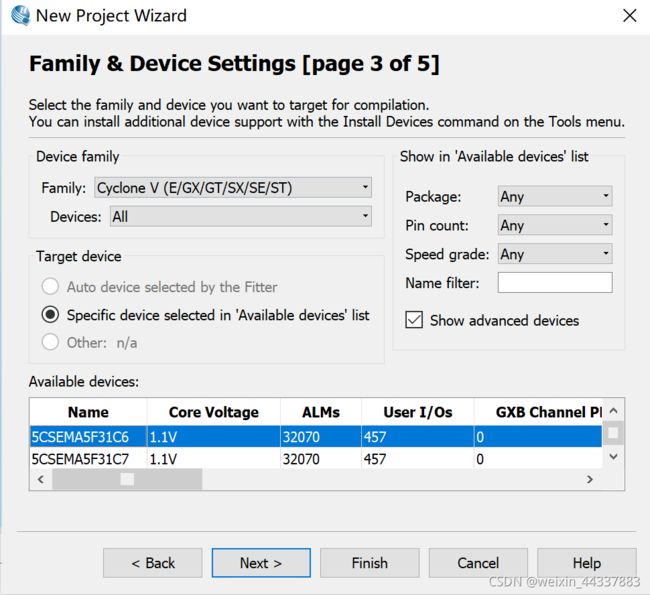

选择你需要使用的FPGA芯片型号,可在name filter中查找。

在此选项选择仿真需要使用的软件modelsim-altera以及testbench所使用的语言。

最终我们就得到一个新建的project。

如果已经有project,那么file-> open project 即可。

第二步 在project中添加file

在一个工程下存在多个文件,所以根据需要在project中添加所需要的文件。

添加新文件 file -> new -> 选择使用的语言

添加已经存在的文件 project -> add/remove files in project

几个注意事项:

保存文件时,需要将文件名和模块名保持一致,方便以后调用。

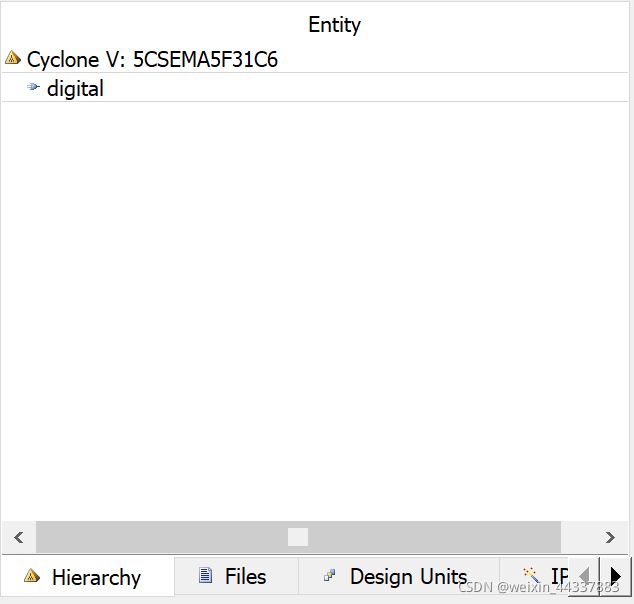

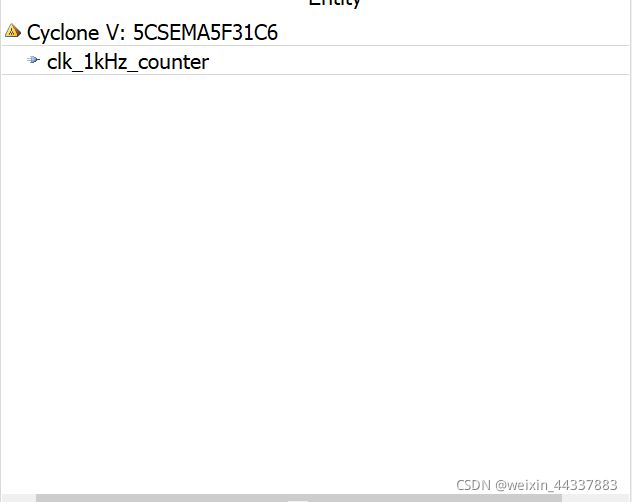

顶层模块和子模块。设置一个模块为顶层模块时,右键该模块,选择set as top-level entity

这时我们的工程项目列表显示的就是我们的顶层模块的名字。

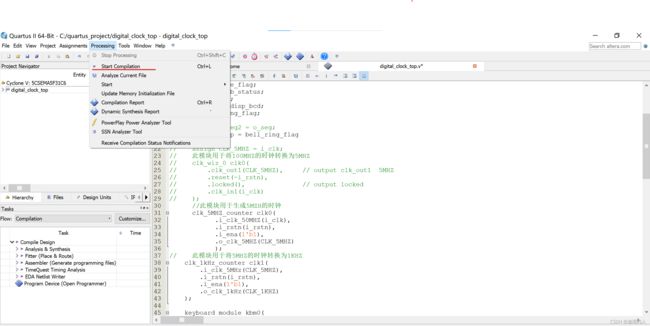

或者直接点击:

(下面的步骤是在确认编译没有错误后,直接将程序下载到板子上的操作,如果要做波形仿真或者写testbench文件可以参考下一章)

第三步 添加引脚约束

完成编程,并编译无错后,需要对引脚进行约束,这样才可以将程序下载到板子上。

进行引脚约束的方法有以下 种

1. assignment -> pin planner 直接进行约束。在location 和I/Ostandard设置引脚所在位置和电平约束。

2.书写所需要的.tcl文件 new -> tcl Scripts file 在这里面书写自己所需要的约束。

quartus也可以自动生成.tcl文件。

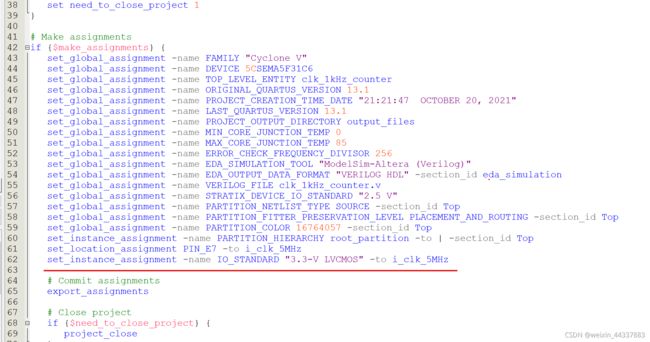

生成的.tcl文件只是指明了设备及工程约束我们可以在下面对使用的端口进行相关的声明。

.tcl 文件中书写管脚约束的格式

//引脚位置声明

set_location_assignment (管脚) -to (信号)

//引脚电平声明

set_instance_assignment -name IO_STANDARD "(电平规范)" -to (信号)

举例:

set_location_assignment PIN_E7 -to i_clk_5MHz

set_instance_assignment -name IO_STANDARD "3.3-V LVCMOS" -to i_clk_5MHz3.导入已有的 .tcl文件 tools -> tcl Scripts 选择需要导入的tcl文件 点击run。

第一种方法适合管脚约束较少的情况操作方便。

第二种方法直观、明了。

第四步 下载到板子上

分配完引脚并编译没错后就可以下载到板子上(不需要仿真)

在将程序下载到板子上之前需要实现板子和电脑端能够正常通信(能够识别板子)。

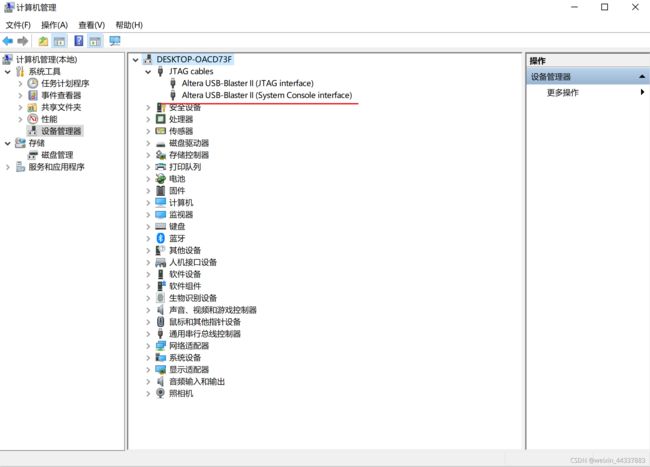

以我使用的cyclon V 5CSEMA5F31C6 为例,将usb数据线连接电脑和板子,打开计算机管理,在其他设备上出现一个未知设备,右击该设备更新驱动,在更新驱动中选择文件夹/C:\altera\13.1\quartus\drivers\usb-blaster-ii 更新即可。

更新完成后电脑就可以识别出器件。

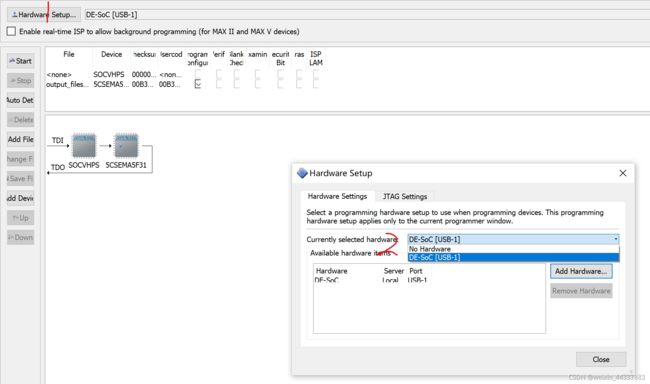

打开quartus中的programmer

edit -> add file 将我们生成的.sof文件导入 点击star 就可以开始下载程序了。