DRAM知识整理系列(三):部分时序参数整理

目录

一、时序参数整理

第一时序:

1、tCL - CAS Lantency Control

2、tRCD - RAS to CAS Delay

3、tRP - Row Precharge Timing

4、tRAS - RAS Active Time

第二时序:

5、CWL - CAS Write Latency

6、tRC - Row Cycle Time

7、tRFC - Row Refresh Cycle Time

8、tRRD - Row to Row Delay

9、tWR - Write Recovery Time

10、tWTR - Write to Read Delay

11、tREF - Refreshh Period

12、tFAW - Four Active Window

13、tCCD - CAS to CAS Delay

一、时序参数整理

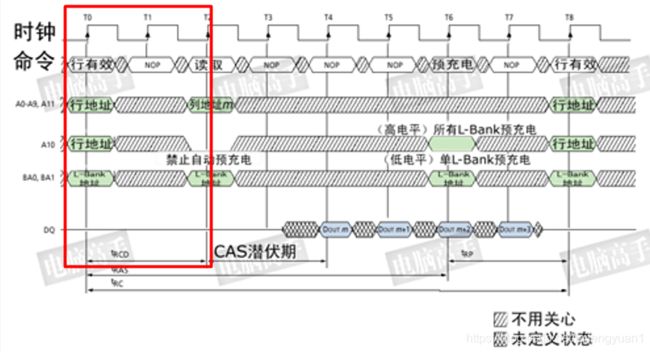

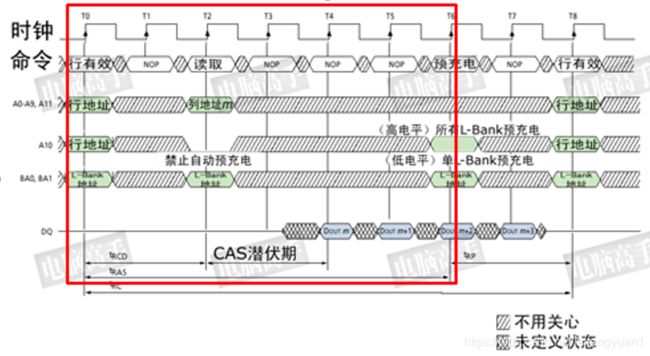

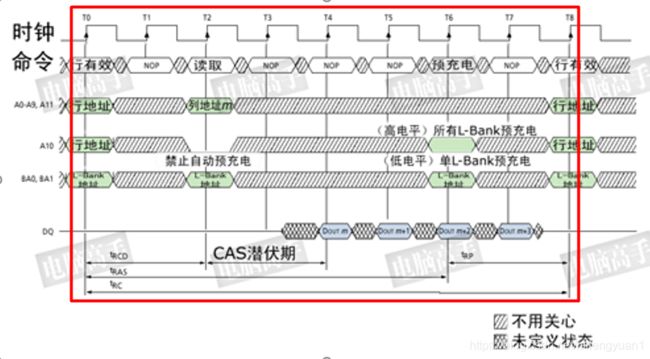

内存是根据行和列寻址的,当请求触发后,最初是tRAS(Active to precharge Delay),预充电后,内存才真正开始初始化RAS(Row Address Strobe)。一旦tRAS激活后,RAS开始进行需要数据的寻址。首先是行地址,然后初始化tRCD(RAS to CAS Delay),周期结束,接着通过CAS(Column Address Strobe)访问所需数据的十六进制地址。其中,从CAS开始到CAS结束,就是CAS延迟(即tCL)。所以CAS是找到数据的最后一个步骤,(tCL)也是内存参数中最重要的。

第一时序:

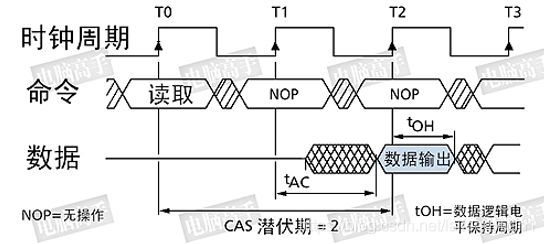

1、tCL - CAS Lantency Control

tCL(CAS Lantency Control):内存读写操作前列地址控制器的潜伏时间,一般单位为tCK(即:单位时钟周期)

- CAS 控制从接受一个指令到指令执行之间的时间。

- 因为 CAS 主要控制十六进制的地址,或者说是内存矩阵中的列地址,所以它是最为重要的参数,在保持稳定的前提下应该尽可能设低。

- 对内存读写性能影响最大。

具体时间计算公式:tCL(ns) = (CL * 2000) / 内存频率

如:DDR3-1333-CL9。tCAS = (9 * 2000) / 1333 = 13.5(ns)

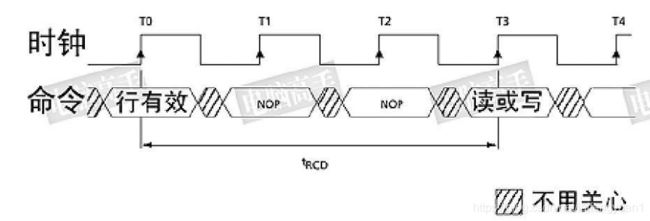

2、tRCD - RAS to CAS Delay

tRCD(RAS to CAS Delay,又可以称为:Acitve to CMD):行寻址到列寻址延迟时间,一般单位为tCK(即:单位时钟周期)

- 对内存进行读、写或刷新操作时,需要在这两种脉冲信号之间插入延迟时钟周期。

- 在JEDEC规范中,它是排在第二的参数,降低此延迟,可以提高系统性能。

- 如果内存的超频性能不佳,可以将此值设置成内存默认值或者提高tRCD的值。

- 对内存最大频率影响最大

3、tRP - Row Precharge Timing

tRP( Row Precharge Timing,又可以称为:Precharge to Active):内存行地址控制器预充电时间,一般单位为tCK(即:单位时间周期)

- tRP用来设定在另一行能被激活之前,RAS需要的充电时间。

- tRP参数太长会导致所有的行激活延迟过;设置太短可能会导致行激活之前的数据丢失,内存控制器不能顺利地完成读写操作。

4、tRAS - RAS Active Time

tRAS(RAS Active Time,又可以称为:Active to Prechage Delay) :内存行有效至预充电的最短周期

- 如果tRAS等待周期太长,系统会因为无意义的等待而降低性能。若tRAS等待周期太短,则会导致已被激活的行地址会更早的进入非激活状态,这样可能会因为缺少足够的时间而无法完成数据的突发传输

- tRAS的值一般设置为 tRAS(推荐)= tCL + tRCD + tRTP

- 为提高系统性能,应尽可能降低tRAS的值,但是如果发生内存错误或系统死机,则应该增大tRAS的值。

第二时序:

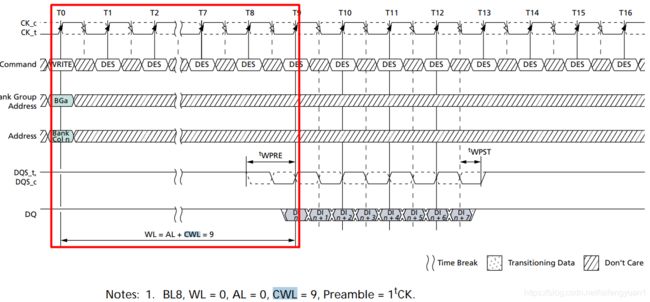

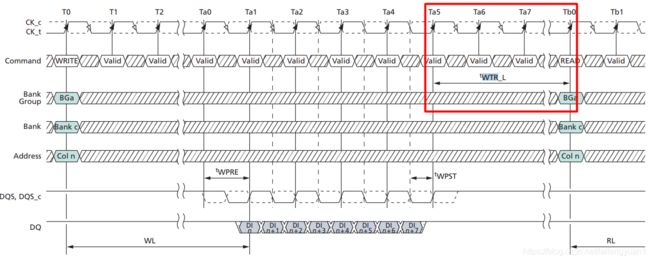

5、CWL - CAS Write Latency

CWL(CAS Write Latency):列地址写入延迟,与CL刚好是读写对应关系。

- 一般与CL设置同一个值是可以稳定的。(即 CWL = CL 一般可以稳定)

- Controller 在发送完Write Command后,需要等待tCWL时间后,才可以发送写入的数据。

6、tRC - Row Cycle Time

tRC( Row Cycle Time):定义了同一bank两次行激活命令所间隔的最小时间,或者说是一个bank中完成一次行操作周期(Row Cycle)的时间

- 计算公式:tRC = tRAS + tRP

- tRC过长会导致无意义的延时等待,降低性能;tRC过短,情况和tRP过短情况差不多,在会导致被激活的行单元被充分充电之前,新的周期就被初始化了,这样会导致数据丢失和损坏。

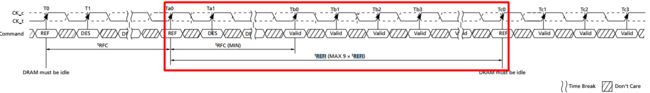

7、tRFC - Row Refresh Cycle Time

tRFC(Row Refresh Cycle Time):SDRAM行刷新周期时间,它是行单元刷新所需要的时钟周期数或者是纳秒(ns)。定义了一个bank中行地址刷新所需要的时间,容量大的bank行地址和cell单元会更多,刷新时间更长,因此tRFC也要更高。

在AMD平台的tRFC是DRAM刷新延迟时间,单位是ns,通常有90/110/160/300几个值可以调整,也就是说它的tRFC时钟周期会随着频率的提升而提升。

Intel平台的单位则直接是时钟周期,相反地延迟时间会随着频率的提升而降低。容量大的bank行地址和cell会更多,刷新时间也更长,因此tRFC也要更高。

- 该值表示行地址刷新所需要的时间。

- tRFC的值越小越好,它比tRC的值要稍高一点。

- tRFC的值与内存容量密度和工作频率有关。

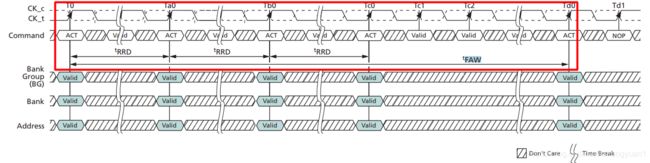

8、tRRD - Row to Row Delay

tRRD(Row to Row Delay):行单元到行单元的延时。

- 该值还表示向相同bank中的 同 一个行单元两次发送激活指令(即:REF)之间的时间间隔。

- tRRD的值越小越好,延迟越低,表示下一个bank能更快地被激活,进行读写操作。然而如果延迟太短,会引起连续数据膨胀。

- tRRD_S表示不同bank,tRRD_L表示相同bank

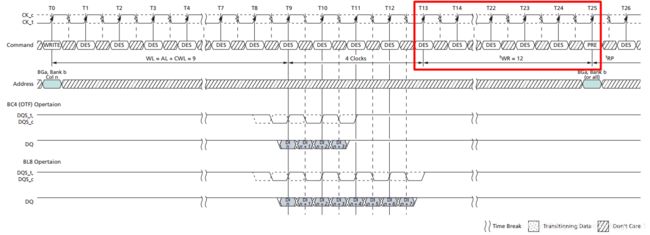

9、tWR - Write Recovery Time

tWR(Write Recovery Time):写恢复延时(即:写完数据后,到预充电命令前的延时)

- 该值说明在一个激活的bank中完成有效的写操作以及与预充电前,必须等待多少个时钟周期。这段必须的时钟周期,用来确保在预充电发生前,写缓冲中的数据可以被写入内存单元中。

- 较低的tWR可以提高系统性能,但可能导致数据还未完全正确写入内存单元,就发生了预充电操作,导致数据的丢失和损坏。

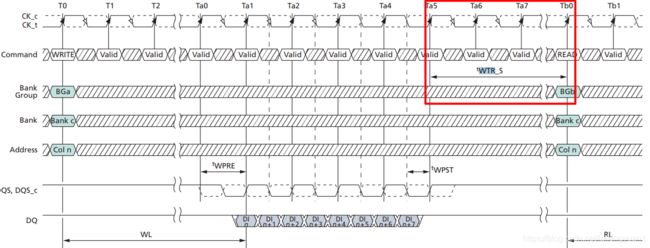

10、tWTR - Write to Read Delay

tWTR(Write to Read Delay):写到读延时(即:最后的数据进入读指令)

- 该值表示的是,DDR内存模块中的同一个单元中,在最后一次有效的写操作和下一次读操作之间必须等待的时钟周期。

- 增加tWTR的值,可以让内容模块运行比其默认速度更快的速度下;减小tWTR的值,可以提高读性能,但会降低系统稳定性。

- tWTR_S表示不同bank,tWTR_L表示相同bank

11、tREF - Refreshh Period

tREF (Refreshh Period):刷新周期,它指的是内存模块的刷新周期。(一般为微秒,us)

- tREFI 指的是平均刷新间隔。从原理上看,DRAM存储单元基于一个电容,64ms是电容的放电时间。DRAM是按照行列组织的,执行一个刷新命令会把某行上所有的存储单元(电容)充电。换句话说,如果DRAM有8192个行,那么就需要在64ms之内执行8192次刷新操作(64 ms / 8192 = 7.81us),无论是摊开平均执行,还是集中突发执行。DDR3允许突发执行8个刷新操作——你既可以先突发执行8个刷新操作,然后等上9*tREFI时间啥事都不干;或者你先发呆9*tREFI时间,然后突发执行8个刷新操作。总之就是要记住,DRAM每行上面的存储单元一定要在64ms之内得到刷新。

- tREFI 的值与 容量密度还有和工作温度有关。

12、tFAW - Four Active Window

tFAW(Four Active Window):它定义了一个rank中允许同时发送大于4个bank行激活的命令的间隔时间

- tFAW >= 4 * tRRD

- 由于tFAW是在一个rank中大于4个bank同时激活之后才生效的,所以在内存不是很繁忙的时候,它对性能的影响并不是很大。但是对一些频繁读写内存的操作,tFAW对性能的影响可能会加大 。

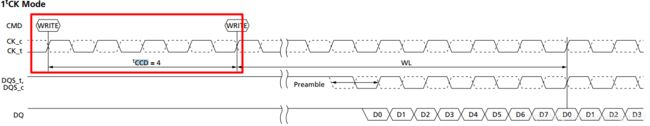

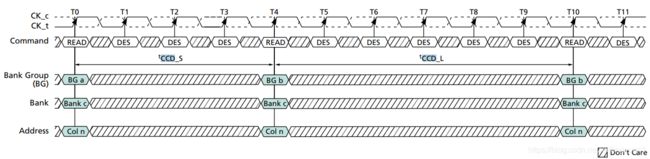

13、tCCD - CAS to CAS Delay

tCCD(CAS to CAS Delay):CAS命令到CAS命令之间的时间间隔