Cyclone II的IO资源学习

IO资源

IO是与外界沟通和控制的通道,fpga提供了丰富的IO和一些实用的特性。

本文简要的将主要的特性摘录下来做设计参考用。具体参数参考handbook。

第一部分:IO特性概述

-----通过软件的灵活配置,可适应不同的电器标准与I/O物理特性;可以调整匹配阻抗特性,上下拉电阻;可以调整输出驱动电流的大小等。

可编程上拉(Each Cyclone II device I/O pin provides an optional programmable

pull-up resistor during user mode. If you enable this feature for an I/O

pin, the pull-up resistor (typically 25 kΩ) holds the output to the VCCIO

level of the output pin’s bank.)

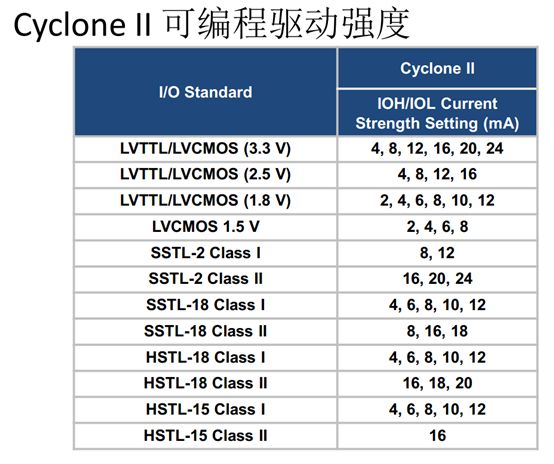

The output buffer for each Cyclone II device I/O pin has a programmable

drive strength control for certain I/O standards. The LVTTL, LVCMOS,

SSTL-2 class I and II, SSTL-18 class I and II, HSTL-18 class I and II, and

HSTL-1.5 class I and II standards have several levels of drive strength that

you can control. Using minimum settings provides signal slew rate

control to reduce system noise and signalovershoot. Table 2–16shows

the possible settings for the I/O standards with drive strength control.

-----总线保持和三态输出(总线保持与上拉冲突)

Each Cyclone II device user I/O pin provides an optional bus-hold

feature. The bus-hold circuitry can holdthe signal on an I/O pin at its

last-driven state. Since the bus-hold feature holds the last-driven state of

the pin until the next input signal ispresent, an external pull-up or

pull-down resistor is not necessary to hold a signal level when the bus is

tri-stated.

--------Fpga 的IO与单片机不一样 它的IO和内核的供电是分离的。

我们可以根据器件特性配置IO的电压比如 3.3v 2.5v 1.8v等

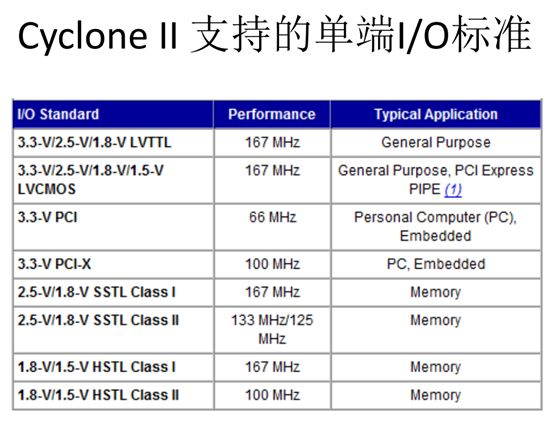

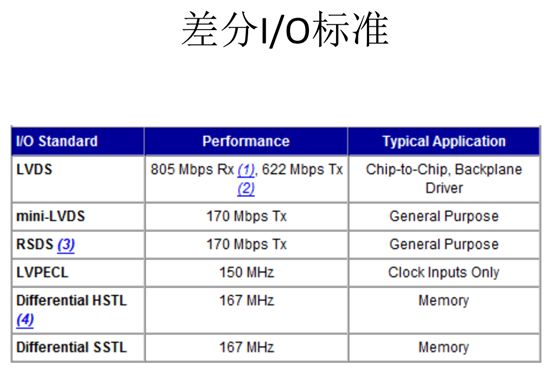

同时更有高级接口可供使用比如PCI LVDS RSDS SSTL SDRAM等。

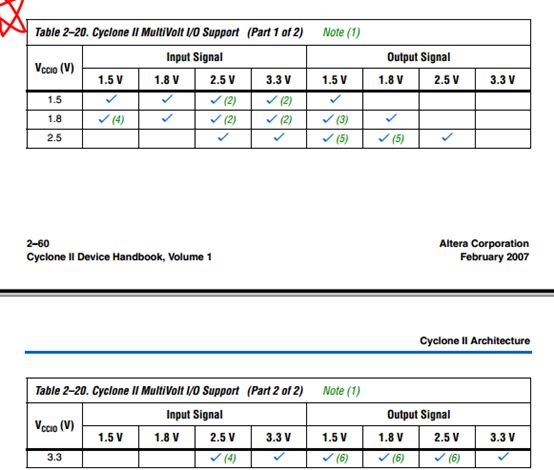

The Cyclone II architecture supports the MultiVolt I/O interface feature,

which allows Cyclone II devices in all packages to interface with systems

of different supply voltages. Cyclone II devices have one set of VCCpins

(VCCINT) that power the internal device logic array and input buffers that

use the LVPECL, LVDS, HSTL, or SSTL I/O standards. Cyclone II devices

also have four or eight sets of VCC pins (VCCIO) that power the I/O

output drivers and input buffers that use the LVTTL, LVCMOS, or PCI

I/O standards.

The Cyclone II VCCINTpins must always be connected to a 1.2-V power

supply. If the VCCINTlevel is 1.2 V, then input pins are 1.5-V, 1.8-V, 2.5-V,

and 3.3-V tolerant. The VCCIOpins can be connected to either a 1.5-V,

1.8-V, 2.5-V, or 3.3-V power supply, depending on the output

requirements. The output levels are compatible with systems of the same

voltage as the power supply (i.e., when VCCIOpins are connected to a

1.5-V power supply, the output levels are compatible with 1.5-V systems).

When VCCIOpins are connected to a 3.3-V power supply, the output high

is 3.3-V and is compatible with 3.3-V systems. Table 2–20summarizes

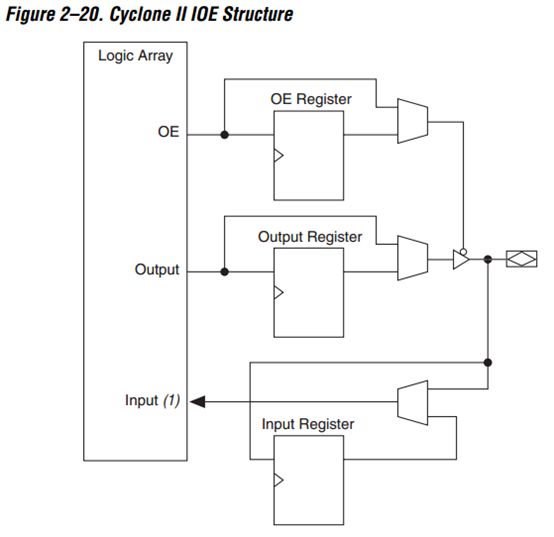

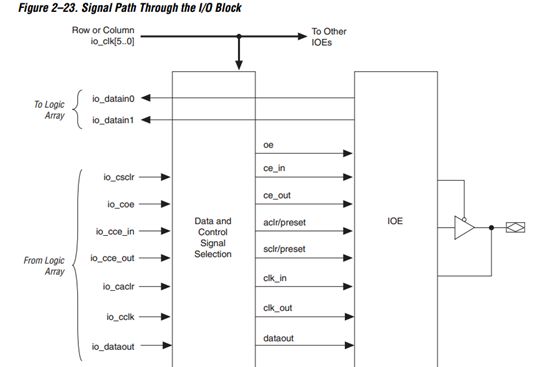

(Each Cyclone II device I/O pin is fed byan IOE located at the ends of LAB

rows and columns around the periphery of the device. I/O pins support

various single-ended and differential I/O standards, such as the 66- and

33-MHz, 64- and 32-bit PCI standard, PCI-X, and the LVDS I/O standard

at a maximum data rate of 805 megabitsper second (Mbps) for inputs and

640 Mbps for outputs. Each IOE contains a bidirectional I/O buffer and

three registers for registering input,output, and output-enable signals.

Dual-purpose DQS, DQ, and DM pins along with delay chains (used tophase-align double data rate (DDR) signals) provide interface support for external memory devices such as DDR, DDR2, and single data rate (SDR) SDRAM, and QDRII SRAM devices at up to 167 MHz. )

------有些fpga的引脚是兼容的很方便升级扩展。

-------未用的时钟引脚可做输入

(The I/O pin counts for the EP2C5, EP2C8, and EP2C15A devices include 8 dedicated clock pins that can be used for data inputs. )

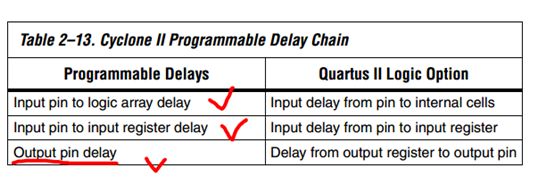

-----------IO延时可编程

The Cyclone II device IOE includes programmable delays to ensure zero

hold times, minimize setup times, or increase clock to output times.The Quartus II Compiler can program these delays to automatically minimize setup timewhile providing a zero hold time.

------可编程IO上电后电平

The IOE registers in each I/O block share the same source for clear or

preset. You can program preset or clear for each individual IOE, but both

features cannot be used simultaneously. You can also program the

registers to power up high or low after configuration is complete. If

programmed to power up low, an asynchronous clear can control the

registers. If programmed to power uphigh, an asynchronous preset can

control the registers. This feature prevents the inadvertent activation of

another device’s active-low input uponpower up. If one register in an

IOE uses a preset or clear signal then all registers in the IOE must use that

same signal if they require preset or clear. Additionally a synchronous

reset signal is available for the IOE registers.

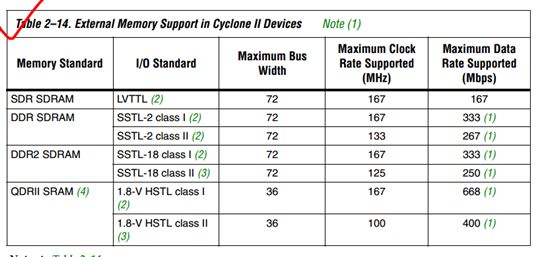

----丰富的外部存储器控制接口

Cyclone II devices support a broad range of external memory interfaces

such as SDR SDRAM, DDR SDRAM,DDR2 SDRAM, and QDRII SRAM

external memories. Cyclone II devices feature dedicated high-speed

interfaces that transfer data between external memory devices at up to

167 MHz/333 Mbps for DDR and DDR2 SDRAM devices and

167 MHz/667 Mbps for QDRII SRAM devices. The programmable DQS

delay chain allows you to fine tune the phase shift for the input clocks or

strobes to properly align clock edges as needed to capture data.

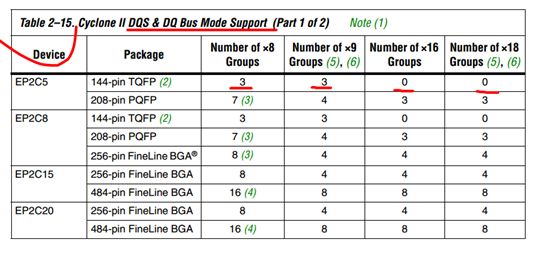

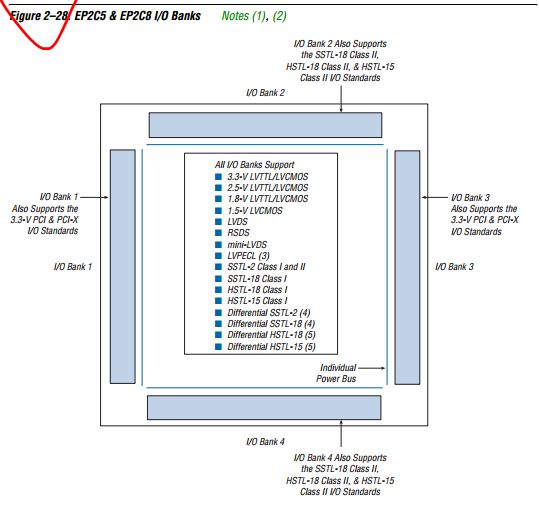

In Cyclone II devices, all the I/O banks support SDR and DDR SDRAM

memory up to 167 MHz/333 Mbps. All I/O banks support DQS signals

with the DQ bus modes of ×8/×9, or ×16/×18. Table 2–14shows the

external memory interfaces supported in Cyclone II devices.

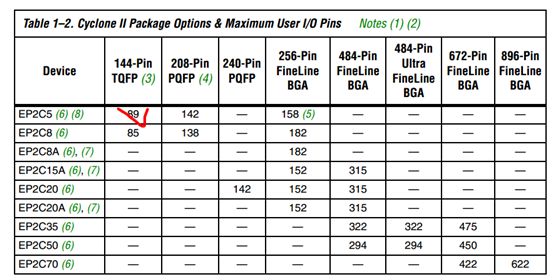

第二部分:引脚与IOE

先看下cyclone II系列引脚数

IO整体特性

IOEs support many features, including:

■ Differential and single-ended I/O standards

■ 3.3-V, 64- and 32-bit, 66- and 33-MHz PCI compliance

■ Joint Test Action Group (JTAG) boundary-scan test (BST) support

■ Output drive strength control

■ Weak pull-up resistors during configuration

■ Tri-state buffers

■ Bus-hold circuitry

■ Programmable pull-up resistors in user mode

■ Programmable input and output delays

■ Open-drain outputs

■ DQ and DQS I/O pins

■ VREFpins

IOE结构

配置管脚:(具体用法可看altera cyclone系列 配置文档)

MSEL[1:0] 用于选择配置模式,比如AS、PS等。

DATA0 FPGA串行数据输入,连接到配置器件的串行数据输出管脚。

DCLK FPGA串行时钟输出,为配置器件提供串行时钟。

nCSO(I/O)FPG**选信号输出,连接到配置器件的nCS管脚。

ASDO(I/O)FPGA串行数据输出,连接到配置器件的ASDI管脚。

nCEO 下载链期间始能输出。在一条下载链中,当第一个器件配置完成后,此信号将始能下一个器件开始进行配置。下载链上最后一个器件的nCEO悬空。

nCE 下载链器件始能输入,连接到上一个器件的nCEO,下载链的最后一个器件nCE接地。

nCNFIG 用户模式配置起始信号。

nSTATUS 配置状态信号。

CONF_DONE 配置结束信号。

电源管脚:

VCCINT 内核电压。130nm为1.5V,90nm为1.2V

VCCIO 端口电压。一般为3.3V,还可以支持多种电压,5V、1.8V、1.5V

VREF 参考电压

GND 信号地

时钟管脚:

VCC_PLL PLL管脚电压,直接连VCCIO

VCCA_PLL PLL模拟电压,截止通过滤波器接到VCCINT上

GNDA_PLL PLL模拟地

GNDD_PLL PLL数字地

CLK[n] PLL时钟输入

PLL[n]_OUT PLL时钟输出

特殊管脚:

VCCPD 用于寻则驱动

VCCSEL 用于控制配置管脚和PLL相关的输入缓冲电压

PROSEL 上电复位选项

NIOPULLUP 用于控制配置时所使用的用户I/O的内部上拉电阻是否工作

TEMPDIODEN 用于关联温度敏感二极管

其他特殊引脚 :

原文地址:FPGA的特殊引脚说明作者:tengfeixinxiang

1/1.I/O, ASDO

在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用。在AS 模式下,这个脚是CII 向串行配置芯片发送控制信号的脚。也是用来从配置芯片中读配置数据的脚。在AS 模式下,ASDO 有一个内部的上拉电阻,一直有效,配置完成后,该脚就变成三态输入脚。ASDO 脚直接接到配置芯片的ASDI 脚(第5 脚)。

2/2.I/O,nCSO

在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用.在AS 模式下,这个脚是CII 用来给外面的串行配置芯片发送的使能脚。在AS 模式下,ASDO 有一个内部的上拉电阻,一直有效。这个脚是低电平有效的。直接接到配置芯片的/CS 脚(第1 脚)。

3/3.I/O,CRC_ERROR

当错误检测CRC 电路被选用时,这个脚就被作为CRC_ERROR 脚,如果不用默认就用来做I/O。但要注意,这个脚是不支持漏极开路和反向的。当它作为CRC_ERROR 时,高电平输出则表示出现了CRC 校验错误(在配置SRAM 各个比特时出现了错误)。CRC 电路的支持可以在setting 中加上。这个脚一般与nCONFIG 脚配合起来用。即如果配置过程出错,重新配置.

4/4.I/O,CLKUSR

当在软件中打开Enable User-supplled start-up clock(CLKUSR)选项后,这个脚就只可以作为用户提供的初始化时钟输入脚。在所有配置数据都已经被接收后,CONF_DONE 脚会变成高电平,CII 器件还需要299 个时钟周期来初始化寄存器,I/O 等等状态,FPGA 有两种方式,一种是用内部的晶振(10MHz),另一种就是从CLKUSR 接进来的时钟(最大不能超过100MHz)。有这个功能,可以延缓FPGA 开始工作的时间,可以在需要和其它器件进行同步的特殊应用中用到。

7/13.I/O,VREF

用来给某些差分标准提供一个参考电平。没有用到的话,可以当成I/O 来用。

14/20. DATA0

专用输入脚。在AS 模式下,配置的过程是:CII 将nCSO 置低电平,配置芯片被使能。CII然后通过DCLK 和ASDO 配合操作,发送操作的命令,以及读的地址给配置芯片。配置芯片然后通过DATA 脚给CII 发送数据。DATA 脚就接到CII 的DATA0 脚上。CII 接收完所有的配置数据后,就会释放CONF_DONE 脚(即不强制使CONF_DONE 脚为低电平),CONF_DONE 脚是漏极开路(Open-Drain)的。这时候,因为CONF_DONE 在外部会接一个10K 的电阻,所以它会变成高电平。同时,CII 就停止DCLK 信号。在CONF_DONE 变成高电平以后(这时它又相当于变成一个输入脚),初始化的过程就开始了。所以,CONF_DONE 这个脚外面一定要接一个10K 的电阻,以保证初始化过程可以正确开始。 DATA0,DCLK,NCSO,ASDO 脚上都有微弱的上拉电阻,且一直有效。在配置完成后,这些脚都会变成输入三态,并被内部微弱的上拉电阻将电平置为高电平。在AS 模式下,DATA0就接到配置芯片的DATA(第2 脚)。

15/21. DCLK

PS 模式下是输入,AS 模式下是输出。在PS 模式下,DCLK 是一个时钟输入脚,是外部器件将配置数据传送给FPGA 的时钟。数据是在DCLK 的上升沿把数据,在AS 模式下,DCLK脚是一个时钟输出脚,就是提供一个配置时钟。直接接到配置芯片的DCLK 脚上去(第6脚)。无论是哪种配置模式,配置完成后,这个脚都会变成三态。如果外接的是配置器件,配置器件会置DCLK 脚为低电平。如果使用的是主控芯片,可以将DCLK 置高也可以将DCLK 置低。配置完成后,触发这个脚并不会影响已配置完的FPGA。这个脚带了输入Buffer,支持施密特触发器的磁滞功能。

16/22. nCE

专用输入脚。这个脚是一个低电平有效的片选使能信号。nCE 脚是配置使能脚。在配置,初始化以及用户模式下,nCE 脚必须置低。在多个器件的配置过程中,第一个器件的nCE 脚要置低,它的nCEO 要连接到下一个器件的nCE 脚上,形成了一个链。nCE 脚在用JTAG编程模式下也需要将nCE 脚置低。 这个脚带了输入Buffer,支持施密特触发器的磁滞功能。

20/26. nCONFIG

专用的输入管脚。这个管脚是一个配置控制输入脚。如果这个脚在用户模式下被置低,FPGA就会丢失掉它的配置数据,并进入一个复位状态,并将所有的I/O 脚置成三态的。nCONFIG从低电平跳变到高电平的过程会初始化重配置的过程。如果配置方案采用增强型的配置器件或EPC2,用户可以将nCONFIG 脚直接接到VCC 或到配置芯片的nINIT_CONF 脚上去。这个脚带了输入Buffer,支持施密特触发器的磁滞功能。实际上,在用户模式下,nCONFIG信号就是用来初始化重配置的。当nCONFIG 脚被置低后,初始化进程就开始了。当nCONFIG脚被置低后,CII 就被复位了,并进入了复位状态,nSTATUS 和CONF_DONE 脚被置低,所有的I/O 脚进入三态。nCONFIG 信号必须至少保持2us。当nCONFIG 又回到高电平状态后,nSTATUS 又被释放。重配置就开始了。在实际应用过程中可以将nCONFIG 脚接一个10K 的上拉电阻到3.3V.

40/56. DEV_OE

I/O 脚或全局I/O 使能脚。在Quartus II 软件中可以使能DEV_OE 选项(Enable Device-wideoutput Enable),如果使能了这一个功能,这个脚可以当全局I/O 使能脚,这个脚的功能是,如果它被置低,所有的I/O 都进入三态。

75/107. INIT_DONE

I/O 脚或漏极开路的输出脚。当这个脚被使能后,该脚上从低到高的跳变指示FPGA 已经进入了用户模式。如果INIT_DONE 输出脚被使能,在配置完成以后,这个脚就不能被用做用户I/O 了。在QuartusII 里面可以通过使能Enable INIT_DONE 输出选项使能这个脚。

76/108. nCEO

I/O 脚或输出脚。当配置完成后,这个脚会输出低电平。在多个器件的配置过程中,这个脚会连接到下一个器件的nCE 脚,这个时候,它还需要在外面接一个10K 的上拉电阻到Vccio。多个器件的配置过程中,最后一个器件的nCEO 可以浮空。如果想把这个脚当成可用的I/O,需要在软件里面做一下设置。另外,就算是做I/O,也要等配置完成以后。

82/121. nSTATUS

这是一个专用的配置状态脚。双向脚,当它是输出脚时,是漏极开路的。在上电之后,FPGA立刻将nSTATUS 脚置成低电平,并在上电复位(POR)完成之后,释放它,将它置为高电平。作为状态输出脚时,在配置过程中如果有任何一个错误发生了,nSTATUS 脚会被置低。作为状态输入脚时,在配置或初始化过程中,外部控制芯片可以将这个脚拉低,这时候FPGA就会进入错误状态。这个脚不能用作普通I/O 脚。nSTATUS 脚必须上拉一个10K 欧的电阻。

83/123. CONF_DONE

这是一个专用的配置状态脚。双向脚,当它是输出脚时,是漏极开路的。当作为状态输出脚时,在配置之前和过程中,它都被置为低电平。一旦配置数据接收完成,并且没有任何错误,初始化周期一开始,CONF_DONE 就会被释放。当作为状态输入脚时,在所有数据都被接收后,要将它置为高电平。之后器件就开始初始化再进入用户模式。它不可以用作普通I/O来用。这个脚外成也必须接一个10K 欧的电阻。

84/125,85/126. MSEL[1:0]

这些脚要接到零或电源,表示高电平或低电平。00 表示用AS 模式,10 表示PS 模式, 01是FAST AS 模式.如果用JTAG 模式,就把它们接00, JTAG 模式跟MSEL 无关,即用JTAG模式,MSEL 会被忽略,但是因为它们不能浮空,所以都建议将它接到地。

142/206 DEV_CLRn

I/O 或全局的清零输入端。在Quartus II 里面,如果选上Enable Device-Wide Reset(DEV_CLRn)这个功能。这个脚就是全局清零端。当这个脚被置低,所有的寄存器都会被清零。这个脚不会影响到JTAG 的边界扫描或编程的操作。

支持的高级接口与速度:

更多详细参数 参考 cyclone II handbook