m基于Lorenz混沌自同步的混沌数字保密通信系统的FPGA实现,verilog编程实现,带MATLAB混沌程序

目录

1.算法描述

2.部分程序

3.部分仿真图预览

4.源码获取方式

1.算法描述

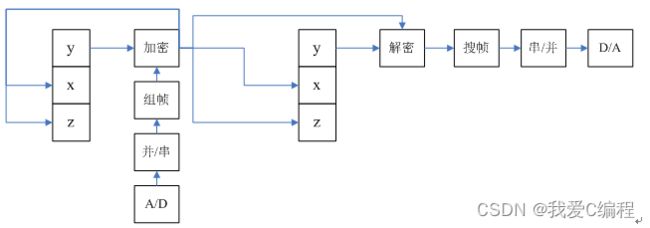

本系统的基本结构框图如下所示:

系统顶层文件

——加密调制模块

————加密子模块,lorenz混沌序列产生模块,组帧模块,并串模块。

——解密解调模块

————解密子模块,Lorenz混沌序列产生模块,搜帧模块,串并模块。

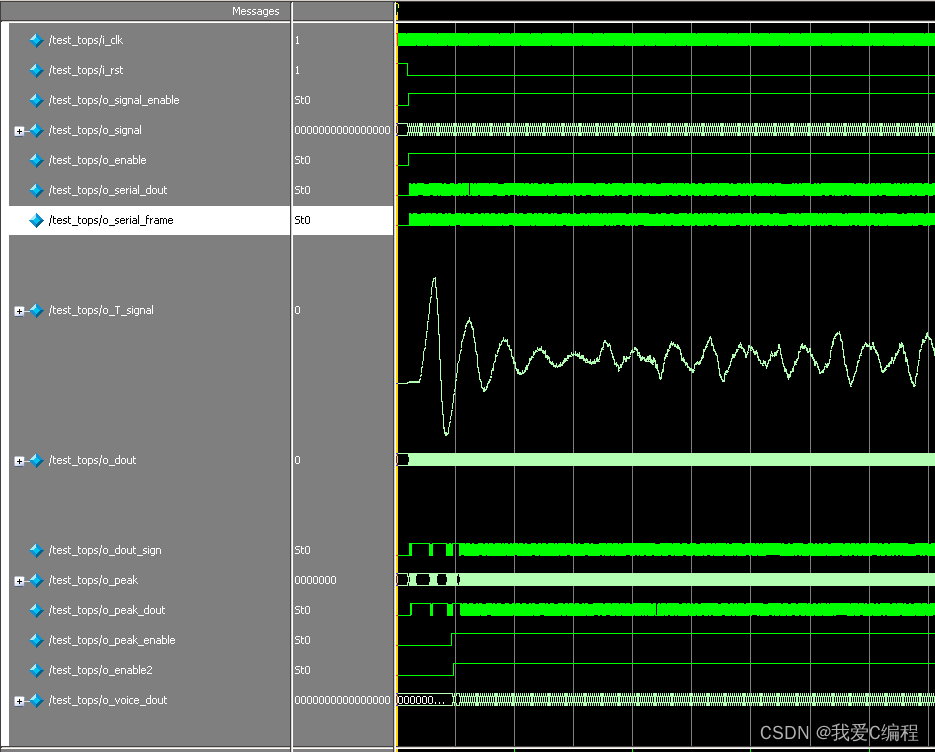

其顶层的文件的管脚为:

| 1 |

i_clk |

系统时钟,就是接到硬件板子上的晶振位置。 |

| 2 |

i_rst |

系统复位,随便接到板子上的key数字按键上。 |

| 3 |

o_signal_enable |

测试并行信号的产生使能信号,不用接板子, |

| 4 |

o_signal |

测试并行信号,这个信号为了验证,你可以接signaltapII上 |

| 5 |

o_enable |

加密模块的使能信号,不用接板子 |

| 6 |

o_serial_dout |

串行输出,接板子上的测试脚或者signaltapII上 |

| 7 |

o_serial_frame |

串行信号组帧输出,接板子上的测试脚或者signaltapII上 |

| 8 |

o_T_signal |

加密输出,这个信号为了验证,你可以接signaltapII上 |

| 9 |

o_dout |

解密输出,可以接signaltapII上 |

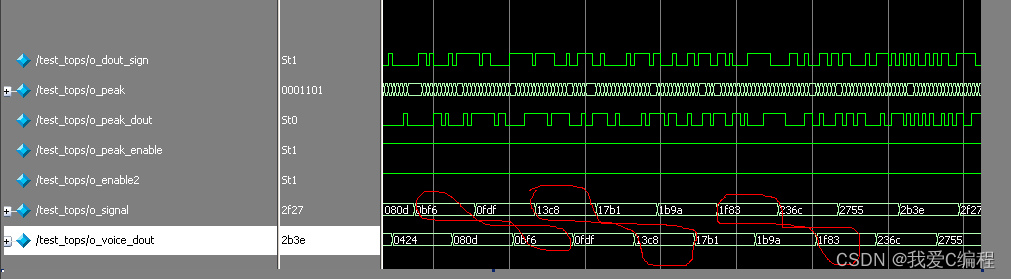

| 10 |

o_dout_sign |

解密输出信号的符号判决,接板子上的测试脚或者signaltapII上 |

| 11 |

o_peak |

搜帧模块的相关峰输出,不用接板子 |

| 12 |

o_peak_enable, |

搜帧模块的使能输出,不用接板子 |

| 13 |

o_peak_dout |

搜帧模块的数据输出,接板子上的测试脚或者signaltapII上 |

| 14 |

o_enable2 |

最后串并转化的使能,不用接板子 |

| 15 |

o_voice_dout |

最后串并转化的数据输出,接板子上的测试脚或者signaltapII上 |

2.部分程序

clc;

clear;

close all;

warning off;

addpath(genpath(pwd));

N = 40000;

x = zeros(N,1);

y = zeros(N,1);

z = zeros(N,1);

x(1) = 0.001;

y(1) = 0.002;

z(1) = 0.02;

for n = 1:N-1

n

y(n+1) = 0.028*x(n) - 0.001*x(n)*z(n) + 0.999*y(n);

x(n+1) = 0.99*x(n) + 0.01*y(n);

z(n+1) = 0.001*x(n)*y(n) + 0.9973333*z(n);

end

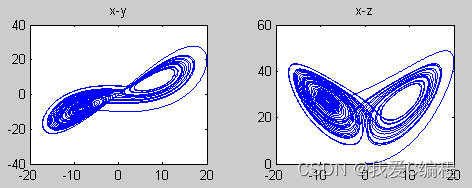

figure;

subplot(221);plot(x,y);title('x-y');

subplot(222);plot(x,z);title('x-z');

subplot(223);plot(y,z);title('y-z');

subplot(224);plot3(x,y,z);title('x-y-z');

figure;

subplot(311);plot(x);title('x');

subplot(312);plot(y);title('y');

subplot(313);plot(z);title('z');//`timescale 1 ns/ 100 ps

module Decryption_complete_system(

i_clk,

i_rst,

i_rec_signal,

o_dout,

o_dout_sign,

o_peak,

o_peak_enable,

o_peak_dout,

o_enable2,

o_voice_dout

);

input i_clk;

input i_rst;

input signed[31:0] i_rec_signal;

output signed[31:0]o_dout;

output o_dout_sign;

output[6:0] o_peak;

output o_peak_dout;

output o_peak_enable;

output o_enable2;

output[15:0] o_voice_dout;

wire signed[31:0]xn;

wire signed[31:0]yn;

wire signed[31:0]zn;

Lorenz2 Lorenz2_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_yn (i_rec_signal),

.o_xn (xn),

.o_yn (yn),

.o_zn (zn)

);

Decryption Decryption_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_din (i_rec_signal),

.i_yn (yn),

.o_signal(o_dout)

);

reg o_dout_sign;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

o_dout_sign <= 1'b0;

end

else begin

if(o_dout < 32'h0000_00ff)

o_dout_sign <= 1'b0;

else

o_dout_sign <= 1'b1;

end

end

find_frame find_frame_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_din (o_dout_sign),

.o_peak (o_peak),

.o_dout (o_peak_dout),

.o_enable(o_peak_enable)

);

s2p s2p_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_enable (o_peak_enable),

.i_serial_din (o_peak_dout),

.o_enable (o_enable2),

.o_voice_dout (o_voice_dout)

);

endmodule //`timescale 1 ns/ 100 ps

module Encryption_complete_system(

i_clk,

i_rst,

i_enable,//the enable of signal

i_voice, //the signal

o_enable,//the enable of p2s

o_serial_dout,//the serial data of signal

o_serial_frame,

o_T_signal//the data of Encryption

);

input i_clk;

input i_rst;

input i_enable;

input[15:0] i_voice;

output o_enable;

output o_serial_dout;

output o_serial_frame;

output signed[31:0]o_T_signal;

//change the parallel data to serial data

p2s p2s_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_enable (i_enable),

.i_voice (i_voice),

.o_enable (o_enable),

.o_serial_dout(o_serial_dout)

);

add_frame add_frame_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_din (o_serial_dout),

.i_enable (o_enable),

.o_dout (o_serial_frame),

.o_enable ()

);

wire signed[31:0]xn;

wire signed[31:0]yn;

wire signed[31:0]zn;

Lorenz Lorenz_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_yn (o_T_signal),

.o_xn (xn),

.o_yn (yn),

.o_zn (zn)

);

Encryption Encryption_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_din (o_serial_frame),

.i_yn (yn),

.o_signal (o_T_signal)

);

endmodule 3.部分仿真图预览

4.源码获取方式

获得方式1:

点击下载链接:

m基于Lorenz混沌自同步的混沌数字保密通信系统的FPGA实现,verilog编程实现,带MATLAB混沌程序+程序操作视频

获取方式2:

博客资源项,搜索和博文同名资源。

获取方式3:

如果下载链接失效,加博主微信联系。

01_053_m