【原创】科研训练指导手册(DE2-115_labs_vhdl)-PART8--附录

附录 DE2-115实验板引脚配置信息

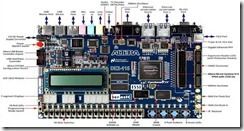

DE2-115开发板:目标芯片Cyclone IV E EP4CE115F29C7;存储器:64MB x2 SDRAM、2MB SRAM、8MB Flash;通信端口:10/100/1000以太网口 x2、USB 2.0时钟:50MHz x3 振荡器、SMA in/out Altera 串行配置芯片– EPCS64

表 1 拨动开关引脚配置

| Signal Name |

FPGA Pin No. |

Description |

I/O Standard |

| SW[0] |

PIN_AB28 |

Slide Switch[0] |

Depending on JP7 |

| SW[1] |

PIN_AC28 |

Slide Switch[1] |

Depending on JP7 |

| SW[2] |

PIN_AC27 |

Slide Switch[2] |

Depending on JP7 |

| SW[3] |

PIN_AD27 |

Slide Switch[3] |

Depending on JP7 |

| SW[4] |

PIN_AB27 |

Slide Switch[4] |

Depending on JP7 |

| SW[5] |

PIN_AC26 |

Slide Switch[5] |

Depending on JP7 |

| SW[6] |

PIN_AD26 |

Slide Switch[6] |

Depending on JP7 |

| SW[7] |

PIN_AB26 |

Slide Switch[7] |

Depending on JP7 |

| SW[8] |

PIN_AC25 |

Slide Switch[8] |

Depending on JP7 |

| SW[9] |

PIN_AB25 |

Slide Switch[9] |

Depending on JP7 |

| SW[10] |

PIN_AC24 |

Slide Switch[10] |

Depending on JP7 |

| SW[11] |

PIN_AB24 |

Slide Switch[11] |

Depending on JP7 |

| SW[12] |

PIN_AB23 |

Slide Switch[12] |

Depending on JP7 |

| SW[13] |

PIN_AA24 |

Slide Switch[13] |

Depending on JP7 |

| SW[14] |

PIN_AA23 |

Slide Switch[14] |

Depending on JP7 |

| SW[15] |

PIN_AA22 |

Slide Switch[15] |

Depending on JP7 |

| SW[16] |

PIN_Y24 |

Slide Switch[16] |

Depending on JP7 |

| SW[17] |

PIN_Y23 |

Slide Switch[17] |

Depending on JP7 |

表 2 按钮开关引脚配置

| Signal Name |

FPGA Pin No. |

Description |

I/O Standard |

| KEY[0] |

PIN_M23 |

Push-button[0] |

Depending on JP7 |

| KEY[1] |

PIN_M21 |

Push-button[1] |

Depending on JP7 |

| KEY[2] |

PIN_N21 |

Push-button[2] |

Depending on JP7 |

| KEY[3] |

PIN_R24 |

Push-button[3] |

Depending on JP7 |

表 3 LED 引脚配置

| Signal Name |

FPGA Pin No. |

Description |

I/OStandard |

| LEDR[0] |

PIN_G19 |

LED Red[0] |

2.5V |

| LEDR[1] |

PIN_F19 |

LED Red[1] |

2.5V |

| LEDR[2] |

PIN_E19 |

LED Red[2] |

2.5V |

| LEDR[3] |

PIN_F21 |

LED Red[3] |

2.5V |

| LEDR[4] |

PIN_F18 |

LED Red[4] |

2.5V |

| LEDR[5] |

PIN_E18 |

LED Red[5] |

2.5V |

| LEDR[6] |

PIN_J19 |

LED Red[6] |

2.5V |

| LEDR[7] |

PIN_H19 |

LED Red[7] |

2.5V |

| LEDR[8] |

PIN_J17 |

LED Red[8] |

2.5V |

| LEDR[9] |

PIN_G17 |

LED Red[9] |

2.5V |

| LEDR[10] |

PIN_J15 |

LED Red[10] |

2.5V |

| LEDR[11] |

PIN_H16 |

LED Red[11] |

2.5V |

| LEDR[12] |

PIN_J16 |

LED Red[12] |

2.5V |

| LEDR[13] |

PIN_H17 |

LED Red[13] |

2.5V |

| LEDR[14] |

PIN_F15 |

LED Red[14] |

2.5V |

| LEDR[15] |

PIN_G15 |

LED Red[15] |

2.5V |

| LEDR[16] |

PIN_G16 |

LED Red[16] |

2.5V |

| LEDR[17] |

PIN_H15 |

LED Red[17] |

2.5V |

| LEDG[0] |

PIN_E21 |

LED Green[0] |

2.5V |

| LEDG[1] |

PIN_E22 |

LED Green[1] |

2.5V |

| LEDG[2] |

PIN_E25 |

LED Green[2] |

2.5V |

| LEDG[3] |

PIN_E24 |

LED Green[3] |

2.5V |

| LEDG[4] |

PIN_H21 |

LED Green[4] |

2.5V |

| LEDG[5] |

PIN_G20 |

LED Green[5] |

2.5V |

| LEDG[6] |

PIN_G22 |

LED Green[6] |

2.5V |

| LEDG[7] |

PIN_G21 |

LED Green[7] |

2.5V |

| LEDG[8] |

PIN_F17 |

LED Green[8] |

2.5V |

表 4 七段数码管引脚配置

| Signal Name |

FPGA Pin No. |

Description |

I/O Standard |

| HEX0[0] |

PIN_G18 |

Seven Segment Digit 0[0] |

2.5V |

| HEX0[1] |

PIN_F22 |

Seven Segment Digit 0[1] |

2.5V |

| HEX0[2] |

PIN_E17 |

Seven Segment Digit 0[2] |

2.5V |

| HEX0[3] |

PIN_L26 |

Seven Segment Digit 0[3] |

Depending on JP7 |

| HEX0[4] |

PIN_L25 |

Seven Segment Digit 0[4] |

Depending on JP7 |

| HEX0[5] |

PIN_J22 |

Seven Segment Digit 0[5] |

Depending on JP7 |

| HEX0[6] |

PIN_H22 |

Seven Segment Digit 0[6] |

Depending on JP7 |

| HEX1[0] |

PIN_M24 |

Seven Segment Digit 1[0] |

Depending on JP7 |

| HEX1[1] |

PIN_Y22 |

Seven Segment Digit 1[1] |

Depending on JP7 |

| HEX1[2] |

PIN_W21 |

Seven Segment Digit 1[2] |

Depending on JP7 |

| HEX1[3] |

PIN_W22 |

Seven Segment Digit 1[3] |

Depending on JP7 |

| HEX1[4] |

PIN_W25 |

Seven Segment Digit 1[4] |

Depending on JP7 |

| HEX1[5] |

PIN_U23 |

Seven Segment Digit 1[5] |

Depending on JP7 |

| HEX1[6] |

PIN_U24 |

Seven Segment Digit 1[6] |

Depending on JP7 |

| HEX2[0] |

PIN_AA25 |

Seven Segment Digit 2[0] |

Depending on JP7 |

| HEX2[1] |

PIN_AA26 |

Seven Segment Digit 2[1] |

Depending on JP7 |

| HEX2[2] |

PIN_Y25 |

Seven Segment Digit 2[2] |

Depending on JP7 |

| HEX2[3] |

PIN_W26 |

Seven Segment Digit 2[3] |

Depending on JP7 |

| HEX2[4] |

PIN_Y26 |

Seven Segment Digit 2[4] |

Depending on JP7 |

| HEX2[5] |

PIN_W27 |

Seven Segment Digit 2[5] |

Depending on JP7 |

| HEX2[6] |

PIN_W28 |

Seven Segment Digit 2[6] |

Depending on JP7 |

| HEX3[0] |

PIN_V21 |

Seven Segment Digit 3[0] |

Depending on JP7 |

| HEX3[1] |

PIN_U21 |

Seven Segment Digit 3[1] |

Depending on JP7 |

| HEX3[2] |

PIN_AB20 |

Seven Segment Digit 3[2] |

Depending on JP6 |

| HEX3[3] |

PIN_AA21 |

Seven Segment Digit 3[3] |

Depending on JP6 |

| HEX3[4] |

PIN_AD24 |

Seven Segment Digit 3[4] |

Depending on JP6 |

| HEX3[5] |

PIN_AF23 |

Seven Segment Digit 3[5] |

Depending on JP6 |

| HEX3[6] |

PIN_Y19 |

Seven Segment Digit 3[6] |

Depending on JP6 |

| HEX4[0] |

PIN_AB19 |

Seven Segment Digit 4[0] |

Depending on JP6 |

| HEX4[1] |

PIN_AA19 |

Seven Segment Digit 4[1] |

Depending on JP6 |

| HEX4[2] |

PIN_AG21 |

Seven Segment Digit 4[2] |

Depending on JP6 |

| HEX4[3] |

PIN_AH21 |

Seven Segment Digit 4[3] |

Depending on JP6 |

| HEX4[4] |

PIN_AE19 |

Seven Segment Digit 4[4] |

Depending on JP6 |

| HEX4[5] |

PIN_AF19 |

Seven Segment Digit 4[5] |

Depending on JP6 |

| HEX4[6] |

PIN_AE18 |

Seven Segment Digit 4[6] |

Depending on JP6 |

| HEX5[0] |

PIN_AD18 |

Seven Segment Digit 5[0] |

Depending on JP6 |

| HEX5[1] |

PIN_AC18 |

Seven Segment Digit 5[1] |

Depending on JP6 |

| HEX5[2] |

PIN_AB18 |

Seven Segment Digit 5[2] |

Depending on JP6 |

| HEX5[3] |

PIN_AH19 |

Seven Segment Digit 5[3] |

Depending on JP6 |

| HEX5[4] |

PIN_AG19 |

Seven Segment Digit 5[4] |

Depending on JP6 |

| HEX5[5] |

PIN_AF18 |

Seven Segment Digit 5[5] |

Depending on JP6 |

| HEX5[6] |

PIN_AH18 |

Seven Segment Digit 5[6] |

Depending on JP6 |

| HEX6[0] |

PIN_AA17 |

Seven Segment Digit 6[0] |

Depending on JP6 |

| HEX6[1] |

PIN_AB16 |

Seven Segment Digit 6[1] |

Depending on JP6 |

| HEX6[2] |

PIN_AA16 |

Seven Segment Digit 6[2] |

Depending on JP6 |

| HEX6[3] |

PIN_AB17 |

Seven Segment Digit 6[3] |

Depending on JP6 |

| HEX6[4] |

PIN_AB15 |

Seven Segment Digit 6[4] |

Depending on JP6 |

| HEX6[5] |

PIN_AA15 |

Seven Segment Digit 6[5] |

Depending on JP6 |

| HEX6[6] |

PIN_AC17 |

Seven Segment Digit 6[6] |

Depending on JP6 |

| HEX7[0] |

PIN_AD17 |

Seven Segment Digit 7[0] |

Depending on JP6 |

| HEX7[1] |

PIN_AE17 |

Seven Segment Digit 7[1] |

Depending on JP6 |

| HEX7[2] |

PIN_AG17 |

Seven Segment Digit 7[2] |

Depending on JP6 |

| HEX7[3] |

PIN_AH17 |

Seven Segment Digit 7[3] |

Depending on JP6 |

| HEX7[4] |

PIN_AF17 |

Seven Segment Digit 7[4] |

Depending on JP6 |

| HEX7[5] |

PIN_AG18 |

Seven Segment Digit 7[5] |

Depending on JP6 |

| HEX7[6] |

PIN_AA14 |

Seven Segment Digit 7[6] |

3.3V |

表 5 时钟信号引脚配置信息

| Signal Name |

FPGA Pin No. |

Description |

I/O Standard |

| CLOCK_50 |

PIN_Y2 |

50 MHz clock input |

3.3V |

| CLOCK2_50 |

PIN_AG14 |

50 MHz clock input |

3.3V |

| CLOCK3_50 |

PIN_AG15 |

50 MHz clock input |

Depending on JP6 |

| SMA_CLKOUT |

PIN_AE23 |

External (SMA) clock output |

Depending on JP6 |

| SMA_CLKIN |

PIN_AH14 |

External (SMA) clock input |

3.3V |

表 6 LCD 模块引脚配置

| Signal Name |

FPGAPinNo. |

Description |

I/O |

| LCD_DATA[7] |

PIN_M5 |

LCD Data[7] |

Standard |

| LCD_DATA[6] |

PIN_M3 |

LCD Data[6] |

3.3V |

| LCD_DATA[5] |

PIN_K2 |

LCD Data[5] |

3.3V |

| LCD_DATA[4] |

PIN_K1 |

LCD Data[4] |

3.3V |

| LCD_DATA[3] |

PIN_K7 |

LCD Data[3] |

3.3V |

| LCD_DATA[2] |

PIN_L2 |

LCD Data[2] |

3.3V |

| LCD_DATA[1] |

PIN_L1 |

LCD Data[1] |

3.3V |

| LCD_DATA[0] |

PIN_L3 |

LCD Data[0] |

3.3V |

| LCD_EN |

PIN_L4 |

LCD Enable |

3.3V |

| LCD_RW |

PIN_M1 |

LCD Read/Write Select, 0 = Write, 1 = Read |

3.3V |

| LCD_RS |

PIN_M2 |

LCD Command/Data Select, 0 = Command, 1 = Data |

3.3V |

| LCD_ON |

PIN_L5 |

LCD Power ON/OFF |

3.3V |

| LCD_BLON |

PIN_L6 |

LCD Back Light ON/OFF |

3.3V |

表 7 HSMC 接口引脚配置

| Signal Name |

FPGA Pin No. |

Description |

I/O Standard |

| HSMC_CLKIN0 |

PIN_AH15 |

Dedicated clock input |

Depending on JP6 |

| HSMC_CLKIN_N1 |

PIN_J28 |

LVDS RX or CMOS I/O or differential clock input |

Depending on JP7 |

| HSMC_CLKIN_N2 |

PIN_Y28 |

LVDS RX or CMOS I/O or differential clock input |

Depending on JP7 |

| HSMC_CLKIN_P1 |

PIN_J27 |

LVDS RX or CMOS I/O or differential clock input |

Depending on JP7 |

| HSMC_CLKIN_P2 |

PIN_Y27 |

LVDS RX or CMOS I/O or differential clock input |

Depending on JP7 |

| HSMC_CLKOUT0 |

PIN_AD28 |

Dedicated clock output |

Depending on JP7 |

| HSMC_CLKOUT_N1 |

PIN_G24 |

LVDS TX or CMOS I/O or differential clock input/output |

Depending on JP7 |

| HSMC_CLKOUT_N2 |

PIN_V24 |

LVDS TX or CMOS I/O or differential clock input/output |

Depending on JP7 |

| HSMC_CLKOUT_P1 |

PIN_G23 |

LVDS TX or CMOS I/O or differential clock input/output |

Depending on JP7 |

| HSMC_CLKOUT_P2 |

PIN_V23 |

LVDS TX or CMOS I/O or differential clock input/output |

Depending on JP7 |

| HSMC_D[0] |

PIN_AE26 |

LVDS TX or CMOS I/O |

Depending on JP7 |

| HSMC_D[1] |

PIN_AE28 |

LVDS TX or CMOS I/O |

Depending on JP7 |

| HSMC_D[2] |

PIN_AE27 |

LVDS TX or CMOS I/O |

Depending on JP7 |

| HSMC_D[3] |

PIN_AF27 |

LVDS TX or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_N[0] |

PIN_F25 |

LVDS RX bit 0n or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_N[1] |

PIN_C27 |

LVDS RX bit 1n or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_N[2] |

PIN_E26 |

LVDS RX bit 2n or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_N[3] |

PIN_G26 |

LVDS RX bit 3n or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_N[4] |

PIN_H26 |

LVDS RX bit 4n or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_N[5] |

PIN_K26 |

LVDS RX bit 5n or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_N[6] |

PIN_L24 |

LVDS RX bit 6n or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_N[7] |

PIN_M26 |

LVDS RX bit 7n or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_N[8] |

PIN_R26 |

LVDS RX bit 8n or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_N[9] |

PIN_T26 |

LVDS RX bit 9n or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_N[10] |

PIN_U26 |

LVDS RX bit 10n or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_N[11] |

PIN_L22 |

LVDS RX bit 11n or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_N[12] |

PIN_N26 |

LVDS RX bit 12n or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_N[13] |

PIN_P26 |

LVDS RX bit 13n or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_N[14] |

PIN_R21 |

LVDS RX bit 14n or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_N[15] |

PIN_R23 |

LVDS RX bit 15n or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_N[16] |

PIN_T22 |

LVDS RX bit 16n or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_P[0] |

PIN_F24 |

LVDS RX bit 0 or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_P[1] |

PIN_D26 |

LVDS RX bit 1 or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_P[2] |

PIN_F26 |

LVDS RX bit 2 or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_P[3] |

PIN_G25 |

LVDS RX bit 3 or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_P[4] |

PIN_H25 |

LVDS RX bit 4 or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_P[5] |

PIN_K25 |

LVDS RX bit 5 or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_P[6] |

PIN_L23 |

LVDS RX bit 6 or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_P[7] |

PIN_M25 |

LVDS RX bit 7 or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_P[8] |

PIN_R25 |

LVDS RX bit 8 or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_P[9] |

PIN_T25 |

LVDS RX bit 9 or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_P[10] |

PIN_U25 |

LVDS RX bit 10 or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_P[11] |

PIN_L21 |

LVDS RX bit 11 or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_P[12] |

PIN_N25 |

LVDS RX bit 12 or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_P[13] |

PIN_P25 |

LVDS RX bit 13 or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_P[14] |

PIN_P21 |

LVDS RX bit 14 or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_P[15] |

PIN_R22 |

LVDS RX bit 15 or CMOS I/O |

Depending on JP7 |

| HSMC_RX_D_P[16] |

PIN_T21 |

LVDS RX bit 16 or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_N[0] |

PIN_D28 |

LVDS TX bit 0n or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_N[1] |

PIN_E28 |

LVDS TX bit 1n or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_N[2] |

PIN_F28 |

LVDS TX bit 2n or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_N[3] |

PIN_G28 |

LVDS TX bit 3n or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_N[4] |

PIN_K28 |

LVDS TX bit 4n or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_N[5] |

PIN_M28 |

LVDS TX bit 5n or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_N[6] |

PIN_K22 |

LVDS TX bit 6n or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_N[7] |

PIN_H24 |

LVDS TX bit 7n or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_N[8] |

PIN_J24 |

LVDS TX bit 8n or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_N[9] |

PIN_P28 |

LVDS TX bit 9n or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_N[10] |

PIN_J26 |

LVDS TX bit 10n or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_N[11] |

PIN_L28 |

LVDS TX bit 11n or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_N[12] |

PIN_V26 |

LVDS TX bit 12n or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_N[13] |

PIN_R28 |

LVDS TX bit 13n or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_N[14] |

PIN_U28 |

LVDS TX bit 14n or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_N[15] |

PIN_V28 |

LVDS TX bit 15n or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_N[16] |

PIN_V22 |

LVDS TX bit 16n or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_P[0] |

PIN_D27 |

LVDS TX bit 0 or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_P[1] |

PIN_E27 |

LVDS TX bit 1 or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_P[2] |

PIN_F27 |

LVDS TX bit 2 or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_P[3] |

PIN_G27 |

LVDS TX bit 3 or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_P[4] |

PIN_K27 |

LVDS TX bit 4 or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_P[5] |

PIN_M27 |

LVDS TX bit 5 or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_P[6] |

PIN_K21 |

LVDS TX bit 6 or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_P[7] |

PIN_H23 |

LVDS TX bit 7 or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_P[8] |

PIN_J23 |

LVDS TX bit 8 or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_P[9] |

PIN_P27 |

LVDS TX bit 9 or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_P[10] |

PIN_J25 |

LVDS TX bit 10 or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_P[11] |

PIN_L27 |

LVDS TX bit 11 or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_P[12] |

PIN_V25 |

LVDS TX bit 12 or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_P[13] |

PIN_R27 |

LVDS TX bit 13 or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_P[14] |

PIN_U27 |

LVDS TX bit 14 or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_P[15] |

PIN_V27 |

LVDS TX bit 15 or CMOS I/O |

Depending on JP7 |

| HSMC_TX_D_P[16] |

PIN_U22 |

LVDS TX bit 16 or CMOS I/O |

Depending on JP7 |

表 8 GPIO 引脚配置信息

| Signal Name |

FPGA Pin No. |

Description |

I/O Standard |

| GPIO[0] |

PIN_AB22 |

GPIO Connection DATA[0] |

Depending on JP6 |

| GPIO[1] |

PIN_AC15 |

GPIO Connection DATA[1] |

Depending on JP6 |

| GPIO[2] |

PIN_AB21 |

GPIO Connection DATA[2] |

Depending on JP6 |

| GPIO[3] |

PIN_Y17 |

GPIO Connection DATA[3] |

Depending on JP6 |

| GPIO[4] |

PIN_AC21 |

GPIO Connection DATA[4] |

Depending on JP6 |

| GPIO[5] |

PIN_Y16 |

GPIO Connection DATA[5] |

Depending on JP6 |

| GPIO[6] |

PIN_AD21 |

GPIO Connection DATA[6] |

Depending on JP6 |

| GPIO[7] |

PIN_AE16 |

GPIO Connection DATA[7] |

Depending on JP6 |

| GPIO[8] |

PIN_AD15 |

GPIO Connection DATA[8] |

Depending on JP6 |

| GPIO[9] |

PIN_AE15 |

GPIO Connection DATA[9] |

Depending on JP6 |

| GPIO[10] |

PIN_AC19 |

GPIO Connection DATA[10] |

Depending on JP6 |

| GPIO[11] |

PIN_AF16 |

GPIO Connection DATA[11] |

Depending on JP6 |

| GPIO[12] |

PIN_AD19 |

GPIO Connection DATA[12] |

Depending on JP6 |

| GPIO[13] |

PIN_AF15 |

GPIO Connection DATA[13] |

Depending on JP6 |

| GPIO[14] |

PIN_AF24 |

GPIO Connection DATA[14] |

Depending on JP6 |

| GPIO[15] |

PIN_AE21 |

GPIO Connection DATA[15] |

Depending on JP6 |

| GPIO[16] |

PIN_AF25 |

GPIO Connection DATA[16] |

Depending on JP6 |

| GPIO[17] |

PIN_AC22 |

GPIO Connection DATA[17] |

Depending on JP6 |

| GPIO[18] |

PIN_AE22 |

GPIO Connection DATA[18] |

Depending on JP6 |

| GPIO[19] |

PIN_AF21 |

GPIO Connection DATA[19] |

Depending on JP6 |

| GPIO[20] |

PIN_AF22 |

GPIO Connection DATA[20] |

Depending on JP6 |

| GPIO[21] |

PIN_AD22 |

GPIO Connection DATA[21] |

Depending on JP6 |

| GPIO[22] |

PIN_AG25 |

GPIO Connection DATA[22] |

Depending on JP6 |

| GPIO[23] |

PIN_AD25 |

GPIO Connection DATA[23] |

Depending on JP6 |

| GPIO[24] |

PIN_AH25 |

GPIO Connection DATA[24] |

Depending on JP6 |

| GPIO[25] |

PIN_AE25 |

GPIO Connection DATA[25] |

Depending on JP6 |

| GPIO[26] |

PIN_AG22 |

GPIO Connection DATA[26] |

Depending on JP6 |

| GPIO[27] |

PIN_AE24 |

GPIO Connection DATA[27] |

Depending on JP6 |

| GPIO[28] |

PIN_AH22 |

GPIO Connection DATA[28] |

Depending on JP6 |

| GPIO[29] |

PIN_AF26 |

GPIO Connection DATA[29] |

Depending on JP6 |

| GPIO[30] |

PIN_AE20 |

GPIO Connection DATA[30] |

Depending on JP6 |

| GPIO[31] |

PIN_AG23 |

GPIO Connection DATA[31] |

Depending on JP6 |

| GPIO[32] |

PIN_AF20 |

GPIO Connection DATA[32] |

Depending on JP6 |

| GPIO[33] |

PIN_AH26 |

GPIO Connection DATA[33] |

Depending on JP6 |

| GPIO[34] |

PIN_AH23 |

GPIO Connection DATA[34] |

Depending on JP6 |

| GPIO[35] |

PIN_AG26 |

GPIO Connection DATA[35] |

Depending on JP6 |

表 9 扩展接口引脚配置信息

| Signal Name |

FPGA Pin No. |

Description |

I/O Standard |

| EX_IO[0] |

PIN_J10 |

Extended IO[0] |

3.3V |

| EX_IO[1] |

PIN_J14 |

Extended IO[1] |

3.3V |

| EX_IO[2] |

PIN_H13 |

Extended IO[2] |

3.3V |

| EX_IO[3] |

PIN_H14 |

Extended IO[3] |

3.3V |

| EX_IO[4] |

PIN_F14 |

Extended IO[4] |

3.3V |

| EX_IO[5] |

PIN_E10 |

Extended IO[5] |

3.3V |

| EX_IO[6] |

PIN_D9 |

Extended IO[6] |

3.3V |

表 10 ADV7123 引脚配置

| Signal Name |

FPGA Pin No. |

Description |

I/O Standard |

| VGA_R[0] |

PIN_E12 |

VGA Red[0] |

3.3V |

| VGA_R[1] |

PIN_E11 |

VGA Red[1] |

3.3V |

| VGA_R[2] |

PIN_D10 |

VGA Red[2] |

3.3V |

| VGA_R[3] |

PIN_F12 |

VGA Red[3] |

3.3V |

| VGA_R[4] |

PIN_G10 |

VGA Red[4] |

3.3V |

| VGA_R[5] |

PIN_J12 |

VGA Red[5] |

3.3V |

| VGA_R[6] |

PIN_H8 |

VGA Red[6] |

3.3V |

| VGA_R[7] |

PIN_H10 |

VGA Red[7] |

3.3V |

| VGA_G[0] |

PIN_G8 |

VGA Green[0] |

3.3V |

| VGA_G[1] |

PIN_G11 |

VGA Green[1] |

3.3V |

| VGA_G[2] |

PIN_F8 |

VGA Green[2] |

3.3V |

| VGA_G[3] |

PIN_H12 |

VGA Green[3] |

3.3V |

| VGA_G[4] |

PIN_C8 |

VGA Green[4] |

3.3V |

| VGA_G[5] |

PIN_B8 |

VGA Green[5] |

3.3V |

| VGA_G[6] |

PIN_F10 |

VGA Green[6] |

3.3V |

| VGA_G[7] |

PIN_C9 |

VGA Green[7] |

3.3V |

| VGA_B[0] |

PIN_B10 |

VGA Blue[0] |

3.3V |

| VGA_B[1] |

PIN_A10 |

VGA Blue[1] |

3.3V |

| VGA_B[2] |

PIN_C11 |

VGA Blue[2] |

3.3V |

| VGA_B[3] |

PIN_B11 |

VGA Blue[3] |

3.3V |

| VGA_B[4] |

PIN_A11 |

VGA Blue[4] |

3.3V |

| VGA_B[5] |

PIN_C12 |

VGA Blue[5] |

3.3V |

| VGA_B[6] |

PIN_D11 |

VGA Blue[6] |

3.3V |

| VGA_B[7] |

PIN_D12 |

VGA Blue[7] |

3.3V |

| VGA_CLK |

PIN_A12 |

VGA Clock |

3.3V |

| VGA_BLANK_N |

PIN_F11 |

VGA BLANK |

3.3V |

| VGA_HS |

PIN_G13 |

VGA H_SYNC |

3.3V |

| VGA_VS |

PIN_C13 |

VGA V_SYNC |

3.3V |

| VGA_SYNC_N |

PIN_C10 |

VGA SYNC |

3.3V |

表 11 音频编解码芯片引脚配置

| Signal Name |

FPGA Pin No. |

Description |

I/O Standard |

| AUD_ADCLRCK |

PIN_C2 |

Audio CODEC ADC LR Clock |

3.3V |

| AUD_ADCDAT |

PIN_D2 |

Audio CODEC ADC Data |

3.3V |

| AUD_DACLRCK |

PIN_E3 |

Audio CODEC DAC LR Clock |

3.3V |

| AUD_DACDAT |

PIN_D1 |

Audio CODEC DAC Data |

3.3V |

| AUD_XCK |

PIN_E1 |

Audio CODEC Chip Clock |

3.3V |

| AUD_BCLK |

PIN_F2 |

Audio CODEC Bit-Stream Clock |

3.3V |

| I2C_SCLK |

PIN_B7 |

I2C Clock |

3.3V |

| I2C_SDAT |

PIN_A8 |

I2C Data |

3.3V |

表 12 RS-232 引脚配置

| Signal Name |

FPGA Pin No. |

Description |

I/O Standard |

| UART_RXD |

PIN_G12 |

UART Receiver |

3.3V |

| UART_TXD |

PIN_G9 |

UART Transmitter |

3.3V |

| UART_CTS |

PIN_G14 |

UART Clear to Send |

3.3V |

| UART_RTS |

PIN_J13 |

UART Request to Send |

3.3V |

表 13 PS/2 引脚配置

| Signal Name |

FPGA Pin No. |

Description |

I/O Standard |

| PS2_CLK |

PIN_G6 |

PS/2 Clock |

3.3V |

| PS2_DAT |

PIN_H5 |

PS/2 Data |

3.3V |

| PS2_CLK2 |

PIN_G5 |

PS/2 Clock (reserved for second PS/2 device) |

3.3V |

| PS2_DAT2 |

PIN_F5 |

PS/2 Data (reserved for second PS/2 device) |

3.3V |

表 14 千兆以太网芯片引脚配置

| Signal Name |

FPGA Pin No. |

Description |

I/O Standard |

| ENET0_GTX_CLK |

PIN_A17 |

GMII Transmit Clock 1 |

2.5V |

| ENET0_INT_N |

PIN_A21 |

Interrupt open drain output 1 |

2.5V |

| ENET0_LINK100 |

PIN_C14 |

Parallel LED output of 100BASE-TX link 1 |

3.3V |

| ENET0_MDC |

PIN_C20 |

Management data clock reference 1 |

2.5V |

| ENET0_MDIO |

PIN_B21 |

Management data 1 |

2.5V |

| ENET0_RST_N |

PIN_C19 |

Hardware reset signal 1 |

2.5V |

| ENET0_RX_CLK |

PIN_A15 |

GMII and MII receive clock 1 |

2.5V |

| ENET0_RX_COL |

PIN_E15 |

GMII and MII collision 1 |

2.5V |

| ENET0_RX_CRS |

PIN_D15 |

GMII and MII carrier sense 1 |

2.5V |

| ENET0_RX_DATA[0] |

PIN_C16 |

GMII and MII receive data[0] 1 |

2.5V |

| ENET0_RX_DATA[1] |

PIN_D16 |

GMII and MII receive data[1] 1 |

2.5V |

| ENET0_RX_DATA[2] |

PIN_D17 |

GMII and MII receive data[2] 1 |

2.5V |

| ENET0_RX_DATA[3] |

PIN_C15 |

GMII and MII receive data[3] 1 |

2.5V |

| ENET0_RX_DV |

PIN_C17 |

GMII and MII receive data valid 1 |

2.5V |

| ENET0_RX_ER |

PIN_D18 |

GMII and MII receive error 1 |

2.5V |

| ENET0_TX_CLK |

PIN_B17 |

MII transmit clock 1 |

2.5V |

| ENET0_TX_DATA[0] |

PIN_C18 |

MII transmit data[0] 1 |

2.5V |

| ENET0_TX_DATA[1] |

PIN_D19 |

MII transmit data[1] 1 |

2.5V |

| ENET0_TX_DATA[2] |

PIN_A19 |

MII transmit data[2] 1 |

2.5V |

| ENET0_TX_DATA[3] |

PIN_B19 |

MII transmit data[3] 1 |

2.5V |

| ENET0_TX_EN |

PIN_A18 |

GMII and MII transmit enable 1 |

2.5V |

| ENET0_TX_ER |

PIN_B18 |

GMII and MII transmit error 1 |

2.5V |

| ENET1_GTX_CLK |

PIN_C23 |

GMII Transmit Clock 2 |

2.5V |

| ENET1_INT_N |

PIN_D24 |

Interrupt open drain output 2 |

2.5V |

| ENET1_LINK100 |

PIN_D13 |

Parallel LED output of 100BASE-TX link 2 |

2.5V |

| ENET1_MDC |

PIN_D23 |

Management data clock reference 2 |

2.5V |

| ENET1_MDIO |

PIN_D25 |

Management data 2 |

2.5V |

| ENET1_RST_N |

PIN_D22 |

Hardware reset signal 2 |

2.5V |

| ENET1_RX_CLK |

PIN_B15 |

GMII and MII receive clock 2 |

2.5V |

| ENET1_RX_COL |

PIN_B22 |

GMII and MII collision 2 |

2.5V |

| ENET1_RX_CRS |

PIN_D20 |

GMII and MII carrier sense 2 |

2.5V |

| ENET1_RX_DATA[0] |

PIN_B23 |

GMII and MII receive data[0] 2 |

2.5V |

| ENET1_RX_DATA[1] |

PIN_C21 |

GMII and MII receive data[1] 2 |

2.5V |

| ENET1_RX_DATA[2] |

PIN_A23 |

GMII and MII receive data[2] 2 |

2.5V |

| ENET1_RX_DATA[3] |

PIN_D21 |

GMII and MII receive data[3] 2 |

2.5V |

| ENET1_RX_DV |

PIN_A22 |

GMII and MII receive data valid 2 |

2.5V |

| ENET1_RX_ER |

PIN_C24 |

GMII and MII receive error 2 |

2.5V |

| ENET1_TX_CLK |

PIN_C22 |

MII transmit clock 2 |

2.5V |

| ENET1_TX_DATA[0] |

PIN_C25 |

MII transmit data[0] 2 |

2.5V |

| ENET1_TX_DATA[1] |

PIN_A26 |

MII transmit data[1] 2 |

2.5V |

| ENET1_TX_DATA[2] |

PIN_B26 |

MII transmit data[2] 2 |

2.5V |

| ENET1_TX_DATA[3] |

PIN_C26 |

MII transmit data[3] 2 |

2.5V |

| ENET1_TX_EN |

PIN_B25 |

GMII and MII transmit enable 2 |

2.5V |

| ENET1_TX_ER |

PIN_A25 |

GMII and MII transmit error 2 |

2.5V |

| ENETCLK_25 |

PIN_A14 |

Ethernet clock source |

3.3V |

表 15 TV 解码芯片引脚配置

| Signal Name |

FPGA Pin No. |

Description |

I/O Standard |

| TD_ DATA [0] |

PIN_E8 |

TV Decoder Data[0] |

3.3V |

| TD_ DATA [1] |

PIN_A7 |

TV Decoder Data[1] |

3.3V |

| TD_ DATA [2] |

PIN_D8 |

TV Decoder Data[2] |

3.3V |

| TD_ DATA [3] |

PIN_C7 |

TV Decoder Data[3] |

3.3V |

| TD_ DATA [4] |

PIN_D7 |

TV Decoder Data[4] |

3.3V |

| TD_ DATA [5] |

PIN_D6 |

TV Decoder Data[5] |

3.3V |

| TD_ DATA [6] |

PIN_E7 |

TV Decoder Data[6] |

3.3V |

| TD_ DATA [7] |

PIN_F7 |

TV Decoder Data[7] |

3.3V |

| TD_HS |

PIN_E5 |

TV Decoder H_SYNC |

3.3V |

| TD_VS |

PIN_E4 |

TV Decoder V_SYNC |

3.3V |

| TD_CLK27 |

PIN_B14 |

TV Decoder Clock Input. |

3.3V |

| TD_RESET_N |

PIN_G7 |

TV Decoder Reset |

3.3V |

| I2C_SCLK |

PIN_B7 |

I2C Clock |

3.3V |

| I2C_SDAT |

PIN_A8 |

I2C Data |

3.3V |

表 16 USB (ISP1362)引脚配置

| Signal Name |

FPGA Pin No. |

Description |

I/O Standard |

| OTG_ADDR[0] |

PIN_H7 |

ISP1362 Address[0] |

3.3V |

| OTG_ADDR[1] |

PIN_C3 |

ISP1362 Address[1] |

3.3V |

| OTG_DATA[0] |

PIN_J6 |

ISP1362 Data[0] |

3.3V |

| OTG_DATA[1] |

PIN_K4 |

ISP1362 Data[1] |

3.3V |

| OTG_DATA[2] |

PIN_J5 |

ISP1362 Data[2] |

3.3V |

| OTG_DATA[3] |

PIN_K3 |

ISP1362 Data[3] |

3.3V |

| OTG_DATA[4] |

PIN_J4 |

ISP1362 Data[4] |

3.3V |

| OTG_DATA[5] |

PIN_J3 |

ISP1362 Data[5] |

3.3V |

| OTG_DATA[6] |

PIN_J7 |

ISP1362 Data[6] |

3.3V |

| OTG_DATA[7] |

PIN_H6 |

ISP1362 Data[7] |

3.3V |

| OTG_DATA[8] |

PIN_H3 |

ISP1362 Data[8] |

3.3V |

| OTG_DATA[9] |

PIN_H4 |

ISP1362 Data[9] |

3.3V |

| OTG_DATA[10] |

PIN_G1 |

ISP1362 Data[10] |

3.3V |

| OTG_DATA[11] |

PIN_G2 |

ISP1362 Data[11] |

3.3V |

| OTG_DATA[12] |

PIN_G3 |

ISP1362 Data[12] |

3.3V |

| OTG_DATA[13] |

PIN_F1 |

ISP1362 Data[13] |

3.3V |

| OTG_DATA[14] |

PIN_F3 |

ISP1362 Data[14] |

3.3V |

| OTG_DATA[15] |

PIN_G4 |

ISP1362 Data[15] |

3.3V |

| OTG_CS_N |

PIN_A3 |

ISP1362 Chip Select |

3.3V |

| OTG_RD_N |

PIN_B3 |

ISP1362 Read |

3.3V |

| OTG_WR_N |

PIN_A4 |

ISP1362 Write |

3.3V |

| OTG_RST_N |

PIN_C5 |

ISP1362 Reset |

3.3V |

| OTG_INT[0] |

PIN_A6 |

ISP1362 Interrupt 0 |

3.3V |

| OTG_INT[1] |

PIN_D5 |

ISP1362 Interrupt 1 |

3.3V |

| OTG_DACK_N[0] |

PIN_C4 |

ISP1362 DMA Acknowledge 0 |

3.3V |

| OTG_DACK_N[1] |

PIN_D4 |

ISP1362 DMA Acknowledge 1 |

3.3V |

| OTG_DREQ[0] |

PIN_J1 |

ISP1362 DMA Request 0 |

3.3V |

| OTG_DREQ[1] |

PIN_B4 |

ISP1362 DMA Request 1 |

3.3V |

| OTG_FSPEED |

PIN_C6 |

USB Full Speed, 0 = Enable, Z = Disable |

3.3V |

| OTG_LSPEED |

PIN_B6 |

USB Low Speed, 0 = Enable, Z = Disable |

3.3V |

表 17 IR 引脚配置

| Signal Name |

FPGA Pin No. |

Description |

I/O Standard |

| IRDA_RXD |

PIN_Y15 |

IR Receiver |

3.3V |

表 18 SRAM 引脚配置

| Signal Name |

FPGA Pin No. |

Description |

I/O Standard |

| SRAM_ADDR[0] |

PIN_AB7 |

SRAM Address[0] |

3.3V |

| SRAM_ADDR[1] |

PIN_AD7 |

SRAM Address[1] |

3.3V |

| SRAM_ADDR[2] |

PIN_AE7 |

SRAM Address[2] |

3.3V |

| SRAM_ADDR[3] |

PIN_AC7 |

SRAM Address[3] |

3.3V |

| SRAM_ADDR[4] |

PIN_AB6 |

SRAM Address[4] |

3.3V |

| SRAM_ADDR[5] |

PIN_AE6 |

SRAM Address[5] |

3.3V |

| SRAM_ADDR[6] |

PIN_AB5 |

SRAM Address[6] |

3.3V |

| SRAM_ADDR[7] |

PIN_AC5 |

SRAM Address[7] |

3.3V |

| SRAM_ADDR[8] |

PIN_AF5 |

SRAM Address[8] |

3.3V |

| SRAM_ADDR[9] |

PIN_T7 |

SRAM Address[9] |

3.3V |

| SRAM_ADDR[10] |

PIN_AF2 |

SRAM Address[10] |

3.3V |

| SRAM_ADDR[11] |

PIN_AD3 |

SRAM Address[11] |

3.3V |

| SRAM_ADDR[12] |

PIN_AB4 |

SRAM Address[12] |

3.3V |

| SRAM_ADDR[13] |

PIN_AC3 |

SRAM Address[13] |

3.3V |

| SRAM_ADDR[14] |

PIN_AA4 |

SRAM Address[14] |

3.3V |

| SRAM_ADDR[15] |

PIN_AB11 |

SRAM Address[15] |

3.3V |

| SRAM_ADDR[16] |

PIN_AC11 |

SRAM Address[16] |

3.3V |

| SRAM_ADDR[17] |

PIN_AB9 |

SRAM Address[17] |

3.3V |

| SRAM_ADDR[18] |

PIN_AB8 |

SRAM Address[18] |

3.3V |

| SRAM_ADDR[19] |

PIN_T8 |

SRAM Address[19] |

3.3V |

| SRAM_DQ[0] |

PIN_AH3 |

SRAM Data[0] |

3.3V |

| SRAM_DQ[1] |

PIN_AF4 |

SRAM Data[1] |

3.3V |

| SRAM_DQ[2] |

PIN_AG4 |

SRAM Data[2] |

3.3V |

| SRAM_DQ[3] |

PIN_AH4 |

SRAM Data[3] |

3.3V |

| SRAM_DQ[4] |

PIN_AF6 |

SRAM Data[4] |

3.3V |

| SRAM_DQ[5] |

PIN_AG6 |

SRAM Data[5] |

3.3V |

| SRAM_DQ[6] |

PIN_AH6 |

SRAM Data[6] |

3.3V |

| SRAM_DQ[7] |

PIN_AF7 |

SRAM Data[7] |

3.3V |

| SRAM_DQ[8] |

PIN_AD1 |

SRAM Data[8] |

3.3V |

| SRAM_DQ[9] |

PIN_AD2 |

SRAM Data[9] |

3.3V |

| SRAM_DQ[10] |

PIN_AE2 |

SRAM Data[10] |

3.3V |

| SRAM_DQ[11] |

PIN_AE1 |

SRAM Data[11] |

3.3V |

| SRAM_DQ[12] |

PIN_AE3 |

SRAM Data[12] |

3.3V |

| SRAM_DQ[13] |

PIN_AE4 |

SRAM Data[13] |

3.3V |

| SRAM_DQ[14] |

PIN_AF3 |

SRAM Data[14] |

3.3V |

| SRAM_DQ[15] |

PIN_AG3 |

SRAM Data[15] |

3.3V |

| SRAM_OE_N |

PIN_AD5 |

SRAM Output Enable |

|

| SRAM_WE_N |

PIN_AE8 |

SRAM Write Enable |

|

| SRAM_CE_N |

PIN_AF8 |

SRAM Chip Select |

|

| SRAM_LB_N |

PIN_AD4 |

SRAM Lower Byte Strobe |

|

| SRAM_UB_N |

PIN_AC4 |

SRAM Higher Byte Strobe |

表 19 SDRAM 引脚配置

| Signal Name |

FPGA Pin No. |

Description |

I/O Standard |

| DRAM_ADDR[0] |

PIN_R6 |

SDRAM Address[0] |

3.3V |

| DRAM_ADDR[1] |

PIN_V8 |

SDRAM Address[1] |

3.3V |

| DRAM_ADDR[2] |

PIN_U8 |

SDRAM Address[2] |

3.3V |

| DRAM_ADDR[3] |

PIN_P1 |

SDRAM Address[3] |

3.3V |

| DRAM_ADDR[4] |

PIN_V5 |

SDRAM Address[4] |

3.3V |

| DRAM_ADDR[5] |

PIN_W8 |

SDRAM Address[5] |

3.3V |

| DRAM_ADDR[6] |

PIN_W7 |

SDRAM Address[6] |

3.3V |

| DRAM_ADDR[7] |

PIN_AA7 |

SDRAM Address[7] |

3.3V |

| DRAM_ADDR[8] |

PIN_Y5 |

SDRAM Address[8] |

3.3V |

| DRAM_ADDR[9] |

PIN_Y6 |

SDRAM Address[9] |

3.3V |

| DRAM_ADDR[10] |

PIN_R5 |

SDRAM Address[10] |

3.3V |

| DRAM_ADDR[11] |

PIN_AA5 |

SDRAM Address[11] |

3.3V |

| DRAM_ADDR[12] |

PIN_Y7 |

SDRAM Address[12] |

3.3V |

| DRAM_DQ[0] |

PIN_W3 |

SDRAM Data[0] |

3.3V |

| DRAM_DQ[1] |

PIN_W2 |

SDRAM Data[1] |

3.3V |

| DRAM_DQ[2] |

PIN_V4 |

SDRAM Data[2] |

3.3V |

| DRAM_DQ[3] |

PIN_W1 |

SDRAM Data[3] |

3.3V |

| DRAM_DQ[4] |

PIN_V3 |

SDRAM Data[4] |

3.3V |

| DRAM_DQ[5] |

PIN_V2 |

SDRAM Data[5] |

3.3V |

| DRAM_DQ[6] |

PIN_V1 |

SDRAM Data[6] |

3.3V |

| DRAM_DQ[7] |

PIN_U3 |

SDRAM Data[7] |

3.3V |

| DRAM_DQ[8] |

PIN_Y3 |

SDRAM Data[8] |

3.3V |

| DRAM_DQ[9] |

PIN_Y4 |

SDRAM Data[9] |

3.3V |

| DRAM_DQ[10] |

PIN_AB1 |

SDRAM Data[10] |

3.3V |

| DRAM_DQ[11] |

PIN_AA3 |

SDRAM Data[11] |

3.3V |

| DRAM_DQ[12] |

PIN_AB2 |

SDRAM Data[12] |

3.3V |

| DRAM_DQ[13] |

PIN_AC1 |

SDRAM Data[13] |

3.3V |

| DRAM_DQ[14] |

PIN_AB3 |

SDRAM Data[14] |

3.3V |

| DRAM_DQ[15] |

PIN_AC2 |

SDRAM Data[15] |

3.3V |

| SRAM_OE_N |

PIN_AD5 |

SRAM Output Enable |

3.3V |

| SRAM_WE_N |

PIN_AE8 |

SRAM Write Enable |

3.3V |

| SRAM_CE_N |

PIN_AF8 |

SRAM Chip Select |

3.3V |

| SRAM_LB_N |

PIN_AD4 |

SRAM Lower Byte Strobe |

3.3V |

| SRAM_UB_N |

PIN_AC4 |

SRAM Higher Byte Strobe |

3.3V |

表 20 SDRAM 引脚配置

| Signal Name |

FPGA Pin No. |

Description |

I/O Standard |

| DRAM_ADDR[0] |

PIN_R6 |

SDRAM Address[0] |

3.3V |

| DRAM_ADDR[1] |

PIN_V8 |

SDRAM Address[1] |

3.3V |

| DRAM_ADDR[2] |

PIN_U8 |

SDRAM Address[2] |

3.3V |

| DRAM_ADDR[3] |

PIN_P1 |

SDRAM Address[3] |

3.3V |

| DRAM_ADDR[4] |

PIN_V5 |

SDRAM Address[4] |

3.3V |

| DRAM_ADDR[5] |

PIN_W8 |

SDRAM Address[5] |

3.3V |

| DRAM_ADDR[6] |

PIN_W7 |

SDRAM Address[6] |

3.3V |

| DRAM_ADDR[7] |

PIN_AA7 |

SDRAM Address[7] |

3.3V |

| DRAM_ADDR[8] |

PIN_Y5 |

SDRAM Address[8] |

3.3V |

| DRAM_ADDR[9] |

PIN_Y6 |

SDRAM Address[9] |

3.3V |

| DRAM_ADDR[10] |

PIN_R5 |

SDRAM Address[10] |

3.3V |

| DRAM_ADDR[11] |

PIN_AA5 |

SDRAM Address[11] |

3.3V |

| DRAM_ADDR[12] |

PIN_Y7 |

SDRAM Address[12] |

3.3V |

| DRAM_DQ[0] |

PIN_W3 |

SDRAM Data[0] |

3.3V |

| DRAM_DQ[1] |

PIN_W2 |

SDRAM Data[1] |

3.3V |

| DRAM_DQ[2] |

PIN_V4 |

SDRAM Data[2] |

3.3V |

| DRAM_DQ[3] |

PIN_W1 |

SDRAM Data[3] |

3.3V |

| DRAM_DQ[4] |

PIN_V3 |

SDRAM Data[4] |

3.3V |

| DRAM_DQ[5] |

PIN_V2 |

SDRAM Data[5] |

3.3V |

| DRAM_DQ[6] |

PIN_V1 |

SDRAM Data[6] |

3.3V |

| DRAM_DQ[7] |

PIN_U3 |

SDRAM Data[7] |

3.3V |

| DRAM_DQ[8] |

PIN_Y3 |

SDRAM Data[8] |

3.3V |

| DRAM_DQ[9] |

PIN_Y4 |

SDRAM Data[9] |

3.3V |

| DRAM_DQ[10] |

PIN_AB1 |

SDRAM Data[10] |

3.3V |

| DRAM_DQ[11] |

PIN_AA3 |

SDRAM Data[11] |

3.3V |

| DRAM_DQ[12] |

PIN_AB2 |

SDRAM Data[12] |

3.3V |

| DRAM_DQ[13] |

PIN_AC1 |

SDRAM Data[13] |

3.3V |

| DRAM_DQ[14] |

PIN_AB3 |

SDRAM Data[14] |

3.3V |

| DRAM_DQ[15] |

PIN_AC2 |

SDRAM Data[15] |

3.3V |

| DRAM_DQ[16] |

PIN_M8 |

SDRAM Data[16] |

3.3V |

| DRAM_DQ[17] |

PIN_L8 |

SDRAM Data[17] |

3.3V |

| DRAM_DQ[18] |

PIN_P2 |

SDRAM Data[18] |

3.3V |

| DRAM_DQ[19] |

PIN_N3 |

SDRAM Data[19] |

3.3V |

| DRAM_DQ[20] |

PIN_N4 |

SDRAM Data[20] |

3.3V |

| DRAM_DQ[21] |

PIN_M4 |

SDRAM Data[21] |

3.3V |

| DRAM_DQ[22] |

PIN_M7 |

SDRAM Data[22] |

3.3V |

| DRAM_DQ[23] |

PIN_L7 |

SDRAM Data[23] |

3.3V |

| DRAM_DQ[24] |

PIN_U5 |

SDRAM Data[24] |

3.3V |

| DRAM_DQ[25] |

PIN_R7 |

SDRAM Data[25] |

3.3V |

| DRAM_DQ[26] |

PIN_R1 |

SDRAM Data[26] |

3.3V |

| DRAM_DQ[27] |

PIN_R2 |

SDRAM Data[27] |

3.3V |

| DRAM_DQ[28] |

PIN_R3 |

SDRAM Data[28] |

3.3V |

| DRAM_DQ[29] |

PIN_T3 |

SDRAM Data[29] |

3.3V |

| DRAM_DQ[30] |

PIN_U4 |

SDRAM Data[30] |

3.3V |

| DRAM_DQ[31] |

PIN_U1 |

SDRAM Data[31] |

3.3V |

| DRAM_BA[0] |

PIN_U7 |

SDRAM Bank Address[0] |

3.3V |

| DRAM_BA[1] |

PIN_R4 |

SDRAM Bank Address[1] |

3.3V |

| DRAM_DQM[0] |

PIN_U2 |

SDRAM byte Data Mask[0] |

3.3V |

| DRAM_DQM[1] |

PIN_W4 |

SDRAM byte Data Mask[1] |

3.3V |

| DRAM_DQM[2] |

PIN_K8 |

SDRAM byte Data Mask[2] |

3.3V |

| DRAM_DQM[3] |

PIN_N8 |

SDRAM byte Data Mask[3] |

3.3V |

| DRAM_RAS_N |

PIN_U6 |

SDRAM Row Address Strobe |

3.3V |

| DRAM_CAS_N |

PIN_V7 |

SDRAM Column Address Strobe |

3.3V |

| DRAM_CKE |

PIN_AA6 |

SDRAM Clock Enable |

3.3V |

| DRAM_CLK |

PIN_AE5 |

SDRAM Clock |

3.3V |

| DRAM_WE_N |

PIN_V6 |

SDRAM Write Enable |

3.3V |

| DRAM_CS_N |

PIN_T4 |

SDRAM Chip Select |

3.3V |

表 21 Flash 引脚配置

| Signal Name |

FPGA Pin No. |

Description |

I/O Standard |

| FL_ADDR[0] |

PIN_AG12 |

FLASH Address[0] |

3.3V |

| FL_ADDR[1] |

PIN_AH7 |

FLASH Address[1] |

3.3V |

| FL_ADDR[2] |

PIN_Y13 |

FLASH Address[2] |

3.3V |

| FL_ADDR[3] |

PIN_Y14 |

FLASH Address[3] |

3.3V |

| FL_ADDR[4] |

PIN_Y12 |

FLASH Address[4] |

3.3V |

| FL_ADDR[5] |

PIN_AA13 |

FLASH Address[5] |

3.3V |

| FL_ADDR[6] |

PIN_AA12 |

FLASH Address[6] |

3.3V |

| FL_ADDR[7] |

PIN_AB13 |

FLASH Address[7] |

3.3V |

| FL_ADDR[8] |

PIN_AB12 |

FLASH Address[8] |

3.3V |

| FL_ADDR[9] |

PIN_AB10 |

FLASH Address[9] |

3.3V |

| FL_ADDR[10] |

PIN_AE9 |

FLASH Address[10] |

3.3V |

| FL_ADDR[11] |

PIN_AF9 |

FLASH Address[11] |

3.3V |

| FL_ADDR[12] |

PIN_AA10 |

FLASH Address[12] |

3.3V |

| FL_ADDR[13] |

PIN_AD8 |

FLASH Address[13] |

3.3V |

| FL_ADDR[14] |

PIN_AC8 |

FLASH Address[14] |

3.3V |

| FL_ADDR[15] |

PIN_Y10 |

FLASH Address[15] |

3.3V |

| FL_ADDR[16] |

PIN_AA8 |

FLASH Address[16] |

3.3V |

| FL_ADDR[17] |

PIN_AH12 |

FLASH Address[17] |

3.3V |

| FL_ADDR[18] |

PIN_AC12 |

FLASH Address[18] |

3.3V |

| FL_ADDR[19] |

PIN_AD12 |

FLASH Address[19] |

3.3V |

| FL_ADDR[20] |

PIN_AE10 |

FLASH Address[20] |

3.3V |

| FL_ADDR[21] |

PIN_AD10 |

FLASH Address[21] |

3.3V |

| FL_ADDR[22] |

PIN_AD11 |

FLASH Address[22] |

3.3V |

| FL_DQ[0] |

PIN_AH8 |

FLASH Data[0] |

3.3V |

| FL_DQ[1] |

PIN_AF10 |

FLASH Data[1] |

3.3V |

| FL_DQ[2] |

PIN_AG10 |

FLASH Data[2] |

3.3V |

| FL_DQ[3] |

PIN_AH10 |

FLASH Data[3] |

3.3V |

| FL_DQ[4] |

PIN_AF11 |

FLASH Data[4] |

3.3V |

| FL_DQ[5] |

PIN_AG11 |

FLASH Data[5] |

3.3V |

| FL_DQ[6] |

PIN_AH11 |

FLASH Data[6] |

3.3V |

| FL_DQ[7] |

PIN_AF12 |

FLASH Data[7] |

3.3V |

| FL_CE_N |

PIN_AG7 |

FLASH Chip Enable |

3.3V |

| FL_OE_N |

PIN_AG8 |

FLASH Output Enable |

3.3V |

| FL_RST_N |

PIN_AE11 |

FLASH Reset |

3.3V |

| FL_RY |

PIN_Y1 |

FLASH Ready/Busy output |

3.3V |

| FL_WE_N |

PIN_AC10 |

FLASH Write Enable |

3.3V |

| FL_WP_N |

PIN_AE12 |

FLASH Write Protect /Programming Acceleration |

3.3V |

表 22 EEPROM 引脚配置

| Signal Name |

FPGA Pin No. |

Description |

I/O Standard |

| EEP_I2C_SCLK |

PIN_D14 |

EEPROM clock |

3.3V |

| EEP_I2C_SDAT |

PIN_E14 |

EEPROM data |

3.3V |

表 23 SD 卡插槽引脚配置

| Signal Name |

FPGA Pin No. |

Description |

I/O Standard |

| SD_CLK |

PIN_AE13 |

SD Clock |

3.3V |

| SD_CMD |

PIN_AD14 |

SD Command Line |

3.3V |

| SD_DAT[0] |

PIN_AE14 |

SD Data[0] |

3.3V |

| SD_DAT[1] |

PIN_AF13 |

SD Data[1] |

3.3V |

| SD_DAT[2] |

PIN_AB14 |

SD Data[2] |

3.3V |

| SD_DAT[3] |

PIN_AC14 |

SD Data[3] |

3.3V |

| SD_WP_N |

PIN_AF14 |

SD Write Protect |

3.3V |