数字信号处理——CFAR检测器设计(1)

目录

引言

说明

CFAR检测器

1、参数说明

2、检测过程分类

1、仅右窗检测

2、双窗检测

3、仅左窗检测

3、延迟线

1、左/右窗的最左单元延迟线

2、左参考窗求和结果、待检测单元延迟线

4、判决

参考说明

引言

雷达数字信号处理是数字信号处理技术在雷达领域的重要应用。CFAR(恒定虚警概率),是雷达信号处理流程中关键的环节。是连接MTD与目标凝聚的关键桥梁。

对于CFAR的基本原理与实现过程,这里就不详细阐述了。可以结合一些文献、利用 MATLAB 仿真熟悉算法步骤。

我之前做过一个有关CFAR的付费资源,感兴趣可以了解一下:

雷达信号CFAR处理——MATLAB源码![]() https://download.csdn.net/download/qq_43045275/78558406?spm=1001.2014.3001.5503这里面对原理以及算法步骤的说明非常详细。对于刚接触的同学,建议看看。

https://download.csdn.net/download/qq_43045275/78558406?spm=1001.2014.3001.5503这里面对原理以及算法步骤的说明非常详细。对于刚接触的同学,建议看看。

说明

CFAR算法主要分为均值类:CA-CFAR、GO-CFAR、SO-CFAR;以及排序类:OS-CFAR

本专栏主要针对均值类CFAR进行设计、实现、验证。

本篇博文主要介绍基于 FPGA 的 均值类CFAR 设计结构。后续几篇会介绍其代码实现、功能仿真、板级调试等。

FPGA芯片型号:xc7a35tfgg484-2

开发环境:Vivado 2018.3

CFAR检测器

1、参数说明

主要参数:

保护单元:目的是为了屏蔽距离维或者速度维的旁瓣,避免其渗入参考单元内,将噪声/杂波基底抬高,影响检测性能。因此保护单元的长度选择准则也就是距离维或速度维旁瓣的宽度。

参考单元:参考单元的均值将作为CFAR检测器的噪声/杂波电平估计值;因此参考窗长度的选择也关乎检测器的性能。

虚警概率:CFAR检测器最直接的指标。一般取到 10的负 6 次方。

门限系数:由CFAR检测器的虚警概率指标推算得到。具体的推算公式:

【注】:具体推导详见见文献【1】3.6节。

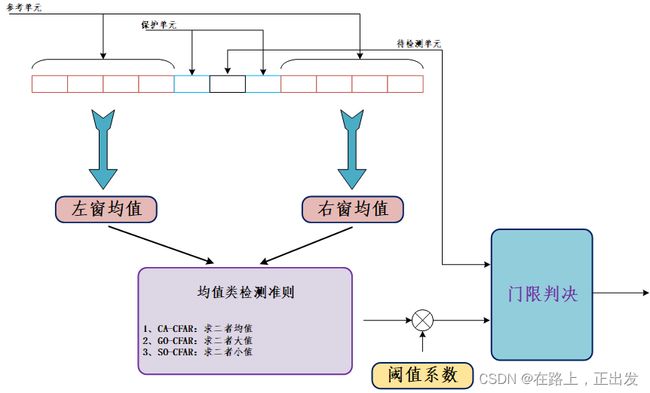

下图所示,以单侧保护单元长度1,单侧参考单元长度4 为例 说明均值类CFAR的检测原理:

2、检测过程分类

以距离维CFAR检测为例进行说明,速度维也是同样道理。

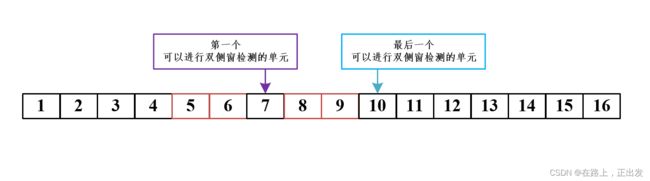

假设一个CPI的数据包括32个PRI,1个PRI采样点数为16。单侧保护单元设为2,单侧参考单元设为4。下面就具体的检测过程做详细描述。

说明:

在某些CFAR检测器的设计中,仅考虑双窗检测(即左右参考窗都存在的数据)。对于仅有左/右窗的数据直接舍弃。个人就目前的认知来说,认为不是很合理,因为目标是有可能出现在舍弃区间的,下面将想i下阐述。

1、仅右窗检测

1-6号距离单元仅能用右窗进行检测。

2、双窗检测

7-10号距离单元可用左右双窗检测。

3、仅左窗检测

11-16号距离单元仅可用左窗检测。

3、延迟线

个人觉得,CFAR检测器中最重要的设计就在于多种延迟线的设计。部分思路参考文献【2】。

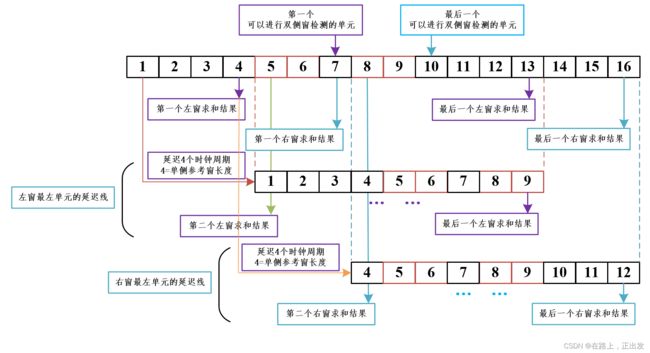

1、左/右窗的最左单元延迟线

说明:

以左窗为例详细阐述:

第1个左窗求和结果:CELL 1 + CELL 2 + CELL 3 +CELL 4 ;

第2个左窗求和结果:CELL 2 + CELL 3 +CELL 4 + CELL 5,即第1个左窗求和结果 + CELL 5 - CELL 1;

第3个左窗求和结果:CELL 3 +CELL 4 + CELL 5 + CELL 6,即第2个左窗求和结果 + CELL 6 - CELL 2;

第4个左窗求和结果:CELL 4 + CELL 5 +CELL 6 + CELL 7,即第3个左窗求和结果 + CELL 7 - CELL 3;

……

所以左窗最左侧单元需要延迟的时钟个数=单侧参考窗长度;

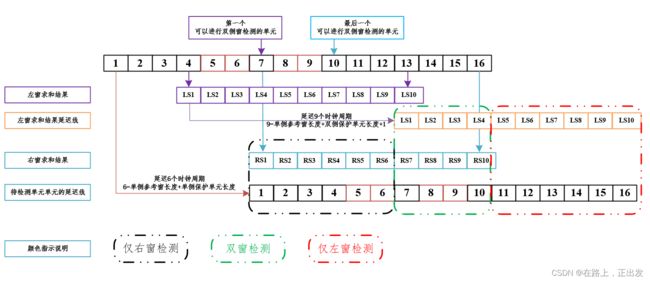

2、左参考窗求和结果、待检测单元延迟线

上图应该是非常清楚明了,这里仅做部分简单说明:

缩写:LS: Left window Sum、RS:Right window Sum

对于第 1 个待检测单元,仅能用右窗 ,而第一个右窗在单元 7 处,因此检测单元需要延迟 6 个时钟周期,后续依次顺延。

第 7 个单元检测时,用第一个左窗的求和结果 LS1,而单元 7 检测时需要用到右窗,因此左窗和 LS1 需要和 RS7 在第 13 个单元的地方对齐,需要将 LS1 延迟 9 个时钟周期,后续依次顺延。

4、判决

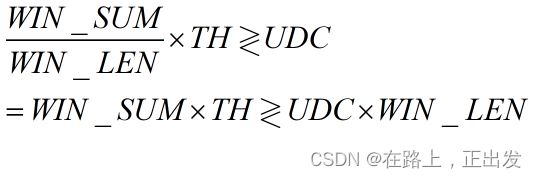

为避免除法运算,采用下面的乘法运算方式:

WIN_SUM:单侧窗求和;

WIN_LEN:但侧窗长度;

UDC:Under Detect Cell,待检测单元;

TH:门限阈值;

需要注意的是,单窗检测于双窗检测对应的窗长不同。

参考说明

[1]董书亚. 高速公路雷达信号处理算法研究与硬件实现[D].南京理工大学,2020.DOI:10.27241/d.cnki.gnjgu.2020.001673.

[2]高亚军,张冠杰,陈矛.基于FPGA的CFAR设计与实现[J].火控雷达技术,2006(03):64-68.DOI:10.19472/j.cnki.1008-8652.2006.03.017.