[连载].基于SOPC的简易数码相框 – Quartus II部分(硬件部分)

开发环境

硬件:艾米电子EP2C8 FPGA/Nios II核心板;Altera USB-Blaster;2.4寸TFT-LCD模块;SD卡模块

软件:Windows XP;Quartus II 10.0;Nios II 10.0 Software Build Tools for Eclipse

基本步骤

自底向上模式。

步骤1 在Quatus II新建一个工程

如何新建Quartus II工程,请参阅http://www.cnblogs.com/yuphone/archive/2010/08/21/1805388.html。

步骤2 设置未用引脚为三态输入

(良好的习惯,必须养成)Assignments>Device>Device and Pin Options…>Unused pins

步骤3 例化一个锁相环

由于SDRAM的时钟需要滞后Nios II软核的时钟,所以需要使用锁相环。具体的相移原理,请参阅http://www.altera.com/literature/ug/ug_embedded_ip.pdf的章节。

![image [原创][连载].基于SOPC的简易数码相框 – Quartus II部分(硬件部分)_第1张图片](http://img.e-com-net.com/image/product/a99c03e4e11e4d9092f8a2a91ba3b122.png)

如何在Quartus II中使用PLL,请参阅http://www.altera.com/literature/ug/ug_altpll.pdf。

在![]() 打开异步复位选项及稳定后锁定选项。选项有什么用?请参阅http://www.altera.com/literature/ug/ug_altpll.pdf。

打开异步复位选项及稳定后锁定选项。选项有什么用?请参阅http://www.altera.com/literature/ug/ug_altpll.pdf。

在![]() 配置输出时钟c0(Nios II系统时钟)和c1(SDRAM时钟)。

配置输出时钟c0(Nios II系统时钟)和c1(SDRAM时钟)。

注意上面那个-3.5ns的相移,具体的相移原理,请参阅http://www.altera.com/literature/ug/ug_embedded_ip.pdf的章节。

配置完的PLL框图如下所示。

步骤4 创建及配置一个Nios II软核系统

1 打开SOPC Builder。

从哪打开,怎么用?请参阅http://www.altera.com/literature/ug/ug_sopcbuilder.pdf。

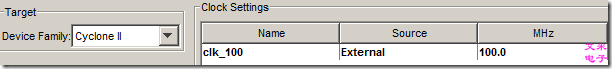

配置软核系统的目标硬件家族及输入时钟。

板载时钟为50MHz,经过PLL倍频到100MHz,下面软核系统的组件基本上都是运行在这个时钟下。输入时钟一定要认真配置,否则Nios II软件部分的延时不准,且一些组件无法正常工作。当然也可以配置n个输入时钟,不同的组件可以使用不同的时钟。

2 配置最小系统

包含cpu(Nios II软核)、ram(SDRAM或SSRAM或SRAM)、flash(EPCS FLASH或者CFI Flash)、jtag_uart(JTAG调试)以及sysid(软核标识)。以上五个部分,最好一个不落的例化到系统中;否则不良结果后果自负。重点组件的配置我会稍微说明的,其他组件自行研究(一般缺省设置)。

4 配置SDRAM选项。

此处使用的HY57V641620FTP-6,容量为8MB,资料请自行查找阅读。按器件手册说明正确选择数据总线宽度、片选数、块数、行数和列数。

选择CAS的消隐周期为3,其他参数缺省不动(或仔细阅读器件手册,酌情修改)。

5 配置Nios II软核

选择Nios II/f。三个版本的区别,请参阅http://www.altera.com/literature/hb/nios2/n2cpu_nii5v1.pdf。

配置硬件乘法及硬件除法。缺省情况下,乘法和除法都是Nios II软件实现的。

既然Cyclone II有硬件乘法器,不用白不用,按如下配置。关于硬件乘法和软件乘法的效率请参阅http://www.altera.com/literature/hb/nios2/n2cpu_nii5v1.pdf。一般情况下,乘法映射到软件中的速度最慢,LE次之,硬件乘法器就快一点,DSP Block最快,可惜Cyclone II没有DSP Block,只有硬件乘法器。硬件除法嘛,因为Cyclone II没有硬件除法器,那么选择硬件除法后,只能用LE来实现;速度较软件实现改善了许多。

配置复位向量及异常向量。有一个原则,复位向量最好映射到Flash里面(不隐射到Flash,就无法实现上电复位),异常向量必须映射到RAM里面(必须哟,千万不要映射到Flash里面)。这是为什么呢?请参阅http://www.altera.com/literature/hb/nios2/n2cpu_nii5v1.pdf。

配置缓存及存储器接口。此处缺省即可。数据缓存和地址缓存的功用请参阅http://www.altera.com/literature/hb/nios2/n2cpu_nii5v1.pdf。感兴趣的朋友可以研究下紧耦合存储器,性能相当强悍,呵呵。

配置JTAG调试模块。有一个USB-Blaster就可以使用JTAG调试Nios II软核,多么令人欢喜的消息,更欢喜的是,USB-Blaster才50块钱。调试器有四个等级,此处选择等级1,其他等级请自行研究。

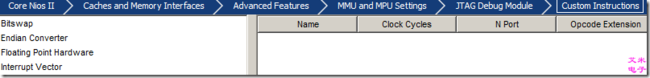

配置自定义指令,此处一个没用。Nios II软核最强大的地方就是自定义指令。Altera提供了4个自定义指令。其中硬件浮点最诱人,不过需要消耗大约4000LE,我们艾米电子的2C8资源有限,消受不起。3C10的朋友可以试试这个自定义指令,非常强悍。如何自定义指令,请参阅http://www.altera.com.cn/support/examples/nios2/exm-crc-acceleration.html。

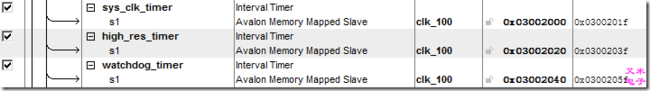

6 配置定时器组件

如何使用,请参阅:

http://www.cnblogs.com/yuphone/archive/2010/04/18/1714554.html

http://www.cnblogs.com/yuphone/archive/2010/04/18/1714628.html

http://www.cnblogs.com/yuphone/archive/2010/04/19/1715525.html

http://www.cnblogs.com/yuphone/archive/2010/11/25/1887621.html

sys_clk_timer,![]() ;

;

high_res_timer是![]() ,可做定时器中断应用或做Timestamp应用;

,可做定时器中断应用或做Timestamp应用;

watchdog_timer是![]() ,其功用就不用我言说了。

,其功用就不用我言说了。

虽然上面的三个定时器在本设计中都未使用,但是为了更好的扩展,加上比较好。

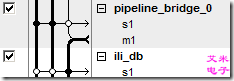

7 配置流水桥

流水桥的功用请参阅http://www.altera.com.cn/support/examples/nios2/exm-high-perf-bridge.html。

在SOPC Builder中例化pipeline_bridge之后,会出来两个总线,s1(主端)与Nios II CPU相连,m1(从端)与需要“过桥”的组件的相连。

配置流水桥相关选项。

8 配置GPIO——ILI9325

本设计中,所有的GPIO的s1(主端),都挂在流水桥上。

配置ILI9325引脚。

怎么搭桥呢?我以ili_db为例。当添加了GPIO——ili_db后,在ili_db左边就会出现3个桥供选择。可以清楚的看到,这三座桥依次(从左到右)为Nios II cpu的指令主端、Nios II cpu的指令从端和流水桥的从端。

现在GPIO想要过流水桥,就把与流水桥从端相连的那个点选上即可。这样ili_db就过桥了,其他类似。

注意ili9325的各总线及引脚的配置。

ili_db,ili9325的8位数据总线(16位及18位的数据总线与之类似),按下图配置(8位双向口):

ili_nrst,ili9325的硬件复位信号引脚(低电平有效);

ili_ncs,ili9325的片选信号引脚(低电平有效);

ili_rs,ili9325的指令 /数据选择信号引脚;

ili_nwr,ili9325的写控制信号引脚(低电平有效);

ili_nrd,ili9325的读控制信号引脚(低电平有效)。

以上五个引脚全部按下图配置(一位输出口):

9 配置GPIO——ADS7843

此处并没有使用Altera提供的三线SPI总线组件,而是使用GPIO模拟SPI总线。配置方法和ILI9325类似。

需要注意的是,ads_nirq,ads7843的笔触中断信号引脚,需要设置为下降沿触发中断。

10 配置GPIO——SD卡

选用的SD模块使用的1线SD协议,即SPI协议。

此处并没有使用Altera提供的三线SPI总线组件,而是使用GPIO模拟SPI总线。配置方法和ILI9325类似。

完成以上十步后,编译。不会编译?请参阅http://www.cnblogs.com/yuphone/archive/2010/05/07/1729752.html。

步骤5 使用HDL描述Quartus II顶层模块

例化PLL和Nios II模块时,请使用HDL例化模板文件,比如pll模块的例化模板pll_inst.v,nios软核模块的例化模块nios_ii_sys_inst.v。要善用模板来快速例化模块。怎么例化?回去看书去!

代码 顶层模块

module lcd_at_nios( input CLOCK_50, input Q_KEY, // ILI9325 Interface output ILI_nRST, output ILI_nCS, output ILI_RS, output ILI_nRD, output ILI_nWR, inout [ 7:0] ILI_DB, // ADS7803 Interface output ADS_CLK, output ADS_nCS, output ADS_DIN, input ADS_DOUT, input ADS_BUSY, input ADS_nIRQ, // SD Card Interface output SD_CLK, output SD_nCS, output SD_DIN, input SD_DOUT, // SDRAM Interface output [11:0] SDRAM_ADDR, output [1 :0] SDRAM_BA, output SDRAM_CAS_N, output SDRAM_CLK, output SDRAM_CKE, output SDRAM_CS_N, inout [15:0] SDRAM_DQ, output [ 1:0] SDRAM_DQM, output SDRAM_RAS_N, output SDRAM_WE_N ); wire nii_clk, pll_locked; pll pll_inst ( .areset (~Q_KEY), .inclk0 (CLOCK_50), .c0 (nii_clk), .c1 (SDRAM_CLK), .locked (pll_locked) ); nios_ii_sys nios_ii_sys_inst ( // .clk_100 (nii_clk), .reset_n (Q_KEY & pll_locked), // ADS7803 Interface .in_port_to_the_ads_busy (ADS_BUSY), .in_port_to_the_ads_dout (ADS_DOUT), .in_port_to_the_ads_nirq (ADS_nIRQ), .out_port_from_the_ads_clk (ADS_CLK), .out_port_from_the_ads_din (ADS_DIN), .out_port_from_the_ads_ncs (ADS_nCS), // ILI9325 Interface .bidir_port_to_and_from_the_ili_db (ILI_DB), .out_port_from_the_ili_ncs (ILI_nCS), .out_port_from_the_ili_nrd (ILI_nRD), .out_port_from_the_ili_nrst (ILI_nRST), .out_port_from_the_ili_rs (ILI_RS), .out_port_from_the_ili_nwr (ILI_nWR), // SD Card Interface .out_port_from_the_sd_clk (SD_CLK), .out_port_from_the_sd_din (SD_DIN), .out_port_from_the_sd_ncs (SD_nCS), .in_port_to_the_sd_dout (SD_DOUT), // SDRAM Interface .zs_addr_from_the_sdram (SDRAM_ADDR), .zs_ba_from_the_sdram (SDRAM_BA), .zs_cas_n_from_the_sdram (SDRAM_CAS_N), .zs_cke_from_the_sdram (SDRAM_CKE), .zs_cs_n_from_the_sdram (SDRAM_CS_N), .zs_dq_to_and_from_the_sdram (SDRAM_DQ), .zs_dqm_from_the_sdram (SDRAM_DQM), .zs_ras_n_from_the_sdram (SDRAM_RAS_N), .zs_we_n_from_the_sdram (SDRAM_WE_N) ); endmodule

代码 锁相环模块的例化模板

pll pll_inst (

.areset ( areset_sig ),

.inclk0 ( inclk0_sig ),

.c0 ( c0_sig ),

.c1 ( c1_sig ),

.locked ( locked_sig )

);

代码 nios软核模块的例化模板

//Example instantiation for system 'nios_ii_sys'

nios_ii_sys nios_ii_sys_inst

(

.bidir_port_to_and_from_the_ili_db (bidir_port_to_and_from_the_ili_db),

.clk_100 (clk_100),

.in_port_to_the_ads_busy (in_port_to_the_ads_busy),

.in_port_to_the_ads_dout (in_port_to_the_ads_dout),

.in_port_to_the_ads_nirq (in_port_to_the_ads_nirq),

.in_port_to_the_sd_dout (in_port_to_the_sd_dout),

.out_port_from_the_ads_clk (out_port_from_the_ads_clk),

.out_port_from_the_ads_din (out_port_from_the_ads_din),

.out_port_from_the_ads_ncs (out_port_from_the_ads_ncs),

.out_port_from_the_ili_ncs (out_port_from_the_ili_ncs),

.out_port_from_the_ili_nrd (out_port_from_the_ili_nrd),

.out_port_from_the_ili_nrst (out_port_from_the_ili_nrst),

.out_port_from_the_ili_nwr (out_port_from_the_ili_nwr),

.out_port_from_the_ili_rs (out_port_from_the_ili_rs),

.out_port_from_the_sd_clk (out_port_from_the_sd_clk),

.out_port_from_the_sd_din (out_port_from_the_sd_din),

.out_port_from_the_sd_ncs (out_port_from_the_sd_ncs),

.reset_n (reset_n),

.zs_addr_from_the_sdram (zs_addr_from_the_sdram),

.zs_ba_from_the_sdram (zs_ba_from_the_sdram),

.zs_cas_n_from_the_sdram (zs_cas_n_from_the_sdram),

.zs_cke_from_the_sdram (zs_cke_from_the_sdram),

.zs_cs_n_from_the_sdram (zs_cs_n_from_the_sdram),

.zs_dq_to_and_from_the_sdram (zs_dq_to_and_from_the_sdram),

.zs_dqm_from_the_sdram (zs_dqm_from_the_sdram),

.zs_ras_n_from_the_sdram (zs_ras_n_from_the_sdram),

.zs_we_n_from_the_sdram (zs_we_n_from_the_sdram)

);

步骤6 分配引脚

怎么分配引脚?请参阅http://www.cnblogs.com/yuphone/archive/2010/01/18/1650612.html。

分配引脚模板

To, Location

// 板载时钟50MHz

CLOCK_50, PIN_23

// 板载RST_N

Q_KEY, PIN_

// SDRAM

SDRAM_ADDR[0], PIN_

SDRAM_ADDR[1], PIN_

SDRAM_ADDR[2], PIN_

SDRAM_ADDR[3], PIN_

SDRAM_ADDR[4], PIN_

SDRAM_ADDR[5], PIN_

SDRAM_ADDR[6], PIN_

SDRAM_ADDR[7], PIN_

SDRAM_ADDR[8], PIN_

SDRAM_ADDR[9], PIN_

SDRAM_ADDR[10], PIN_

SDRAM_ADDR[11], PIN_

SDRAM_BA[0], PIN_

SDRAM_BA[1], PIN_

SDRAM_CAS_N, PIN_

SDRAM_CLK, PIN_

SDRAM_CKE, PIN_

SDRAM_CS_N, PIN_

SDRAM_DQ[0], PIN_

SDRAM_DQ[1], PIN_

SDRAM_DQ[2], PIN_

SDRAM_DQ[3], PIN_

SDRAM_DQ[4], PIN_

SDRAM_DQ[5], PIN_

SDRAM_DQ[6], PIN_

SDRAM_DQ[7], PIN_

SDRAM_DQ[8], PIN_

SDRAM_DQ[9], PIN_

SDRAM_DQ[10], PIN_

SDRAM_DQ[11], PIN_

SDRAM_DQ[12], PIN_

SDRAM_DQ[13], PIN_

SDRAM_DQ[14], PIN_

SDRAM_DQ[15], PIN_

SDRAM_DQM[0], PIN_

SDRAM_DQM[1], PIN_

SDRAM_RAS_N, PIN_

SDRAM_WE_N, PIN_

// ILI9325

ILI_RS, PIN_

ILI_nWR, PIN_

ILI_nRD, PIN_

ILI_DB[0], PIN_

ILI_DB[1], PIN_

ILI_DB[2], PIN_

ILI_DB[3], PIN_

ILI_DB[4], PIN_

ILI_DB[5], PIN_

ILI_DB[6], PIN_

ILI_DB[7], PIN_

ILI_nCS, PIN_

ILI_nRST, PIN_

// ADS7803

ADS_CLK, PIN_

ADS_nCS, PIN_

ADS_DIN, PIN_

ADS_DOUT, PIN_

ADS_BUSY, PIN_

ADS_nIRQ, PIN_

// SD Card

SD_CLK, PIN_

SD_nCS, PIN_

SD_DIN, PIN_

SD_DOUT, PIN_

步骤7 约束时钟

自行研究。

步骤8 编译

自行研究。

源码下载

目录

1 [原创][连载].基于SOPC的简易数码相框 - Quartus II部分(硬件部分)

2 [原创][连载].基于SOPC的简易数码相框 - Nios II SBTE部分(软件部分)- 配置工作

3 [原创][连载].基于SOPC的简易数码相框 - Nios II SBTE部分(软件部分)- SD卡(SPI模式)驱动

4 [原创][连载].基于SOPC的简易数码相框 - Nios II SBTE部分(软件部分)- TFT-LCD(控制器为ILI9325)驱动

5 [原创][连载].基于SOPC的简易数码相框 - Nios II SBTE部分(软件部分)- 从SD卡内读取图片文件,然后显示在TFT-LCD上

6 [原创][连载].基于SOPC的简易数码相框 - Nios II SBTE部分(软件部分)- 优化工作

7 [原创][连载].基于SOPC的简易数码相框 - Nios II SBTE部分(软件部分)- ADS7843触摸屏驱动测试

![image [原创][连载].基于SOPC的简易数码相框 – Quartus II部分(硬件部分)_第2张图片](http://img.e-com-net.com/image/product/68d4268b3fd64e1cadf4df48503ee2f3.png)

![image [原创][连载].基于SOPC的简易数码相框 – Quartus II部分(硬件部分)_第3张图片](http://img.e-com-net.com/image/product/6f1d73dcc4b9438bbaefe871210a29b1.png)

![image [原创][连载].基于SOPC的简易数码相框 – Quartus II部分(硬件部分)_第4张图片](http://img.e-com-net.com/image/product/00f59977d7ef43138bf72bcc93c352a5.png)

![image [原创][连载].基于SOPC的简易数码相框 – Quartus II部分(硬件部分)_第5张图片](http://img.e-com-net.com/image/product/243ca5bffc6b43febd4dcd5b03ad9cb1.png)

![image [原创][连载].基于SOPC的简易数码相框 – Quartus II部分(硬件部分)_第6张图片](http://img.e-com-net.com/image/product/3a639e262f324c96ae0db9154710f60d.png)

![image [原创][连载].基于SOPC的简易数码相框 – Quartus II部分(硬件部分)_第7张图片](http://img.e-com-net.com/image/product/a6f5a58990054bbb85d9efa103cc370f.png)

![image [原创][连载].基于SOPC的简易数码相框 – Quartus II部分(硬件部分)_第8张图片](http://img.e-com-net.com/image/product/a84acb11f4244ac9b0ba8e3948ff27d9.png)

![image [原创][连载].基于SOPC的简易数码相框 – Quartus II部分(硬件部分)_第9张图片](http://img.e-com-net.com/image/product/07f52ac8bc404546bb2313cf8f9847ec.png)

![image [原创][连载].基于SOPC的简易数码相框 – Quartus II部分(硬件部分)_第10张图片](http://img.e-com-net.com/image/product/4b9f5e8dc55648dead9348b8b36c10f5.png)

![image [原创][连载].基于SOPC的简易数码相框 – Quartus II部分(硬件部分)_第11张图片](http://img.e-com-net.com/image/product/7318663710ec4e62a6f9929b9650db64.png)

![image [原创][连载].基于SOPC的简易数码相框 – Quartus II部分(硬件部分)_第12张图片](http://img.e-com-net.com/image/product/b63f09246a314eb989d72008b657ba54.png)

![image [原创][连载].基于SOPC的简易数码相框 – Quartus II部分(硬件部分)_第13张图片](http://img.e-com-net.com/image/product/f0edf5f9c00b4e77b8f998f1fd88463a.png)

![image [原创][连载].基于SOPC的简易数码相框 – Quartus II部分(硬件部分)_第14张图片](http://img.e-com-net.com/image/product/af22e0cdf160414fa49efdc6e36c1e36.png)

![image [原创][连载].基于SOPC的简易数码相框 – Quartus II部分(硬件部分)_第15张图片](http://img.e-com-net.com/image/product/b30bcdcb1d284cd7a85eb9ce1246bf53.png)

![image [原创][连载].基于SOPC的简易数码相框 – Quartus II部分(硬件部分)_第16张图片](http://img.e-com-net.com/image/product/4f0808ff9ce846c691076493dda85b83.png)

![image [原创][连载].基于SOPC的简易数码相框 – Quartus II部分(硬件部分)_第17张图片](http://img.e-com-net.com/image/product/8144109d65584e35b1fa5039920688e0.png)

![image [原创][连载].基于SOPC的简易数码相框 – Quartus II部分(硬件部分)_第18张图片](http://img.e-com-net.com/image/product/33525b275aa346d48a9c61d17b82cb79.png)

![image [原创][连载].基于SOPC的简易数码相框 – Quartus II部分(硬件部分)_第19张图片](http://img.e-com-net.com/image/product/8f2fb71ac81648a0bebb45d6eb1df3b1.png)

![image [原创][连载].基于SOPC的简易数码相框 – Quartus II部分(硬件部分)_第20张图片](http://img.e-com-net.com/image/product/ff7e3094284642c09702c5af4a03f80e.png)

![image [原创][连载].基于SOPC的简易数码相框 – Quartus II部分(硬件部分)_第21张图片](http://img.e-com-net.com/image/product/3597fa4b1b234e449efe61004f060f3f.png)

![image [原创][连载].基于SOPC的简易数码相框 – Quartus II部分(硬件部分)_第22张图片](http://img.e-com-net.com/image/product/4023b625cf28412c88ed4b010fcaf3d2.png)