- [Verilog]带使能端的级联BCD码计数器 - 以时钟计数器为例

Jason_Tye

fpga开发

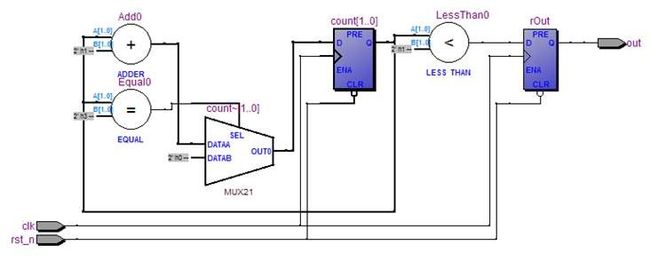

问题描述//模块声明moduletop_module(inputclk,inputreset,inputena,outputpm,output[7:0]hh,output[7:0]mm,output[7:0]ss);前置知识:BCD码:将十进制数的每一位(0~9)按序,用4位2进制数表示Decimal=[3:0]Binary(78)10=(0111,1000)BCDDecimal=[3:0]\Bi

- [Verilog]模块实例化驱动的理解

Jason_Tye

fpga开发

笔者在复习刷题HDLBits时,对模块实例化时,接口的驱动有了更深理解.问题描述实现100位的带涟漪进位(ripple-carry)的全加器处理过程这是一个纯组合逻辑电路,除了可能在CombinationalBlocksalways@(*)中进行的赋值外,无需reg,所以默认的wire类型不予显式.首先实现单位全加器full_addermodulefadd(inputa;inputb;inputc

- - `always @(posedge opt_txclk)` 触发后,调用内部有 `@(posedge opt_txclk)`的task

零度随想

fpga开发

问题背景always@(posedgeopt_txclk)触发后,调用task。task内部还有@(posedgeopt_txclk),但在下一个时钟沿到来之前,always块会不会重新触发,从而导致错误。Verilog的事件调度机制always@(posedgeopt_txclk)每当opt_txclk出现上升沿时,always块会被触发,进入执行状态。任务中的@(posedgeopt_txcl

- 均薪23W还缺人,FPGA工程师到底有多重要?

博览鸿蒙

FPGAfpga开发

近两年,随着FPGA行业的快速发展,FPGA工程师的需求量持续增长。FPGA技术在通信、人工智能、自动驾驶、数据中心等领域的广泛应用,使得这一岗位变得尤为重要。尤其是在高性能计算、边缘计算等场景下,FPGA凭借其高并行计算能力和灵活性,成为不可或缺的技术方案。FPGA工程师的核心职责FPGA工程师主要负责FPGA的开发、调试和优化,具体包括:逻辑设计与实现:使用Verilog/VHDL等硬件描述语

- Verilog 实现 FPGA 复杂算法的案例

百态老人

fpga开发

在数字电路设计领域,FPGA(现场可编程门阵列)因其灵活性和高性能而备受青睐。有许多利用Verilog实现FPGA复杂算法的案例。例如,有一个项目是在FPGA中用Verilog实现开方运算。该项目充分利用Verilog的强大功能,通过深入理解FPGA的内部结构优化代码资源利用率,采用经典数学算法确保计算结果的准确性和高效性。具有高效性、可移植性和易用性等优势,适用于对实时性要求较高的应用场景,为开

- XY2-100协议解析

李逍遥lzx

fpga开发

前言XY2-100及XY2-100-E协议被广泛地应用于激光振镜的控制中,本文将从激光振镜控制原理,接口引脚定义,协议时序,以及verilog代码实现实现这几个角度展开本文。本文参考RAYLASE的官方文档一、激光振镜的工作原理激光振镜所使用的电机为检流式电机,检流式电机工作原理类似于电流计,电机的旋转角度会随着输入电压变化.当转动的电磁力矩与回复力矩平衡时,电机偏转到位,此时的偏转角与输入电压成

- XY2-100的Verilog实现

csdn_gddf102384398

fpga开发

xy2_100.vmodulexy2_100(inputclk,inputtx_init,//当产生上升沿时,开始发数据inputwire[15:0]x_pos,inputwire[15:0]y_pos,inputwire[15:0]z_pos,outputclk_2MHz_o,//输出2MHz时钟outputsync_o,outputx_ch_o,outputy_ch_o,outputz_ch_

- 【了不起的芯片底层】-verilog设计实例

huxixi_2

数字ICfpga开发

序列检测器作用:从一串码流中检测出指定序列10010,监测到一个序列后就输出一个高电平。设计状态转换机制:初始是IDLE态,然后输入1后进入A状态,输出0;输入0依然保持IDLE,输出0;在A状态,输入0进入B状态,输出0;输入1进入F中间态,输出0;在B状态,输入0进入C状态,输出0;输入1进入G中间态,输出0;.....以此类推所有状态。一共8个状态,需要3位记录状态的寄存器,实现代码如下:/

- Verilog 语法篇 硬件描述语言

7yewh

【FPGA知识点笔记汇总】fpga开发硬件工程驱动开发arm开发物联网iot

Verilog是一种硬件描述语言,用于设计、模拟和综合数字电路和系统。它主要用于描述ASIC(专用集成电路)或FPGA(现场可编程门阵列)等硬件设备的结构和行为。定义与用途:Verilog是一种硬件描述语言(HDL),主要用于数字电路的建模、仿真、综合与验证。设计人员利用它来描述电路的结构、行为以及时序关系,从而生成实际的硬件电路(如FPGA或ASIC)。发展背景:1984年,PhilMoorby

- 【Verilog中的function和task可综合用法】

中古传奇

HDL

Verilog中的function和task用法1概念1.1VS1.2function1.3task1.4示例【博客首发于微信公众号《漫谈芯片与编程》,欢迎专注一下,多谢大家】在Verilog中,function和task都是用于封装可重用代码的结构;通过把代码分成小的模块或者使用任务(task)和函数(function),可把一项任务分成许多较小的、易于管理的部分,从而提高代码的可读性、可维护性

- Verilog基础(三):过程

TrustZone_

IC验证之旅fpga开发verilog

过程(Procedures)-Always块–组合逻辑(Alwaysblocks–Combinational)由于数字电路是由电线相连的逻辑门组成的,所以任何电路都可以表示为模块和赋值语句的某种组合.然而,有时这不是描述电路最方便的方法.两种alwaysblock是十分有用的:组合逻辑:always@(*)时序逻辑:always@(posedgeclk)always@(*)就相当于赋值语句–ass

- 验证工具:VCS简要教程

TrustZone_

IC验证之旅IC

1.引言在本课程中,我们将使用Synopsys的VCS工具套件。我们主要使用的工具将是VCS(Verilog编译器仿真器)和VirSim,后者是VCS的图形用户界面,用于调试和查看波形。这些工具目前安装在Sun应用服务器(sunapp1、sunapp2和sunapp3)上。因此,您需要通过SSH连接到sunapp1、sunapp2或sunapp3来使用VCS工具套件。调试项目设计的方法包括三个步骤

- 验证工具:VCS与Verdi介绍

TrustZone_

IC验证之旅fpga开发

VCS和Verdi都是Synopsys公司旗下的工具,在集成电路设计和验证领域发挥着重要作用。VCSVCS,全称VerilogCompileSimulator,是Synopsys公司的一款Verilog仿真工具。它具有以下主要功能:编译和仿真:VCS能够对Verilog设计代码和testbench进行编译,生成simv二进制可执行文件,该文件后续用于仿真。它支持Verilog-1995、Veril

- Verilog基础(五):时序逻辑

TrustZone_

IC验证之旅fpga开发verilog

时序逻辑(SequentialLogin)锁存器与触发器-D-触发器(Dflip-flops)D-触发器可以存储一个bit数据并根据时钟信号周期的更新数据,一般是由正边沿触发.D-触发器由逻辑合成器(Logicsynthesizer)在使用"Alwaysblock"时创建(参见AlwaysBlock2).D-触发器是"组合逻辑块之后连接触发器"的最简单形式,其中组合逻辑部分只是一个wire类型变量

- 编程AI深度实战:自己的AI,必会LangChain

relis

编程AI:企业级开发深度实战pythonlangchainrag知识库芯片设计ai大模型

系列文章:编程AI深度实战:私有模型deepseekr1,必会ollama-CSDN博客编程AI深度实战:自己的AI,必会LangChain-CSDN博客编程AI深度实战:给vim装上AI-CSDN博客编程AI深度实战:火的编程AI,都在用语法树(AST)-CSDN博客编程AI深度实战:让verilog不再是AI的小众语言-CSDN博客您听说过LangChain这个术语,但不确定它到底是什么?那么

- (16)System Verilog联合体union详解

宁静致远dream

SystemVerilog教程stm32深度学习机器学习

(16)SystemVerilog联合体union详解1.1目录1)目录2)FPGA简介3)SystemVerilog简介4)SystemVerilog联合体union详解5)结语1.2FPGA简介FPGA(FieldProgrammableGateArray)是在PAL、GAL等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的

- FPGA约束:如何生成时钟多路复用器及时钟约束?

编码实践

fpga开发matlab

FPGA约束:如何生成时钟多路复用器及时钟约束?在现代数字电路设计中,高速信号的传输对时钟信号的要求非常严格。设计者通常需要生成各种时钟信号,并为其指定合适的时钟约束。为了优化资源使用,FPGA中经常使用时钟多路复用器来同时提供多个时钟。本文将介绍如何使用VerilogHDL编写时钟多路复用器,并为其生成合适的时钟约束。时钟多路复用器的实现代码如下所示:moduleclk_mux#(paramet

- SystemVerilog模块定义例化及接口

pilxpi

功能测试

今天我们主要跟随《漫游》模块定义例化(7.2节)及接口(7.3节)模块定义及例化这里,我们主要强调一个地方,就是参数化及宏的使用。在实际项目中,参数化是和宏是非常常用的。在设计中,我们要求所有变量都要通过宏来表示,没有宏名称表示的数字,我们会戏称其为“魔鬼数字”,因为其含义需要追溯才能理解,不便于调试及模块代码传承。但是验证环境中,由于需要兼顾效率,所以要求没有这么严格。接口这里,我们一定是采用连

- 编程AI深度实战:使用 tree sitter 构建更好的代码库地图

relis

编程AI:企业级开发深度实战AI大模型编程代码库treesitter上下文嵌入

系列文章:编程AI深度实战:私有模型deepseekr1,必会ollama-CSDN博客编程AI深度实战:自己的AI,必会LangChain-CSDN博客编程AI深度实战:给vim装上AI-CSDN博客编程AI深度实战:火的编程AI,都在用语法树(AST)-CSDN博客编程AI深度实战:让verilog不再是AI的小众语言-CSDN博客GPT-4对于“自包含”编码任务非常有用,例如生成或修改没有依

- 编程AI深度实战:让verilog不再是 AI 的小众语言

relis

编程AI:企业级开发深度实战vimverilogrulelint芯片设计ai大模型

系列文章:编程AI深度实战:私有模型deepseekr1,必会ollama-CSDN博客编程AI深度实战:自己的AI,必会LangChain-CSDN博客编程AI深度实战:给vim装上AI-CSDN博客编程AI深度实战:火的编程AI,都在用语法树(AST)-CSDN博客

- 编程AI深度实战:给vim装上AI

relis

编程AI:企业级开发深度实战vimaichat大模型芯片设计ide编程

系列文章:编程AI深度实战:私有模型deepseekr1,必会ollama-CSDN博客编程AI深度实战:自己的AI,必会LangChain-CSDN博客编程AI深度实战:给vim装上AI-CSDN博客编程AI深度实战:火的编程AI,都在用语法树(AST)-CSDN博客编程AI深度实战:让verilog不再是AI的小众语言-CSDN博客文末有vim-ollama安装指南。VIMAI插件列表以下是G

- SystemVerilog变量的符号

pilxpi

功能测试

过年这几天,偷懒了,没有认真创作,但是素材收集了一些,今天专门聊聊变量的符号,我们只从书中的一个点来切入。引用《漫游》原文:从仿真器得到的结果是:如果按照有符号和无符号的类型划分,那么可以将常见的变量类型划分为:·有符号类型:byte、shortint、int、longint、integer。·无符号类型:bit、logic、reg、net-type(如wire、tri)。上文的“signed_v

- nios ii FIFO读取FPGA数据交互实验1

尼德兰的喵

FPGA相关EDA工具使用笔记NiOSiialteraquartus硬件fpga

实验所用板子为altera经典的DE2板子,FPGA为CycloneII:EP2C35F672C6,quartus版本为13.01.建立工程,导入管脚图DE2_pin_assignments.csv文件,写入硬件代码并编译。最终的硬件verilog代码如下(部分代码需要在生成Qsys文件之后才能编译通过):modulework(CLOCK_50,KEY,SW,LEDR);inputCLOCK_50

- 第14篇:2线-4线译码器

Terasic友晶科技

数字逻辑(DE2-115)fpga开发

Q:有编码器那对应的就会有译码器,本期我们来设计实现2线-4线二进制译码器。A:基本原理:译码器是编码器的逆过程,其功能是将具有特定含义的二进制码转换为对应的输出信号。2线-4线二进制译码器有2个输入共4种不同的组合状态,因此可以解码出4组输出信号。这里我们还设置使能信号,只有使能信号为“1”时译码器才会工作,否则输出全为1。用Verilog过程结构always表示部分代码:使用DE2-115开发

- 【教程4>第5章>第22节】基于FPGA的Gardner环实现——时偏误差检测模块

fpga和matlab

#fpga开发Gardner环时偏误差检测教程4

欢迎订阅FPGA/MATLAB/Simulink系列教程《★教程1:matlab入门100例》《★教程2:fpga入门100例》《★教程3:simulink入门60例》《★教程4:FPGA/MATLAB/Simulink联合开发入门与进阶X例》目录1.软件版本2.时偏误差检测模块的FPGA实现2.1原理回顾2.2verilog程序3.时偏误差检测模块的仿真测试

- verilog中+:和-:用法

snow每天都要好好学习

Verilogfpga开发

verilog中的+:和-:用法在Verilog中,+:和-:是用于部分选择的操作符,它们通常用来选择一个向量中的一部分,或者进行位的切片操作。+:用于从指定起始位向右选取一定数量的位。-:用于从指定起始位向左选取一定数量的位。+:操作符+:表示从某个位开始,向右延伸一定数量的位。这是对向量的一种正向选择。语法如下:vector[start_bit+:size]start_bit是选择的起始位。s

- Verilog系统函数实现单精度float、双精度doble浮点类型和整型之间互相转换

whik1194

XilinxFPGAZYNQverilogsystemverilog

标准verilog支持双精度double类型和十六进制64位数据相互转换,使用$realtobits和$bitstoreal系统函数使用示例://test_tb.v`timescale1ns/1psmoduletest_tb;realdata_real;reg[63:0]data_hex;initialbegindata_real=0;data_hex=0;data_real=1234.56789

- I2C协议与FPGA开发教程_VHDL/Verilog实现

侯昂

本文还有配套的精品资源,点击获取简介:本压缩包文件包含了I2C协议的学习资料,特别是针对FPGA开发的实验教程。内容涵盖了I2C基础知识、通信模式、总线仲裁机制,以及用VHDL和Verilog语言实现I2C控制器的方法。教程还包括在FPGA平台配置I2C接口的详细步骤和实验指导,帮助读者深入理解I2C协议,并在FPGA上实现其控制。1.I2C协议基础介绍I2C(Inter-IntegratedCi

- verilog Matlab GPS C/A码发生器.

today_typ

verilog学习日志开发语言matlab经验分享fpga开发

本文所涉文献资料均为开源免费,参考文献、声明链接等均写在文末。1.C/A码简要介绍GPS卫星信号包括载波信号、测距码和数据码.其中的测码粗码即C/A码(CoarseAcquisitionCode)除了作为粗测码外,还由于其具有码长短,易于捕获的特点而作为GPS卫星信号的捕获码,因此C/A码是GPS信号捕获以及接收机实现的基础。[1]GPS系统中使用了两种伪随机码,一种是时钟速率为10.23MHz用

- Quartus Prime 仿真相关报错解决方法

门外的兔子

问题解决fpga开发嵌入式硬件

出现如图相关报错是因为文件路径的问题解决方法如下:第一步打开仿真设置第二步检查如图所示路径是否正确即对应.VMF文件保存的路径复制粘贴可见上方文本如下quartus_eda--gen_testbench--tool=modelsim_oem--format=verilog--write_settings_files=offProject-cProject--vector_source="D:/Kt

- mondb入手

木zi_鸣

mongodb

windows 启动mongodb 编写bat文件,

mongod --dbpath D:\software\MongoDBDATA

mongod --help 查询各种配置

配置在mongob

打开批处理,即可启动,27017原生端口,shell操作监控端口 扩展28017,web端操作端口

启动配置文件配置,

数据更灵活

- 大型高并发高负载网站的系统架构

bijian1013

高并发负载均衡

扩展Web应用程序

一.概念

简单的来说,如果一个系统可扩展,那么你可以通过扩展来提供系统的性能。这代表着系统能够容纳更高的负载、更大的数据集,并且系统是可维护的。扩展和语言、某项具体的技术都是无关的。扩展可以分为两种:

1.

- DISPLAY变量和xhost(原创)

czmmiao

display

DISPLAY

在Linux/Unix类操作系统上, DISPLAY用来设置将图形显示到何处. 直接登陆图形界面或者登陆命令行界面后使用startx启动图形, DISPLAY环境变量将自动设置为:0:0, 此时可以打开终端, 输出图形程序的名称(比如xclock)来启动程序, 图形将显示在本地窗口上, 在终端上输入printenv查看当前环境变量, 输出结果中有如下内容:DISPLAY=:0.0

- 获取B/S客户端IP

周凡杨

java编程jspWeb浏览器

最近想写个B/S架构的聊天系统,因为以前做过C/S架构的QQ聊天系统,所以对于Socket通信编程只是一个巩固。对于C/S架构的聊天系统,由于存在客户端Java应用,所以直接在代码中获取客户端的IP,应用的方法为:

String ip = InetAddress.getLocalHost().getHostAddress();

然而对于WEB

- 浅谈类和对象

朱辉辉33

编程

类是对一类事物的总称,对象是描述一个物体的特征,类是对象的抽象。简单来说,类是抽象的,不占用内存,对象是具体的,

占用存储空间。

类是由属性和方法构成的,基本格式是public class 类名{

//定义属性

private/public 数据类型 属性名;

//定义方法

publ

- android activity与viewpager+fragment的生命周期问题

肆无忌惮_

viewpager

有一个Activity里面是ViewPager,ViewPager里面放了两个Fragment。

第一次进入这个Activity。开启了服务,并在onResume方法中绑定服务后,对Service进行了一定的初始化,其中调用了Fragment中的一个属性。

super.onResume();

bindService(intent, conn, BIND_AUTO_CREATE);

- base64Encode对图片进行编码

843977358

base64图片encoder

/**

* 对图片进行base64encoder编码

*

* @author mrZhang

* @param path

* @return

*/

public static String encodeImage(String path) {

BASE64Encoder encoder = null;

byte[] b = null;

I

- Request Header简介

aigo

servlet

当一个客户端(通常是浏览器)向Web服务器发送一个请求是,它要发送一个请求的命令行,一般是GET或POST命令,当发送POST命令时,它还必须向服务器发送一个叫“Content-Length”的请求头(Request Header) 用以指明请求数据的长度,除了Content-Length之外,它还可以向服务器发送其它一些Headers,如:

- HttpClient4.3 创建SSL协议的HttpClient对象

alleni123

httpclient爬虫ssl

public class HttpClientUtils

{

public static CloseableHttpClient createSSLClientDefault(CookieStore cookies){

SSLContext sslContext=null;

try

{

sslContext=new SSLContextBuilder().l

- java取反 -右移-左移-无符号右移的探讨

百合不是茶

位运算符 位移

取反:

在二进制中第一位,1表示符数,0表示正数

byte a = -1;

原码:10000001

反码:11111110

补码:11111111

//异或: 00000000

byte b = -2;

原码:10000010

反码:11111101

补码:11111110

//异或: 00000001

- java多线程join的作用与用法

bijian1013

java多线程

对于JAVA的join,JDK 是这样说的:join public final void join (long millis )throws InterruptedException Waits at most millis milliseconds for this thread to die. A timeout of 0 means t

- Java发送http请求(get 与post方法请求)

bijian1013

javaspring

PostRequest.java

package com.bijian.study;

import java.io.BufferedReader;

import java.io.DataOutputStream;

import java.io.IOException;

import java.io.InputStreamReader;

import java.net.HttpURL

- 【Struts2二】struts.xml中package下的action配置项默认值

bit1129

struts.xml

在第一部份,定义了struts.xml文件,如下所示:

<!DOCTYPE struts PUBLIC

"-//Apache Software Foundation//DTD Struts Configuration 2.3//EN"

"http://struts.apache.org/dtds/struts

- 【Kafka十三】Kafka Simple Consumer

bit1129

simple

代码中关于Host和Port是割裂开的,这会导致单机环境下的伪分布式Kafka集群环境下,这个例子没法运行。

实际情况是需要将host和port绑定到一起,

package kafka.examples.lowlevel;

import kafka.api.FetchRequest;

import kafka.api.FetchRequestBuilder;

impo

- nodejs学习api

ronin47

nodejs api

NodeJS基础 什么是NodeJS

JS是脚本语言,脚本语言都需要一个解析器才能运行。对于写在HTML页面里的JS,浏览器充当了解析器的角色。而对于需要独立运行的JS,NodeJS就是一个解析器。

每一种解析器都是一个运行环境,不但允许JS定义各种数据结构,进行各种计算,还允许JS使用运行环境提供的内置对象和方法做一些事情。例如运行在浏览器中的JS的用途是操作DOM,浏览器就提供了docum

- java-64.寻找第N个丑数

bylijinnan

java

public class UglyNumber {

/**

* 64.查找第N个丑数

具体思路可参考 [url] http://zhedahht.blog.163.com/blog/static/2541117420094245366965/[/url]

*

题目:我们把只包含因子

2、3和5的数称作丑数(Ugly Number)。例如6、8都是丑数,但14

- 二维数组(矩阵)对角线输出

bylijinnan

二维数组

/**

二维数组 对角线输出 两个方向

例如对于数组:

{ 1, 2, 3, 4 },

{ 5, 6, 7, 8 },

{ 9, 10, 11, 12 },

{ 13, 14, 15, 16 },

slash方向输出:

1

5 2

9 6 3

13 10 7 4

14 11 8

15 12

16

backslash输出:

4

3

- [JWFD开源工作流设计]工作流跳跃模式开发关键点(今日更新)

comsci

工作流

既然是做开源软件的,我们的宗旨就是给大家分享设计和代码,那么现在我就用很简单扼要的语言来透露这个跳跃模式的设计原理

大家如果用过JWFD的ARC-自动运行控制器,或者看过代码,应该知道在ARC算法模块中有一个函数叫做SAN(),这个函数就是ARC的核心控制器,要实现跳跃模式,在SAN函数中一定要对LN链表数据结构进行操作,首先写一段代码,把

- redis常见使用

cuityang

redis常见使用

redis 通常被认为是一个数据结构服务器,主要是因为其有着丰富的数据结构 strings、map、 list、sets、 sorted sets

引入jar包 jedis-2.1.0.jar (本文下方提供下载)

package redistest;

import redis.clients.jedis.Jedis;

public class Listtest

- 配置多个redis

dalan_123

redis

配置多个redis客户端

<?xml version="1.0" encoding="UTF-8"?><beans xmlns="http://www.springframework.org/schema/beans" xmlns:xsi=&quo

- attrib命令

dcj3sjt126com

attr

attrib指令用于修改文件的属性.文件的常见属性有:只读.存档.隐藏和系统.

只读属性是指文件只可以做读的操作.不能对文件进行写的操作.就是文件的写保护.

存档属性是用来标记文件改动的.即在上一次备份后文件有所改动.一些备份软件在备份的时候会只去备份带有存档属性的文件.

- Yii使用公共函数

dcj3sjt126com

yii

在网站项目中,没必要把公用的函数写成一个工具类,有时候面向过程其实更方便。 在入口文件index.php里添加 require_once('protected/function.php'); 即可对其引用,成为公用的函数集合。 function.php如下:

<?php /** * This is the shortcut to D

- linux 系统资源的查看(free、uname、uptime、netstat)

eksliang

netstatlinux unamelinux uptimelinux free

linux 系统资源的查看

转载请出自出处:http://eksliang.iteye.com/blog/2167081

http://eksliang.iteye.com 一、free查看内存的使用情况

语法如下:

free [-b][-k][-m][-g] [-t]

参数含义

-b:直接输入free时,显示的单位是kb我们可以使用b(bytes),m

- JAVA的位操作符

greemranqq

位运算JAVA位移<<>>>

最近几种进制,加上各种位操作符,发现都比较模糊,不能完全掌握,这里就再熟悉熟悉。

1.按位操作符 :

按位操作符是用来操作基本数据类型中的单个bit,即二进制位,会对两个参数执行布尔代数运算,获得结果。

与(&)运算:

1&1 = 1, 1&0 = 0, 0&0 &

- Web前段学习网站

ihuning

Web

Web前段学习网站

菜鸟学习:http://www.w3cschool.cc/

JQuery中文网:http://www.jquerycn.cn/

内存溢出:http://outofmemory.cn/#csdn.blog

http://www.icoolxue.com/

http://www.jikexue

- 强强联合:FluxBB 作者加盟 Flarum

justjavac

r

原文:FluxBB Joins Forces With Flarum作者:Toby Zerner译文:强强联合:FluxBB 作者加盟 Flarum译者:justjavac

FluxBB 是一个快速、轻量级论坛软件,它的开发者是一名德国的 PHP 天才 Franz Liedke。FluxBB 的下一个版本(2.0)将被完全重写,并已经开发了一段时间。FluxBB 看起来非常有前途的,

- java统计在线人数(session存储信息的)

macroli

javaWeb

这篇日志是我写的第三次了 前两次都发布失败!郁闷极了!

由于在web开发中常常用到这一部分所以在此记录一下,呵呵,就到备忘录了!

我对于登录信息时使用session存储的,所以我这里是通过实现HttpSessionAttributeListener这个接口完成的。

1、实现接口类,在web.xml文件中配置监听类,从而可以使该类完成其工作。

public class Ses

- bootstrp carousel初体验 快速构建图片播放

qiaolevip

每天进步一点点学习永无止境bootstrap纵观千象

img{

border: 1px solid white;

box-shadow: 2px 2px 12px #333;

_width: expression(this.width > 600 ? "600px" : this.width + "px");

_height: expression(this.width &

- SparkSQL读取HBase数据,通过自定义外部数据源

superlxw1234

sparksparksqlsparksql读取hbasesparksql外部数据源

关键字:SparkSQL读取HBase、SparkSQL自定义外部数据源

前面文章介绍了SparSQL通过Hive操作HBase表。

SparkSQL从1.2开始支持自定义外部数据源(External DataSource),这样就可以通过API接口来实现自己的外部数据源。这里基于Spark1.4.0,简单介绍SparkSQL自定义外部数据源,访

- Spring Boot 1.3.0.M1发布

wiselyman

spring boot

Spring Boot 1.3.0.M1于6.12日发布,现在可以从Spring milestone repository下载。这个版本是基于Spring Framework 4.2.0.RC1,并在Spring Boot 1.2之上提供了大量的新特性improvements and new features。主要包含以下:

1.提供一个新的sprin