JTAG基本介绍

JTAG

1. JTAG接口形式

JTAG作为一项国际标准测试协议(IEEE1149.1兼容),主要用于芯片内部测试和调试。目前的DSP、FPGA、ARM、部分单片机等主流芯片均支持JTAG协议。标准的JTAG接口是20Pin,但JTAG实际使用的只有4根信号线,再配合电源、地。目前常见的各种接口形式(20pin、14pin、10pin):

2. JTAG标准介绍

JTAG的基本原理是在器件内部定义一个TAP(Test Access Port)(测试访问口)通过专用的JTAG测试工具对内部节点进行测试。TAP是Test Access Port(测试访问端口)的缩写,是芯片内部一个通用的端口,通过TAP可以访问芯片提供的所有数据寄存器(DR)和指令寄存器(IR),对整个TAP的控制是通过TAP控制器(TAP Controller)完成的。

JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。JTAG引脚的定义如下列表所示:

- TCK:TCK在IEEE1149.1标准里是强制要求的。TCK为TAP的操作提供了一个独立的、基本的时钟信号,TAP的所有操作都是通过这个时钟信号来驱动的;

- TMS:TMS在IEEE1149.1标准里是强制要求的。TMS信号在TCK的上升沿有效,用来控制TAP状态机的转换。通过TMS信号,可以控制TAP在不同的状态间相互转换;

- TDI:TDI在IEEE1149.1标准里是强制要求的。TDI是数据输入的接口,所有要输入到特定寄存器的数据都是通过TDI接口一位一位串行输入的(由TCK驱动);

- TDO:TDO在IEEE1149.1标准里是强制要求的。TDO是数据输出的接口,所有要从特定的寄存器中输出的数据都是通过TDO接口一位一位串行输出的(由TCK驱动);

- TRST:可选项,TRST可以用来对TAP控制器进行复位(初始化)。因为通过TMS也可以对TAP控制器进行复位(初始化),所以有四线JTAG与五线JTAG之分;

- RTCK:可选项,由目标端反馈给仿真器的时钟信号,用来同步TCK信号的产生,不使用时直接接地;

- nSRST:可选性与目标板上的系统复位信号相连,可以直接对目标系统复位。同时可以检测目标系统的复位情况,为了防止误触发,应在目标端是哪个加上适当的上拉电阻;

3. JTAG功能作用

通过JTAG连接,可以完成如下的功能:

- 对所有串接在一起的IC进行引脚连接性测试,确认PCB是否焊接正常;

- 对CPU、DSP、FPGA等进行调试;

- 通过JTAG对FPGA进行编程。

进行引脚连接测试的JTAG用法如下图所示,各个芯片引脚的连通状态可以一次串接通信到PC的TDO引脚中。

按照菊花链方式串接调试的JTAG用法如下图所示,多个串接在一起的CPU和FPGA都能够一起进行调试和测试。

4. JTAG的调试原理

上图可以看出JTAG的调试原理:

所有调试芯片的IR寄存器串接在一起,然后进行串行移位,最后,所有数据都进入到JTAG口的TDO中;PC通过对TDO数据的串并转换,获得每个CPU、DPS或FPGA的内部寄存器状态。

PC将需要写入CPU、DSP或FAPG的数据通过并串转换放置到TDI总线上,最后通过状态移位到规定的CPU寄存器上,最后通过TMS制定生效时刻。

TCK就是TDI和TDO的移位时钟,而TMS则是控制指令。

因此,JTAG通过一个标准状态机就能够将CPU/DSP/FPGA的内部状态查明,也能改变内部寄存器内容,这也是一种状态控制原理。在1990年之前,JTAG的状态机基本是由各个厂商自行定义的,但后来出现的IEEE1149.1标准对状态转移过程进行了标准化。在某种意义上讲,JTAG的状态机实现过程是最佳的FSM学习对象。

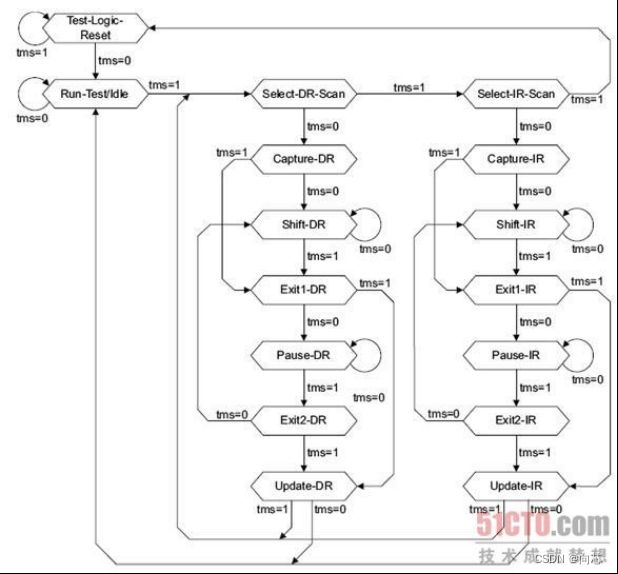

5. TAP控制器的状态机

TAP是Test Access Port(测试访问端口)的缩写,是芯片内部一个通用的端口,通过TAP可以访问芯片提供的所有数据寄存器(DR)和指令寄存器(IR),对整个TAP的控制是通过TAP控制器(TAP Controller)完成的。

TAP控制器有16个同步状态,控制器的下一个状态TMS信号决定,TMS信号在TCK的上升沿被采样生效。

(1)Test-Logic-Reset测试逻辑复位状态

处于这种状态下,测试逻辑被禁止以允许芯片正常操作,读IDCODE寄存器将禁止测试逻辑。

无论TAP控制器处于何种状态,只要将TMS信号在5个连续的TCK信号的上升沿保持高电平,TAP就将进入Test-Logic-Reset状 态,如果TMS信号一直为高电平,那么TAP将保持在Test-Logic-Reset状态,另外TRST信号也可以强迫TAP进入Test- Logic-Reset状态。

处于Test-Logic-Reset状态的TAP,如果下一个TCK的上升沿时TMS信号处于低电平,那么TAP将被切换到Run-Test-Idle状态。

(2)Run-Test-Idle运行测试空闲状态

Run-Test-Idle是TAP控制器扫描操作空闲状态,如果TMS信号一直处于低电平,那么TAP将保持在TRun-Test-Idle状态。当TMS信号在TCK上升沿处于高电平,TAP控制器将进入Select-DR-Scan状态。

(3)Select-DR-Scan选择数据寄存器扫描状态

Select-DR-Scan是TAP控制器的一个临时状态,边界扫描寄存器BSR保持它们先前的状态。

当TMS信号在下一个TCK上升沿处于低电平,TAP控制器进入Capture-DR状态,一个边界扫描寄存器的扫描操作同时被初始化。

如果TMS信号在下一个TCK上升沿处于高电平,TAP控制器将进入Select-IR-Scan状态。

(4)Capture-DR捕获数据寄存器状态

如果TAP控制器处于Capture-DR状态,且当前指令是SAMPLE/PRELOAD指令,那么边界扫描寄存器BSR在TCK信号的上升沿捕 获输入管脚的数据。如果此时不是SAMPLE/PRELOAD指令,那么BSR保持它们先前的值,另外BSR的值被放入连接在TDI和TDO管脚之间的移 位寄存器中。

处于Capture-DR状态时,指令不会被改变。

如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Exit1-DR状态。如果TMS信号在下一个TCK上升沿处于低电平,则TAP进入Shift-DR状态。

(5)Shift-DR移位数据寄存器状态

在Shift-DR状态下,在每个TCK的上升沿,TDI-移位寄存器-TDO串行通道向右移一位,TDI的数据移入移位寄存器,移位寄存器最靠近TDO的位移到TDO管脚上。

处于Shift-DR状态时,指令不会被改变。

如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Exit1-DR状态。如果TMS信号处于低电平,则TAP一直进行移位操作。

(6)Exit1-DR退出数据寄存器状态1

Exit1-DR是TAP控制器的一个临时状态,如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Update-DR状态;如果TMS信号在下一个TCK上升沿处于低电平,则TAP进入Pause-DR状态。

处于Exit1-DR状态时,指令不会被改变。

(7)Pause-DR暂停数据寄存器状态

Pause-DR状态允许TAP控制器暂时停止TDI-移位寄存器-TDO串行通道的移位操作。

处于Pause-DR状态时,指令不会被改变。

如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Exit2-DR状态;如果TMS信号处于低电平,则TAP一直保持暂停状态。

(8)Exit2-DR退出数据寄存器状态2

Exit2-DR也是TAP控制器的临时状态,如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Update-DR状态,结束扫描操作;如果TMS信号在下一个TCK上升沿处于低电平,则TAP重新进入Shift-DR状态。

处于Exit2-D状态时,指令不会被改变。

(9)Update-DR更新数据寄存器状态

在正常情况下,边界扫描寄存器BSR的值是被锁存在并行输出管脚中,以免在EXTEST或SAMPLE/PRELOAD命令下执行移位操作时改变 BSR的值。当处于Update-DR状态时选择的是BSR寄存器,那么移位寄存器中的值将在TCK的下降沿被锁存到BSR寄存器的并行输出管脚中去。

处于Update-DR状态时,指令不会被改变。

如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Select-DR-Scan状态;如果TMS信号在下一个TCK上升沿处于低电平,则TAP进入Run-Test-Idle状态。

(10)Select-IR-Scan选择指令寄存器扫描状态

Select-IR-Scan是TAP控制器的一个临时状态。

如果TMS信号在下一个TCK上升沿处于低电平,TAP控制器进入Capture-IR状态,一个对指令寄存器的扫描操作同时被初始化。

如果TMS信号在下一个TCK上升沿处于高电平,TAP控制器将进入Test-Logic-Reset状态。

处于Select-IR-Scan状态时,指令不会被改变。

(11)Capture-IR捕获指令寄存器状态

处于Capture-IR状态时,指令寄存器中的值被固定设置成0b0000001,并将它放入连接在TDI与TDO之间的移位寄存器中。

处于Capture-DR状态时,指令不会被改变。

如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Exit1-IR状态;如果TMS信号在下一个TCK上升沿处于低电平,则TAP进入Shift-IR状态。

(12)Shift-IR移位指令寄存器状态

在Shift-IR状态下,在每个TCK的上升沿,TDI-移位寄存器-TDO串行通道向右移一位,JTAG指令从TDI管脚上被逐位移入移位寄存器,而移位寄存器中的0b0000001则被逐位从TDO管脚移出。

处于Shift-IR状态时,指令不会被改变。

如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Exit1-IR状态;如果TMS信号处于低电平,则TAP一直进行移位操作。

(13)Exit1-IR退出指令寄存器状态1

Exit1-IR是TAP控制器的一个临时状态,如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Update-IR状态;如果TMS信号在下一个TCK上升沿处于低电平,则TAP进入Pause-IR状态。

处于Exit1-IR状态时,指令不会被改变。

(14)Pause-IR暂停指令寄存器状态

Pause-IR状态允许TAP控制器暂时停止TDI-移位寄存器-TDO串行通道的移位操作。

处于Pause-IR状态时,指令不会被改变。

如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Exit2-IR状态;如果TMS信号处于低电平,则TAP一直处于暂停状态。

(15)Exit2-IR退出指令寄存器状态2

Exit2-IR也是TAP控制器的临时状态,如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Update-IR状态,结束扫描操作;如果TMS信号在下一个TCK上升沿处于低电平,则TAP重新进入Shift-IR状态。

处于Exit2-D状态时,指令不会被改变。

(16)Update-IR更新指令寄存器状态

处于Update-IR状态时,移位寄存器中的值将在TCK的下降沿被锁存到指令寄存器中,一旦锁存成功,新的指令将成为当前的指令。

如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Select-DR-Scan状态;如果TMS信号在下一个TCK上升沿处于电平,则TAP进入Run-Test-Idle状态。

6. JTAG接口指令集

JTAG接口指令集包含以下常用指令:

(1)EXTEST指令

外部测试指令,必须全为0,TAP强制定义。该指令初始化外部电路测试,主要用于板级互连以及片外电路测试。

EXTEST指令在Shift-DR状态时将扫描寄存器BSR寄存器连接到TDI与TDO之间。在Capture-DR状态时,EXTEST指令将 输入管脚的状态在TCK的上升沿装入BSR中。EXTEST指令从不使用移入BSR中的输入锁存器中的数据,而是直接从管脚上捕获数据。在Update- DR状态时,EXTEST指令将锁存在并行输出寄存器单元中的数据在TCK的下降沿驱动到对应的输出管脚上去。

(2)SAMPLE/PRELOAD指令

采样/预装载指令,TAP强制定义。在Capture-DR状态下,SAMPLE/PRELOAD指令提供一个从管脚到片上系统逻辑的数据流快照, 快照在TCK的上升沿提取。在Update-DR状态时,SAMPLE/PRELOAD指令将BSR寄存器单元中的数据锁存到并行输出寄存器单元中,然后 由EXTEST指令将锁存在并行输出寄存器单元中的数据在TCK的下降沿驱动到对应的输出管脚上去。

(3)BYPASS指令

旁路指令,必须全为1,TAP强制定义。BYPASS指令通过在TDI和TDO之间放置一个1位的旁通寄存器,这样移位操作时只经过1位的旁通寄存 器而不是很多位(与管脚数量相当)的边界扫描寄存器BSR,从而使得对连接在同一JTAG链上主CPU之外的其他芯片进行测试时提高效率。

(4)IDCODE指令

读取CPU ID号指令,TAP强制定义。该指令将处理器的ID号寄存器连接到TDI和TDO之间。

7. 总结

以上主要讲述JTAG的使用和内部工作方式,简单描述了微电子中一些电路设计方式,整个JTAG的关键在于先通过IR地址输入,打开对应的寄存器,在通过DR输入或者读取数据,具体实现需要根据手册中指令的格式输入,才能进入对应寄存器。