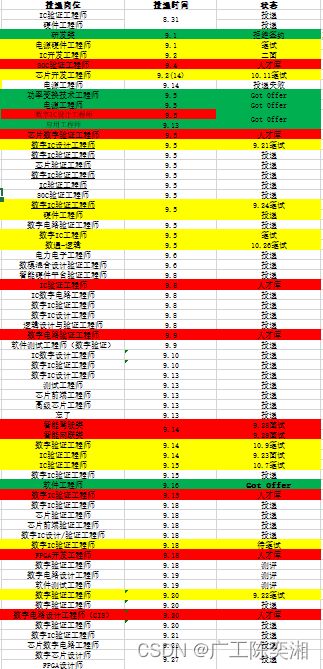

网上IC笔试面试题目与秋招进度(2022.11.5更新)

2022.11.5更新:(IC笔试题目有JL科技、TR半导体、HZW、MX半导体、RSKX)欢迎大家一起讨论题目,也请多多指教弟弟。笔试已经转移到新开帖子了。

目前投递60+,人才库8,offer6拒3签3。

第四阶段的目标是找到一个IC的开发岗位offer,继续往前走。

越努力,越幸运。

BYD(拒绝签约)

广东某双非工科院校,宣讲会当晚电话面试约40mins,主要是对方介绍汽车研究院和自己介绍自己的简历,对着简历一行一行问。三天后在教室现场人事面,通知9:20到,提前十分钟到教室,等到11:20才轮到,面试内容为查户口,期望薪资报了个数也没往下谈,你说什么他就记录什么。两天后通知签约,通知晚上7:00到,到了之后上一场的人还没签完,又等了近半小时才开始讲,教室坐满加站满人,教室外走廊也站了很多人。当场拒绝比亚迪。

待遇:双非硕士级别为F3,底薪10k,绩效0.36,前三个月没绩效,最后也没年终奖,说是利润奖,按21年报的净利润10%除以技术人员数量44318,人均近7k,又不是保证人人都有的。公积金按底薪的5%交,住4人间宿舍。

结论:招牛马,已拒绝。

YST(拒绝后hr保留)

15k*14薪,虽然是1-4个月年终奖,但是刚进去只能是1-2;

公积金按8k*5%交,社保按东莞交三百多;

住单人间月租200或300,吃饭类比学校食堂,东莞松山湖

丑的(GOT OFFER)

一面:天河五星级酒店无领导小组群面,题目为电动汽车设计方案,组员为4华工1暨大1双非的压倒性阵容,很无聊,双一流的学生也是真的会说话,不得不佩服。

测评:当晚收到测评邮件。

二面:视频面,很轻松,面试官还没开摄像头,全程对着自己说话。

签约:整了一天。

待遇:17.5k*14,级别好像是14级,公积金按8k多*7交610左右,住宿单间,其他奖项大约3-5w

CVTE(拒绝签约)

笔试:九月初

一面:电话面,问得没有很深入,半小时,国庆后的第一周

二面:人事面聊聊天,半小时

现场见面:三产在萝岗最边缘,和部门leader了解业务。最后选择拒绝,理由有三方面。首先是业务,做的是空调控制板卡,电机驱动,空调这个行业十年前已经是竞争充分了,个人并不看好这种赛道;其次是薪资,第一年学习阶段绩效拿不满,也就是年终没有3个月,内部调薪一年三次,不是领导评而是同事之间互相评,薪资透明,他说我的薪资已经是倒挂了,那我岂不是两年内基本不用考虑调薪,甚至还可能会被排挤;最后是加班文化,九点后下班,弹性工作制不打卡,相当于随叫随到,他说基本保证双休。和美的比起来性价比就低很多了。

待遇:17k*13+年终3个月,公积金按月薪-1k2住房补贴的5%交,吃免费无住宿,年调薪2-5次(250元/档,封顶8档),加班是文化,宣讲会的时候放了张部门全部人半夜四点下班的合照,有个朋友在里面天天九点后下班。

SY半导体(GOT OFFER)

10.28早上十点打电话约面试,下午三点半面试,五点半hr沟通发offer,不到八小时拿下。

珠海,应用工程师,保底18k*16(按绩效可多最多2个月的)+12w签字费三年均匀发,公积金按工资18k*12%。

长期激励就不展开了,类似丑的那些项目奖专利奖什么的,要IPO也可能有原始股。

住宿:吃食堂,申请珠海的人才公寓1k多,这方面没有丑的方便。

ZH电源(GOT OFFER)

投递:9月初

一面:十月中

二面:一面之后一星期

20k*14,年终奖看绩效,不一定是2,公积金按工资65%交5%,一日两顿餐补30,夜宵免费,朝九晚六还双休,坐标深圳。

目录

BYD(拒绝签约)

YST(拒绝后hr保留)

丑的(GOT OFFER)

CVTE(拒绝签约)

SY半导体(GOT OFFER)

ZH电源(GOT OFFER)

APB和AHB协议 ,如何完成APB与AHB之间的握手?

AHB怎么完成burst传输?

在AHB到APB bridge的测试点?

项目中FIFO的测试点?FIFO的深度是多少?

你是如何判别fifo的空满?

是否进行覆盖率的收集 ,都有哪些覆盖率,代码覆盖率又包含哪些内容?

你所做项目的测试点有什么?

是否用到了断言覆盖率?

寄存器和锁存器的区别

什么是建立时间和保持时间?如果违例怎么办?

跨时钟域应该怎么处理

多线程的同步调度方法有哪些?

接口和时钟块的功能是什么?

怎么编写测试用例?

断言中$past的用法

rand 和randc的区别?

MOORE 与 MEELEY状态机的特征?

什么是"线与"逻辑?要实现它,在硬件特性上有什么具体要求?

Verilog HDL中的可综合、不可综合的东西有哪些?

对于同步fifo,每100个cycle可以写入80个数据,每10个cycle可以读出8个数据,fifo的深度至少为?

JTAG接口信号及功能是什么?

约束有几种形式?

get_next_item()和try_next_item()有什么区别?

如何关闭约束?

如何控制一个约束块?

如何控制对象的所有约束?

类的public、protected和local的区别?

phase中的domain概念?

FPGA、CPLD、ASIC、SOC、SOPC是什么?

什么是Clock Jitter和Clock Skew,这两者有什么区别?

反相器的速度与哪些因素有关?

什么是转换时间(Transition Time)和传播延迟(Propagation Delay)?

相同面积的cmos与非门和或非门哪个更快?

FPGA与ASIC设计流程的区别?

FPGA芯片内有哪两种存储器资源?

FPGA设计中如何使用时钟?

FPGA设计如何实现同步时序电路的延时?

什么是竞争与冒险?怎样判断?如何消除?

UVM的优势是什么?为什么要用UVM?

说一下ref类型,你用到过吗?

component和object的区别?item是哪种?

如何保证验证的完备性?

break;continue;return的含义

sequencer的仲裁特性set_arbitration和锁定机制(lock和grab)

virtual sequence和virtual sequencer中virtual的含义

为什么要分开实现sequence、sequencer、driver?

什么是field_automation机制和objection机制?

你搭建的验证平台为什么要用寄存器?

APB和AHB协议 ,如何完成APB与AHB之间的握手?

通过一个AHB to APB bridge进行握手

AHB怎么完成burst传输?

首先看burst的类型是single、wrap还是incr,single就是单个传输,地址阶段从总线拿到地址和控制信号后,在数据阶段wdata拉高等待ready拉高完成传输。

incr表示地址不循环增量,每传输一个数据相应的地址就递增;wrap表示地址循环,具体看是多少拍为一个循环,如果是wrap4,数据位宽size是8,那么就是从当前地址开始进行增量为4、地址范围32的地址循环传输。

在AHB到APB bridge的测试点?

APB的测试点如下:

指令测试(覆盖组cg_apb_command,收集读写和idle三个指令);

传输时间测试(覆盖组cg_apb_trans_timing_group,看传输多个数据的sel信号的翻转情况,1次读写要2个clk,sel传送1个数据要维持2个clk为高后拉低,传送2个数据要维持2*2个clk为高后拉低,以此类推,burst test一共有4,8,16,32个数据;enable信号在连续读写时就是0101一高一低,如果是单个single的,就可能是1后拉低[*2:10]);

读写顺序的测试(覆盖组cg_apb_write_read_order_group,采集write信号,读为1写为0,共四种读写顺序)

项目中FIFO的测试点?FIFO的深度是多少?

根据硬件设计v文件sync_dff_fifo,深度是32

你是如何判别fifo的空满?

根据读写指针来判断fifo空满。

空标志:读指针追上写指针,两个指针所有位相同

满标志:写时针写满一圈,标志位置1,然后追上读指针,就是第一位相反,后面位相反

是否进行覆盖率的收集 ,都有哪些覆盖率,代码覆盖率又包含哪些内容?

是的。覆盖率的收集分为几块:首先是APB覆盖率的收集,一共测试了三个测试点,指令测试、传输时间测试、读写顺序的测试。

其次是

你所做项目的测试点有什么?

是否用到了断言覆盖率?

是的。断言覆盖率编写在覆盖组的后面。

1 检查地址中有无不定值:在sel拉高时(交叠蕴含|→)用系统函数$isunknown(addr)评估地址是否含x和z,如果是则返回1

2 检查sel拉高后下一拍enable是否拉高:用$rose(sel)和非交叠蕴含|⇒ $rose(enable)

3 检查enable拉高后下一拍是否被拉低:enable要拉低需要完成数据传输,所以在enable和ready都为高时评估|→$fell(enable)

4 检查wdata在传输数据时是否稳定:传输数据的两个clk的序列描述出来((psel && !penable) ##1 (psel && penable)),则评估$stable(wdata)

5 检查地址是否在两次连续传输保持稳定:定义两个地址变量,在enable为高时存入第一个地址,下一拍进入setup状态时调用$past(addr)存入第二个地址,然后评估两个地址是否一致

6 同上,检查write是否稳定:

7 检查读操作时rdata是否稳定:读操作write为低、ready为高、enable为高时,评估rdata是否稳定$stable()

8 检查不连续传输的write序列是否正确:enable拉高后评估write是否贯穿到下一次传输,由于不连续,enable拉高后的下一拍是idle,然后进入下一次传输,所以序列是$rose(penable) |-> pwrite throughout (##1 (!penable)[*2] ##1 penable[=1])

9 检查连续传输的write序列是否正确:enable拉高后评估write是否贯穿两拍后enable为高这个序列

10 检查连续读写的序列是否正确:连续读写时,write高2拍低2拍,enable0101,由于是连续写读,地址也要保持一致

11 连续两次写后读:在10的基础上复制多一次,write改为!write

12 13 不连续读,连续读,和9、10的区别就是write为!write

14 连续读写读:也是同理

寄存器和锁存器的区别

寄存器:寄存器的功能是存储二进制代码,它是由具有存储功能的触发器组合起来构成的。一个触发器可以存储1位二进制代码,故存放n位二进制代码的寄存器,需用n个触发器来构成。

锁存器:可以把信号暂存以维持某种电平状态。锁存器的最主要作用是缓存,其次完成高速的控制器与慢速的外设的不同步问题,再其次是解决驱动的问题,最后是解决一个 I/O 口既能输出也能输入的问题。锁存器是利用电平控制数据的输入。

寄存器是同步时钟控制,而锁存器是电位信号控制。锁存器一般由电平信号控制,属于电平敏感型。寄存器一般由时钟信号信号控制,属于边沿敏感型。

寄存器的输出端平时不随输入端的变化而变化,只有在时钟有效时才将输入端的数据送输出端(打入寄存器),而锁存器的输出端平时总随输入端变化而变化,只有当锁存器信号到达时,才将输出端的状态锁存起来,使其不再随输入端的变化而变化

什么是建立时间和保持时间?如果违例怎么办?

在时钟采样沿之前,数据必须保持稳定的时间,该时间量称为建立时间

在时钟采样沿之后,数据必须保持稳定的最短时间,称为保持时间。

建立时间余量(Setup Slack): 要求数据到达时间和数据实际到达时间的差值。

保持时间余量(Hold Slack): 数据实际结束位置和要求数据结束位置的差值。

数据从Reg1到Reg2,理想情况下采样沿到达Reg2时,数据的中间位置到达Reg2的数据端,这样出现最优的建立时间和保持时间,此时采样的数据也是最稳定的,如果时钟早到或者数据早到就会产生余量,严重的情况下就会产生时序违例。

在实际的数据传输中器件和线路均会存在延迟。

如果数据在时钟上升沿的建立保持时间内{latch edge-setup,latch edge+hold time}发生跳变,则会产生亚稳态输出,即输出值在短时间内处于不确定态,有可能是1,有可能是0,也可能什么都不是,处于中间态。可能数据丢失,无法采到预期中的信号。

跨时钟域应该怎么处理

常见的跨时钟域信号处理方法

-

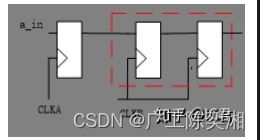

两级DFF同步器(要求信号频率较低,维持比两个时钟域的多个周期还要久),就是打两拍

单比特信号处理通常采用两级DFF串联进行同步,从时钟域A(CLKA)传过来的信号a_in, 直接用时钟域CLKB采用很容易产生亚稳态,用两级DFF敲过后再使用就可以把亚稳态概率降到一个合理的值。

为什么是两级?这里有一个平均失效间隔时间MTBF(Mean Time Between Failure)的考虑。MTBF时间越长,出现亚稳态的概率就越小,但是也不能完全避免亚稳态。注意采样时钟频率越高,MTBF可能会迅速减小。

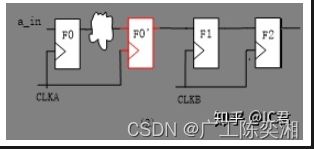

由于组合逻辑电路各个输入信号的不一致性以及组合逻辑内部路径的延时时间不一样,运算后的信号存在毛刺,而我们又无法预先知道CLKB 的上升沿何时会到来,CLKB 采样到的信号就无法预知,这显然不是我们想要的结果。

改进如下:要想CLKB 能采到稳定的信号,时钟域A的信号必须是经过CLKA 敲过,在一个时钟周期内是稳定的信号

-

握手协议

in时钟域的d_in要传到out时钟域,首先将d_in展宽为d_req,经过clk_out打两拍产生d_req_sync,此时取1个周期即可获得跨时钟域的d_out;d_req_sync打两拍clk_in获得d_ack,下一拍d_req就拉低。完成握手。

-

异步FIFO

处理多bit数据的跨时钟域,一般采用异步双口RAM****+格雷码****。

多线程的同步调度方法有哪些?

mailbox:两个线程之间进行数据通信,通过调用put、get、peek函数获取和发送数据

event:两个线程之间的同步运行,通过事件触发和等待进行两个线程间的运行同步

等待:@(evevnt),wait(event.trigger);触发|->

semaphore:对共用资源的访问,通过key的获取和返回实现一个线程对资源的一次访问,调用put和get函数返回和获取key

接口和时钟块的功能是什么?

接口:封装信号,便于提高可复用性;是软硬件之间的交互媒介;还提供时钟块用于测试平台和dut之间的同步、避免竞争。让连接更简洁。

时钟块:做信号的同步和采样。clocking基于时钟周期对信号驱动和采样,tb不再苦恼于如何准确及时地对信号驱动或采样。具体地,自定义采样输入信号采样、输出信号驱动的时间,用来检查建立时间保持时间是否符合

怎么编写测试用例?

主要是编写sequence,在seq的body中根据测试功能的要求编写相应的激励,再通过ref_model和checker判断功能是否实现。

断言中$past的用法

可以追溯过去任意时钟时变量的值,完整的用法如下:

$past(expression1, [, number_of_ticks] [,expression2][, clocking_event]);

number_of_ticks可以指定要追溯多少个clk,默认是1。

rand 和randc的区别?

rand/randc 数据类型(bit) [ 数据:宽度] 数据名1,数据名2;

rand类似放回的抽球,每次随机都在取值范围内随机取一个值;

randc是不放回的抽球,所有可能取的值取完了才会重复取值。

MOORE 与 MEELEY状态机的特征?

Moore 状态机的输出仅与当前状态值有关, 且只在时钟边沿到来时才会有状态变化。 Mealy 状态机的输出不仅与当前状态值有关, 而且与当前输入值有关。

什么是"线与"逻辑?要实现它,在硬件特性上有什么具体要求?

线与逻辑是两个输出信号相连可以实现与的功能。

一般TTL门输出端并不能直接并接使用,否则这些门的输出管之间由于低阻抗形成很大的短路电流(灌电流),而烧坏器件。

在硬件上,要用集电极开路门oc门或三态门TS门来实现,同时在输出端口应加一个上拉电阻。oc门就是集电极开路门,od门是漏极开路门。

Verilog HDL中的可综合、不可综合的东西有哪些?

所有综合工具都支持的结构:always,assign,begin,end,case,wire,tri,aupply0,supply1,reg,integer,default,for,function,and,nand,or,nor,xor,xnor,buf,not,bufif0,bufif1,notif0,notif1,if,inout,input,instantitation,module,negedge,posedge,operators,output,parameter。 所有综合工具都不支持的结构:time,defparam,$finish,fork,join,initial,delays,UDP,wait。 有些工具支持有些工具不支持的结构:casex,casez,wand,triand,wor,trior,real,disable,forever,arrays,memories,repeat,task,while。

对于同步fifo,每100个cycle可以写入80个数据,每10个cycle可以读出8个数据,fifo的深度至少为?

写时钟每B个周期写入A个数据,读时钟每Y个周期读出X个数据。

考虑100个周期写入80个,先写后读,一共160个数据操作。

深度=连续操作数据数160(1-(读出数据X/读出数据所需时间Y )(读时钟频率/写时钟频率))

JTAG接口信号及功能是什么?

JTAG接口(Joint Test Action Group,联合测试工作组),是一种国际标准测试协议,主要用于芯片内部测试。

接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出 线。

功能:下载软件到flash里;debug;边界扫描,可以访问芯片内部的信号逻辑状态、引脚状态

约束有几种形式?

- 权重约束:随机变量名 dist {指定的数:=权重1,[范围1]:=权重2}

- :=表示范围内的每个数各自占有权重2;:/表示范围内的每个数平分权重2

- 条件约束:if else和→ (case);满足前面条件后触发case

- 范围约束:inside{[min, max]}; 也可以用min

get_next_item()和try_next_item()有什么区别?

get_next_item()是一个阻塞调用,直到存在可供驱动的sequence item为止,并返回指向sequence item的指针。

try_next_item()是非阻塞调用,如果没有可供驱动的sequence item,则返回空指针。

如何关闭约束?

通过内建函数constraint_mode(0)关闭默认范围的约束块;constraint_mode(1)是打开约束。 可以用soft关键字修饰特定的约束语句,这样既可以让变量在一般的情况下取默认值,也可以直接给变量赋默认值范围外的取值。

如何控制一个约束块?

handle.constrain.constraint_mode(); 注意handle是句柄,constrain是具体约束的名称

如何控制对象的所有约束?

handle.constraint_mode(); 注意handle是对象的句柄

类的public、protected和local的区别?

如果没有指明访问类型,那么成员的默认类型是public,子类和外部均可以访问成员。

如果指明了访问类型是protected,那么只有该类或者子类可以访问成员,而外部无法访问。

如果指明了访问类型是local,那么只有该类可以访问成员,子类和外部均无法访问。

phase中的domain概念?

Domain是用来组织不同组件,实现独立运行的概率。默认情况下,UVM phase机制的9个phase属于 common_domain,run phase的12个小phase属于uvm_domain。例如,如果我们有两个dirver类,默认情况下,两个driver类中的复位phase和 main phase必须同时执行,但是我们可以设置两个driver属于不同的domain,这样两个dirver就是独立运行的了,相当于处于不同的时钟域(只针对12个小phase有效)。

FPGA、CPLD、ASIC、SOC、SOPC是什么?

FPGA:现场可编程门阵列,一般工艺SRAM静态随机存取存储器(易失性),所以要外挂配置芯片。 CPLD:(Complex Programmable Logic Device)复杂可编程逻辑器件,一般工艺Flash(不易失)存储芯片闪存。 ASIC:(Application Specific Integrated Circuit)专用集成电路 SOC:片上系统,系统级芯片,意指它是一个产品,是一个有专用目标的集成电路,其中包含完整系统并有嵌入软件的全部内容。同时它又是一种技术,用以实现从确定系统功能开始,到软/硬件划分,并完成设计的整个过程。 SOPC:片上可编程系统,它是基于FPGA解决方案的SOC片上系统设计技术。它将处理器、l/O 口、存储器以及需要的功能模块集成到一片FPGA 内,构成一个可编程的片上系统。

什么是Clock Jitter和Clock Skew,这两者有什么区别?

时钟抖动(Clock Jitter):指芯片的某一个给定点上时钟周期发生暂时性变化,使得时钟周期在不同的周期上可能加长或缩短。

时钟偏移(Clock Skew):是由于布线长度及负载不同引起的,导致同一个时钟信号到达相邻两个时序单元的时间不一致。

区别:Jitter是在时钟发生器内部产生的,和晶振或者PLL内部电路有关,布线对其没有影响。Skew是由不同布线长度导致的不同路径的时钟上升沿到来的延时不同。

锁相环 (PLL) 是一种反馈电路,旨在允许一个电路板将其板上时钟相位与外部时序信号同步。 PLL 电路的工作原理是将外部信号的相位与压控晶体振荡器 (VCXO) 产生的时钟信号的相位进行比较。

反相器的速度与哪些因素有关?

- 电容(负载电容、自载电容、连线电容)较小,漏端扩散区的面积应尽可能小。输入电容要考虑:(1)Cgs 随栅压而变化(2)密勒效应(3)自举效应

- 加大晶体管的尺寸(驱动能力),使晶体管的等效导通电阻(输出电阻)较小。但这同时加大自载电容和负载电容(下一级晶体管的输入电容)。

- 提高电源电压,提高电源电压可以降低延时,即用功耗换取性能但超过一定程度后改善有限。电压过高会引起可靠性问题(氧化层击穿、热电子等)。

什么是转换时间(Transition Time)和传播延迟(Propagation Delay)?

上升时间:从10%Vdd上升到90%Vdd的时间,下降时间L从90%Vdd下降到10%dd的时间。上升时间和下降时间统称为Transition Time,也有定义为20%到80%。

Propagation Delay(传播延时):在输入信号变化到50%Vdd到输出信号变化到50%Vdd之间的时间。

相同面积的cmos与非门和或非门哪个更快?

电子迁移率是空穴的2.5倍(在硅基CMOS工艺中),运算就是用这些大大小小的MOS管驱动后一级的负载电容,翻转速度和负载大小一级前级驱动能力相关。为了上升延迟和下降延迟相同,PMOS需要做成NMOS两倍多大小;

载流子的迁移率,对PMOS而言,载流子是空穴;对NMOS而言,载流子是电子;

PMOS采用空穴导电,NMOS采用电子导电,由于PMOS的载流子的迁移率比NMOS的迁移率小,所以,同样尺寸条件下,PMOS的充电时间要大于NMOS的充电时间长,在互补CMOS电路中,与非门是PMOS管并联,NMOS管串联,而或非门正好相反,所以,同样尺寸条件下,与非门的速度快,所以,在互补CMOS电路中,优先选择与非门。

FPGA与ASIC设计流程的区别?

首先我们要清楚FPGA的基本单元是LUT,而ASIC的基本单元是寄存器;

对于FPGA:首先要进行模块划分,然后编写RTL代码,进行RTL仿真,综合后将生成的网表文件在FPGA上实现,也就是布局布线,该步骤完成后进行STA,没有问题的话就生成bit流文件,将bit流文件烧录到FPGA开发板上进行板级调试;

对于ASIC:模块划分、RTL设计、验证、综合、STA、形式验证、布局规划、DRC设计规则检查、时钟树综合、生成GDSII文件。

FPGA芯片内有哪两种存储器资源?

BLOCK RAM和分布式RAM(由LUT配置成的内部存储器)。

BLOCK RAM:由一定数量固定大小的存储块构成,不占用额外的逻辑资源,速度快,使用时消耗的BLOCK RAM资源是其块大小的整数倍。用很小的物理空间存储了大量的数据。

分布式distribution RAM:用逻辑部分里的LUT搭建,搭建大小相当的存储器需要用到大量的LUT,占用更大的面积,实现的存储效果还受到逻辑和布线延迟造成的时序性能的影响。一般用来实现小存储器,提高资源利用率,获得更灵活的布局。

LUT(look up table查找表),在FPGA中用LUT实现组合逻辑电路的功能,延迟是固定的,组合逻辑的功能由输入决定不再和复杂度有关。

FPGA设计中如何使用时钟?

FPGA芯片有固定的时钟路径可以有效减少时钟抖动和偏差;不允许对时钟进行逻辑操作来实现对时钟的相移和变频,这样做会增加时钟抖动和偏差,有毛刺。

正确的做法是利用FPGA芯片自带的CMT时钟管理器PLL、DLL、DCM,或者把逻辑转换到触发器的D输入。

PLL(phase lock loop)锁相环,可用于时钟倍频、分频、调节相位,不能动态调整相位

DCM的核心是DLL(delay locked loop),是数字模块,可以产生不同相位的时钟、分频、倍频、相位动态调整等,但是精度不高

FPGA设计如何实现同步时序电路的延时?

异步电路通过加buffer、两级与非门等实现延时,这不适合同步电路。

同步电路中对于比较大和特殊要求的延时,要通过高速时钟产生计数器,通过计数器控制延时;对于比较小的延时可以通过触发器打一拍。

什么是竞争与冒险?怎样判断?如何消除?

竞争:在组合逻辑电路中,某一输入变量经过不同途径转播后到达电路中某一汇合点的时间有先后。

冒险:由于竞争而使电路输出发生瞬时错误的现象,也就是由竞争产生的毛刺。

如何消除:加滤波电容,消除毛刺的影响;加选通信号避开毛刺;增加冗余项消除逻辑冒险。

UVM的优势是什么?为什么要用UVM?

UVM的主要优势在于复用性,UVM是对SV的一些封装,在搭建tb过程中一些可重复性和重要的工作进行封装,使得搭建tb的速度更快。

说一下ref类型,你用到过吗?

ref参数类型是引用。向子程序传递数组时应尽量使用ref获取最佳性能,如果不希望子程序改变数组的值就使用const ref类型。

component和object的区别?item是哪种?

object——report_object——component,component是object派生出来的,其phase机制和树形结构是object没有的。

在UVM中不仅需要component这种较为复杂的类进行tb的层次化搭建,也需要object这种基础类进行tb的事务搭建和环境配置。

object——transaction——sequence_item,item是object类。

如何保证验证的完备性?

首先不可能百分之百完备,即遍历所有信号的组合,既不经济也不现实;

只能通过多种验证方法一起验证尽可能减少潜在风险。

验证流程:IP级验证,子系统级验证,SOC级验证;还有UPF验证、FPGA原型验证等多种手段。

前端走完每一个阶段都需要跟设计以及系统一起review验证功能点、测试用例、特殊情况下的波形。

后端也会做一些检查:STA、formality、DFM、DRC检查,也会插入一些DFT逻辑供流片回来测试用。流片回来后进行测试,有些bug可以通过软件规避,有些不能规避,只能重新流片。

break;continue;return的含义

break语句结束整个循环;continue结束本次循环执行下一次循环;return终止函数的执行并返回函数的值。

sequencer的仲裁特性set_arbitration和锁定机制(lock和grab)

sequencer的仲裁特性用于多个seq同时挂载到sequencer上时通过特定seq的item

利用uvm_sequencer::set_arbitration(UVM_SEQ_ARB_TYPE val)设置仲裁模式

UVM_SEQ_ARB_TYPE有:fifo,random,及其strict,weighted,user

- UVM_SEQ_ARB_FIFO:默认模式,按照fifo先进先出依次授权,与seq优先级无关

- UVM_SEQ_ARB_WEIGHTED:对不同seq的发送请求,按照优先级权重随机授权

- UVM_SEQ_ARB_RANDOM:不同的请求会被随机授权,无视抵达顺序和优先级

- UVM_SEQ_ARB_STRICT_FIFO:按照优先级和抵达顺序依次授权

- UVM_SEQ_ARB_STRICT_RANDOM:按照最高优先级随机授权

- UVM_SEQ_ARB_USER:用户自定义仲裁方法user_priority_arbitration()

lock()和unlock()可以为sequence提供排外的访问权限,前提是该seq获得了sequencer的授权,获得授权后只有该seq主动解锁unlock才会释放权限。lock是阻塞任务,只有获得了权限才会返回。

grab()和ungrab()可以为sequence提供排外的权限,只需要在sequencer的下一次授权周期就可以无条件拿到授权,唯一可以阻止的只有还没释放权限的lock或grab的sequence

sequence结束前必须释放权限,否则sequencer会进入死锁状态。

virtual sequence和virtual sequencer中virtual的含义

其sequencer不会传递item也不会和driver连接,只是一个协调各个sequencer的中央路由器,实现所有sequencer的调度和复用。

virtual seq可以组织不同sequencer的seq群落

为什么要分开实现sequence、sequencer、driver?

使用SV搭建验证环境搭建时,一开始是用driver进行数据的转换、发送,或者多个generator产生数据,复用性差且代码臃肿。

分开实现的目的是分而治之,独立运作,提高复用性。item是载着数据的货车,sequence是item运输的道路,sequencer由于有仲裁机制,选择通往哪条sequence,driver只负责货物的发送

什么是field_automation机制和objection机制?

域的自动化宏注册之后可以直接调用数据处理函数copy、compare、print等函数,无需自定义,简化了验证平台的搭建。

objection机制

你搭建的验证平台为什么要用寄存器?

寄存器是模块间交互的窗口,通过读寄存器的值来观察模块的运行状态,通过写寄存器的值来控制模块的配置和功能。如果不能保证寄存器的读写正确,那后面的dut是否正确就没有意义了,寄存器的验证应该放在首要位置。

利用寄存器模型来测试验证寄存器,通过前门或者后门访问去控制dut的寄存器,使其按我们需要运行。也可以用UVM寄存器模型的内建序列去测试寄存器。