面积结构设计概念总结-FPGA学习笔记(七)

文章目录

-

-

-

- 1.1 折叠流水线

- 1.2 基于控制的逻辑复用

- 1.3 资源共享

- 1.4 复位对面积的影响

-

- 1.4.1 无复位的资源

- 1.4.2 无置位的资源

- 1.4.3 无同步复位的资源

- 1.4.4 复位RAM

- 1.5 小结

- 参考文档

-

-

面积是数字设计的主要物理特性之一,讨论通过正确的拓扑结构减少面积的方法。针对面积的拓扑是尽可能最大程度的复用逻辑资源,设计更多追求总设计的提高,面积优化常常以流量(速度)为代价。

1.1 折叠流水线

当拆开环路产生流水线,会占用较多资源保存中间数值,并行的运行需要复制计算结构,都会增加面积。折叠流水线使得逻辑资源可以重用,面积最小化。

对于A*B乘法器运算,在错误示范中每个时钟产生一个新的乘积,乘法器本身是很长的逻辑链,添加中间寄存器层次,时滞小,但有明显的流水线。在正确示范中,可以用一系列的移位和加操作把乘法折叠,不需要对通过乘法器顺序进行专门的控制,简单依靠一个计数器确定停止移位和相加。

错误示范:

module mult8(

output [7:0] product,

input [7:0] a,b,

input clk);

reg [15:0] prod16;

assign product=prod16[15:8];

always @(posedge clk)

prod16 <= a*b ;

endmodule

正确示范:

module mult8(

output done,

output reg [7:0] product,

input [7:0] a,b,

input clk,

input start);

reg [4:0] multcounter;//counter for number of shift/adds

reg [7:0] shifta,shiftb;//shift register for a,b

wire adden ; //enable addition

assign adden = shiftb[7]&!done;

assign done = multcounter[3];

always @(posedge clk) begin

//increment multiply counter for shift/add ops

if(start) multcounter <= 0;

else if(!done) multcounter <= multcounter+1;

//shift register for b

if(start) shiftb <= b;

else shiftb <= {shiftb[6:0],1'b0};

//shift register for a

if(start) shifta <= a;

else shifta <= {shifta[7],shifta[7:1]};

//calculate multiplication

if(start) product <= 0;

else if(adden) product <= product+shifta;

end

endmodule

1.2 基于控制的逻辑复用

共享逻辑资源有时要求专门的控制电路决定哪些元件是到特定结构的输入,当共享逻辑比控制逻辑更大时,控制可以直接用来逻辑复用。有时可能通过添加状态机增加控制逻辑,但增加控制逻辑占用面积比起共享逻辑减少面积就微不足道。

1.3 资源共享

高层次的结构资源共享,不同的资源在横跨不同的功能范围共享,功能块可以在设计的其他部分或者在不同的模块利用,就可以利用。

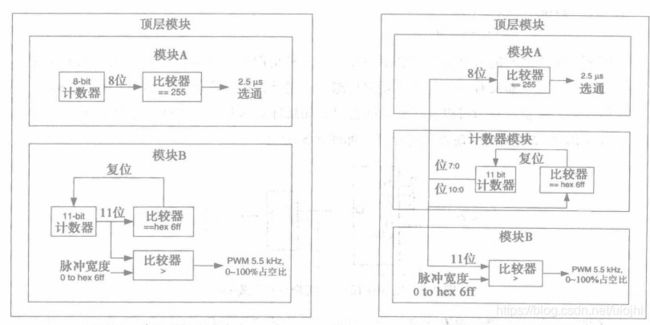

可以以系统计数器举例,一般如定时器、序列发生器和状态机等设计过程都会用到计数器,如果将计数器集中到更高的层次,分配到多个功能模块。

对于面积是主要要求的紧凑设计,搜索 在其他模块中有类似计数部件的资源,可以提取出来放到层次上的全局位置,在多个功能范围之间共享。

1.4 复位对面积的影响

对面积的第一个影响为每个DFF定义全局的置位/复位条件有关。一些功能按照FPGA的细粒度结构来优化,把复位接到每个同步元件可能引起综合和映射工具把逻辑放进粗粒度实现。

1.4.1 无复位的资源

同步复位:

Always @(posedge iclk)

if(!ireset) sr <= 0;

else sr <= {sr[14:0],idat};

无复位:

Always @(posedge iclk)

else sr <= {sr[14:0],idat};

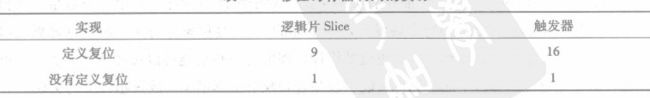

实现之间差别并不明显,区别只在于有没有定义逻辑0的复位状态,如果利用FPGA内置移位寄存器资源的优势,可以做直接映射的编码。设计中定义了复位,就只能利用离散触发器来实现。

1.4.2 无置位的资源

类似于上一节提出的问题,内部的资源缺少任何类型的复位置位能力,因此少用复位置位可以尽多的调用内部资源。

上一节复位是寄存器赋值逻辑0,如果赋值逻辑1,即调用置位功能。

1.4.3 无同步复位的资源

高性能的FPGA提供广泛应用范围可利用的内置功能模块。

DSPs和其他多功能资源一般对复位策略的变化是不灵活的。

调用IP使用时,仔细阅读文档,在不影响自定义功能的前提下,符合IP使用规范的调用,可以大幅减少面积的占用。

当利用同步复位时,综合工具能够利用FPGA器件中可用的DSP核,利用与器件不同的复位时,大量的逻辑要产生来实现异步逻辑。

1.4.4 复位RAM

Xilinx的RAM一般采用同步复位,没有明确要求的情况下,采用异步复位产生大量逻辑。

1.5 小结

-

折叠流水线复用逻辑

-

增加控制逻辑调用共享逻辑

-

类似计数部件的资源,放到层次上的全局位置,在多个功能范围之间共享。

-

复位、置位、了解IP对复位的策略

-

当面积是考虑的关键时,尽可能避免利用置位和复位

参考文档

【1】Kilts S . 高级FPGA设计: 结构、实现和优化[M]. 机械工业出版社, 2009.