模拟集成电路设计:Bandgap电路设计及版图实现

模拟集成电路设计

Bandgap电路设计及版图实现

一、目的:

1、熟悉模拟集成电路设计的基本流程,实现Bandgap电路设计;

2、熟悉Linux系统及Cadence Virtuoso icfb设计、仿真软件的使用方法。

二、原理:

1、设计目标:Bandgap设计目标:提供稳定的电压基准:具有一定的绝对精度(例如3%,5%)、温漂系数小(例如20ppm);尽可能大的电源电压范围;尽可能小的静态工作电流;尽可能大的PSRR;尽可能小的输出分布范围和Noise (Flick noise);具有可靠的启动电路;尽可能小的面积。

2、设计要求:

1)设计基本的Bandgap电路结构,提供对温度不敏感的基准电压以及PTAT基准电流,基本电路与工作原理如下:

2)基准电压与电流:

VBG通常在1.2左右,其温度特性包含抛物线型非线性项,设计中令顶点位于常温附近,更高精度要求可采用二次补偿电路。IBG~T,在高温与低温下其值变换较大,若用它直接去偏置其他电路,这一点须特别注意。

3)启动与稳定性:启动方面,这个电路有两个稳定工作点,其中一个是两个支路电流都为0,设计中需加启动电路来避免这个工作点;稳定方面,正、负反馈环路共存,运放输入端需正确连接,保证负反馈强于正反馈。启动电路中的M9要大于M10,使进入正反馈回路的刺激大一些。M6~M8作为MOS RES,其值应保证正常工作后M9,M10关闭。

4)PSRR(电源抑制比):

低频:OPA环路增益保证;高频:输出RC滤波保证。最差点在中间,提高需要:提高环路带宽,与功耗tradeoff,降低RC带宽,与面积tradeoff。

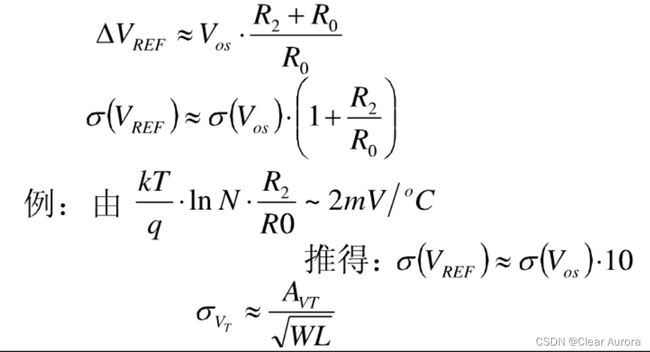

5)电压离散性与噪声:

输出离散性:运放失调的控制很重要!噪声:热噪声可由输出滤波电容来控制;1/f噪声:与Vos一样会被放大,且很难被滤波,因此要特别注意电路中的NMOS;运放输入管应用PMOS,与失调要求一样,要增加W,L。抑制1/f噪声还可采用chopping技术。

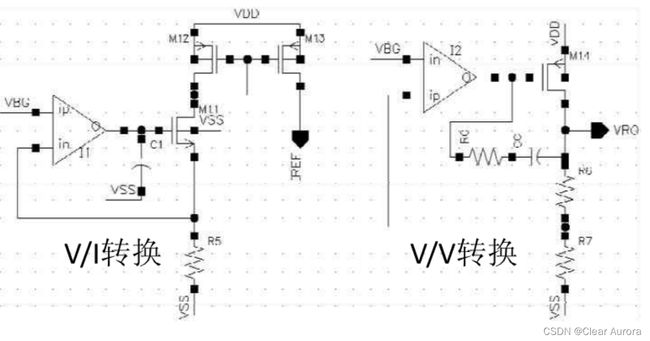

6)局限性与解决办法:

输出基准电压固定为1.2V左右,不够灵活;输出基准电流为PTAT,在全温度范围内变化很大;电源电压的限制:最低工作电压>1.2+Vdsat。解决办法:通过V/V,V/I转换电路来解决前两个问题,代价是电路复杂性和功耗。

三、设计内容与结果:

1、原理图设计及尺寸确定:

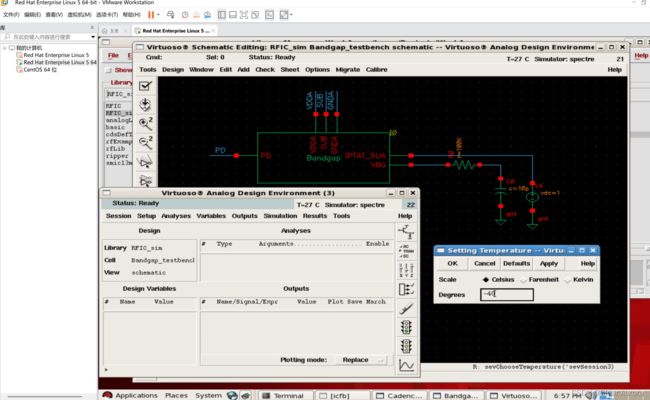

1)运行Cadence Virtuoso icfb,打开Bandgap电路原理图如图:

![]()

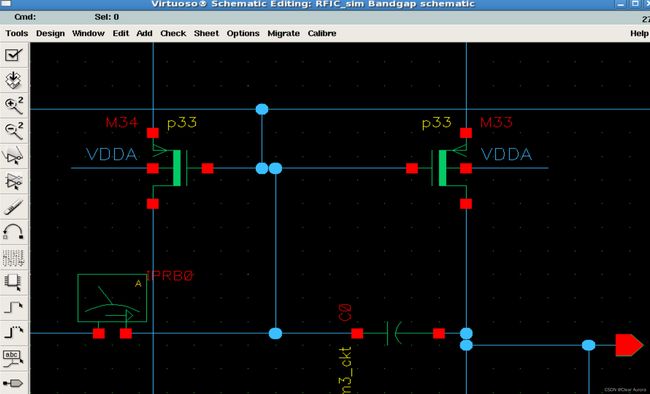

2)分析电路:核心电路中,下左图为两个PMOS构成的电流镜(并联四个,每个沟道长度为1um),下右图为流过相同电流的两个支路,Q4为并联一个的2×2尺寸的BJT晶体管,Q0是并联八个的2×2尺寸的BJT晶体管,Q0的VBE要比Q4要低,所以电压差将加载在R0上。设置R0电阻值大小即可设置支路电流大小。其余电阻尺寸完全相同,与R0成比例得到需要的电压比例关系。

3)运算放大器电路中,下左图为输入部分,采用PMOS差分对,其1/f噪声低,且可保证伪电流源电压使电路正常开启。VDDA为电流镜,从核心电路镜像出电流,尺寸较核心减半,为了降低噪声故沟长设为2um。下中图为折叠结构的二级放大电路,其NMOS伪电流源沟长1um避免沟道长度调制效应。电流由核心电路镜像所得,电流镜MOS尺寸为核心四分之一。确定M32、M13尺寸时考虑1/f共享噪声,同时考虑版图面积,故把沟道长度确定为1um,并联2个。下右图M5为下中图Cascode级提供偏置电压,而M11、M12沟长确定为1um。

4)启动电路中,下左图二极管接法的PMOS将电压降下来,下接反相器,反相器输入端接Bandgap电压,MB7控制内核电路是否产生工作电流用于启动。下右图为PD控制信号端,经过一个反相器接PDn,经过两个反相器接PDp,分别控制下左图中M38、M91与核心电路中M37,控制整个电路的开启与关闭状态。

5)symbol电路与仿真电路搭建:下左图为上述Bandgap电路的模型,下右图为搭建的仿真电路Bandgap_testbench原理图,其中输出端接一个很小的电容负载便于观察输出电压波形,PTAT电流输出接1V理想电压源,VDDA为电源,由V5提供,范围在3.3V到2V之间。引线电感2nH,模拟封装时芯片焊盘与芯片封装管脚上筋线(1mm对应1nH)带来的电感。电阻同理,此处设为100mΩ。GNDA与SUB的引线电感设为1nH,50mΩ(由封装决定)。

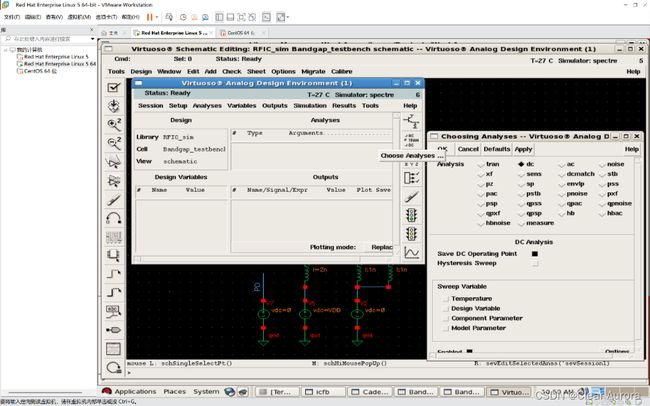

2、直流仿真:

1)打开ADE仿真编辑器,如下设置进行直流工作状态仿真:

2)提取VDDA电源电压,设置大小为3V如图:

3)运行仿真,显示结点电压,如图操作:

4)确定Bandgap_testbench原理图直流工作点如下图:

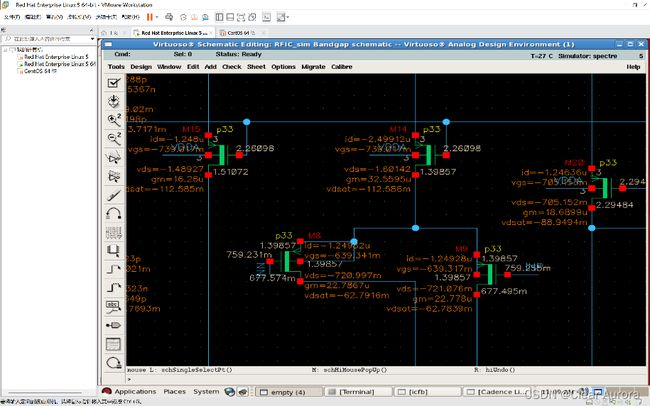

5)进入Bandgap原理图,确定各结点电压电流如图:

可见小尺寸(左)PNP BJT型晶体管发射极电压为-759mV左右,大尺寸也为-704mV左右,电流均为-3uA左右,而PTAT电流为两BJT发射极电压差与R0之比,可通过设定R0的值来改变。

![]()

电流镜各结点电压如上图,可见为保证晶体管工作在放大区,需要|Vds|>|Vdsat|,满足要求。

![]()

运放伪电流源部分,电流镜镜像电流为-2.499uA,准确,同理M15电流镜电流为-1.248uA也符合要求。

上图为NMOS伪电流源电流镜的|Vds|>|Vdsat|,工作状态正确。漏极电流为2.496uA,准确。

折叠运放Cascode级两晶体管|Vds|>|Vdsat|,工作状态没有问题。

二极管接法的PMOS电流镜|Vds|>|Vdsat|,工作在放大区,右边同样|Vds|>|Vdsat|,工作状态正确。

PMOS差分对电路部分,M14伪电流源|Vds|>|Vdsat|,沟道宽度选择没有问题,且差分对也满足|Vds|>|Vdsat|,均工作在放大区,且PMOS差分对Vdsat比较小,整体gm值更大但fT较低,此处应折中考虑。

启动电路部分,反相器PMOS Vds=-1.88V,处于几乎截止状态,而NMOS Vds约等于0,处于导通状态,启动电路的NMOS(M87)栅极被拉至地,处于截止状态,可知启动电路整体电流消耗基本为0。

6)直流扫描:仿真参数选择温度自动扫描,设置从-40扫描至85,如下所示:

运行仿真后,选择Direct Plot查看VBG输出端电压扫描结果,操作如下:

扫描结果如图所示:

![]()

可见曲线抛物线顶点在25℃左右,温度系数为:[1.210916V(MAX)-1.209941V(MIN)]/1.210581V(MID)/125℃×106=6.443ppm.

之后修改R1与R4电阻值使之变小,例如修改为串联20个,如图:

运行仿真后,选择Direct Plot查看VBG输出端电压扫描结果,扫描结果如图所示:

可见其为负温度系数的电压输出特性,需要增加正温度系数分量部分的比例。同理修改R1与R4电阻值使之变大,例如修改为串联30个,如图:

可见其变为正温度系数的电压输出特性,需要增加负温度系数分量部分的比例。通过不断调试电阻值比例,可以调整出理想抛物线结构的温度系数电压输出特性。

2、频率分析:

1)从analogLib中选择Analysis,调入iprobe元件symbol放置在如下图运放输出的位置,便于同时仿真出正负反馈回路的完整频率响应特性:

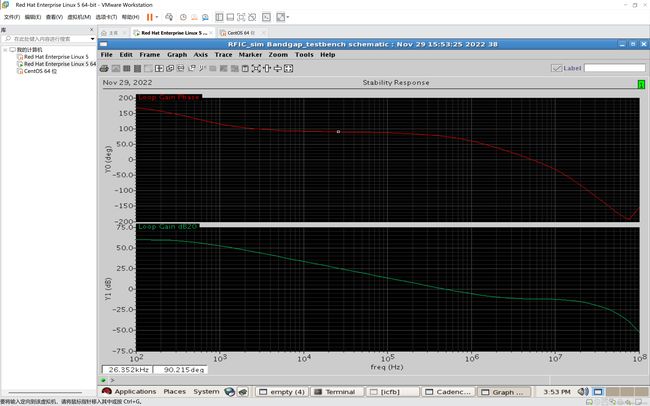

2)在ADE中设置仿真参数:关闭直流温度扫描,选择stb稳定性仿真,扫描频率从100Hz自动扫描至100MHz,选择iprobe元件进行仿真,如图:

3)运行仿真后,选择Direct Plot—>Main from,选择相位裕度可见相位裕度为78.0276度,如图:

之后查看stb环路增益输出结果,选择幅度与相位,单位为dB20,结果如图所示:

可见环路总增益为59dB,相位裕度大于45度,也大于60度,电路稳定。此相位裕量与密勒补偿反馈电容(C0)大小决定,减小电容值可使相位裕量减小。例如将密勒补偿电容尺寸减小为10×20,0.63pF(原先为20×20,1.24pF),如图:

之后查看stb环路增益输出结果,选择幅度与相位,单位为dB20,结果如图所示:

可见相位裕度为74.855度。即:高频增益相较于电容减小前变大,单位增益带宽翻倍,相位裕量减小。若需提高环路增益,可将PMOS差分对与所有晶体管,包括电流镜的沟道长度变大,例如将它们的沟道长度、Fingers翻倍,如图:

运行仿真后,查看stb环路增益输出结果,选择幅度与相位,单位为dB20,结果如图所示:

可见其增益提高到60dB以上,但提高不明显,因为此电路在深负反馈状态下环路增益由反馈系数决定。

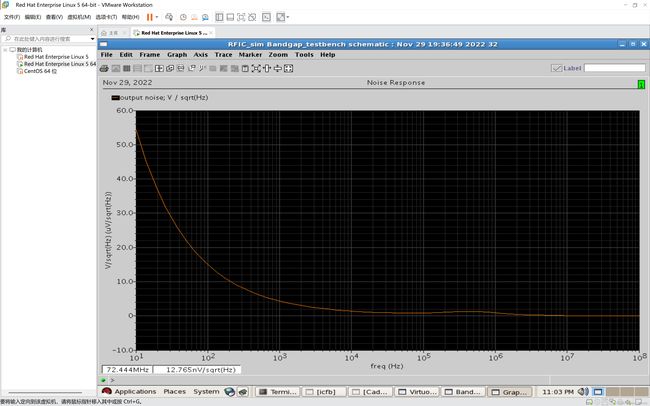

3、噪声分析:

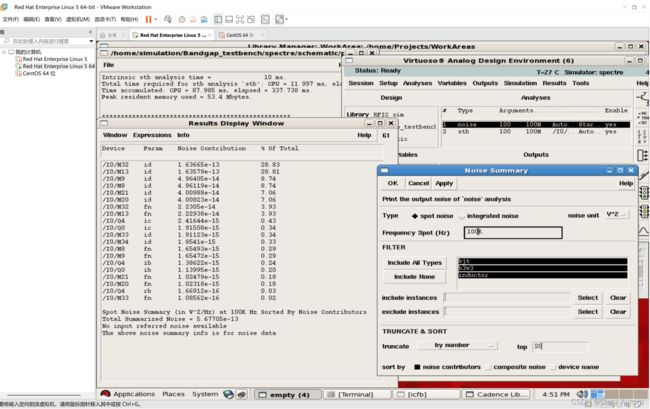

1)ADE设置仿真参数进行噪声分析:扫描频率从100Hz自动扫描至100MHz,选择VBG和GND的电压为噪声输出正负端,不设噪声输入,如图:

仿真结果输出噪声结果如下图,单位:V/sqrt(Hz)

可见在100Hz时噪声为9.72uV,10KHz时为1.33uV,100KHz时为806nV,1MHz时为376nV。Print 1KHz处的噪声来源,90%的噪声来自M32与M13的1/f噪声,5%由电流镜负载晶体管M20与M21的1/f噪声引入,其余噪声贡献较少,如图:

2)为了降低主要噪声,可将M6、M32与M13晶体管沟道长度变大,例如将它们的沟道长度增大为3um(原先为2um)、Fingers增大为3(原先为2),如图:

仿真结果输出噪声结果如下图,单位:V/sqrt(Hz)

可见1KHz时为噪声幅值下降为2.3uV,高频处1/f噪声贡献较小。之后Print 100KHz处噪声来源,56%的噪声来自M32与M13的电流噪声,1/f噪声贡献较少,如图:

3)为了降低主要噪声,可增大运算放大器部分的工作电流,例如将电流放大一倍,即:把M14与M15的Multiplier扩大一倍,如图:

可见100KHz处噪声来源,来自M32与M13的电流噪声贡献下降至50%,如图:

3、瞬态响应特性分析:

1) 从analogLib中选择Sources,调入vpulse元件symbol放置在如下图位置,设置参数如图,便于产生阶跃信号仿真出电路瞬态响应特性:

2) ADE设置仿真参数进行瞬态分析:50us,中等精度,如图:

运行仿真,Direct Plot—>Main from,电源电压VDD和Bandgap输出电压工作上升过程,Bandgap输出电压由过充到下降,最后随VDD稳定而稳定,如图:

3)同理,反相器漏端电压跟随电源电压上升,最后随电源电压稳定而稳定,如图:

4)反相器反相端电压开始时跟随电源电压上升,超过NMOS阈值电压后翻转变为0V,此时电路进入正常工作状态,Bandgap电压输出正常输出,如图:

5)电流镜栅极电压瞬态响应曲线如图,其电压随电源电压上升而上升,在反相器反相端电压翻转变为0V后快速上升到最终工作电平:

3、电源抑制比分析:

1)调入交流电源元件symbol放置在如下图位置,设置参数如图:![]()

2)ADE设置仿真参数进行AC交流小信号分析:10Hz到10MHz自动扫描,如图:

运行仿真,Direct Plot—>Main from,选择VBD输出端查看扫描结果,单位dB20:

3)可见电源抑制比在10Hz处为-100dB,1KHz处为-62dB,10KHz处为-41.79dB,100KHz处为-21dB,1MHz处为-1.21dB,如图:

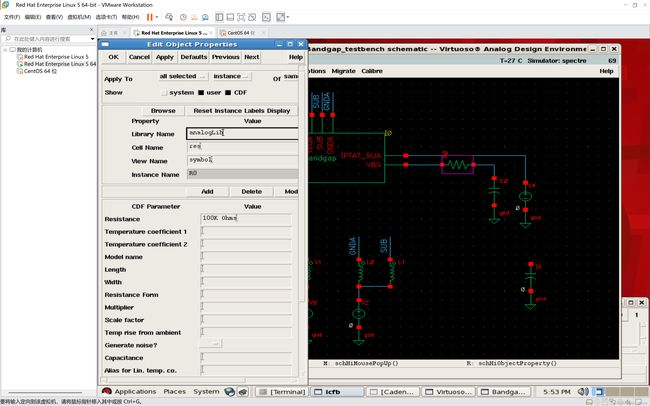

4)为实现高频电源抑制,需要进行外部滤波,即加一个RC低通滤波,串联阻容,电阻为100KΩ,电容为10pF,如图:

可见电源抑制比在高频处有所改善,如图:

并且此时高频噪声得到了一定程度的滤除,如图:

5)之后将伪电流源晶体管沟道长度减小一倍,同比缩小晶体管沟道宽度,如图:

可见低频处电源抑制比变差,但整体电源抑制比增益有优化且优化量不大,如图:

6)修改密勒反馈电容,将其尺寸变为10×10,容值缩小一半,如图:

修改密勒反馈电容后,电路相位裕度有所减小,为61.592度,满足要求;单位增益带宽翻倍到800KHz左右,如图:

此时整体电源抑制比增益有优化且优化量较为理想,下降了约5dB,如图:

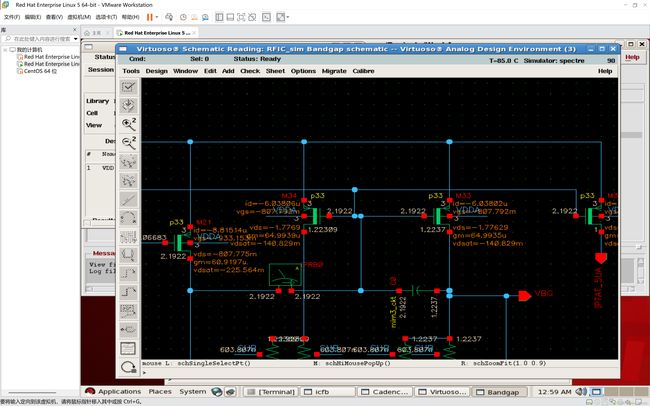

4、可靠性设计:

2)运行直流仿真后进入Bandgap原理图,确定各结点电压电流,核心电路电流镜各结点电压如下图,可见为保证晶体管工作在放大区,需要|Vds|>|Vdsat|,满足要求。但其PTAT电流仅为-3.71uA,较设计标准5uA小,对性能有影响。除此之外,依次检查其他晶体管,工作状态均满足要求。

3) 运行stb稳定性仿真后,选择Direct Plot—>Main from,可见相位裕度为58.7519度,接近60度,可接受,如图:

4)噪声方面,仿真输出噪声结果如下图,单位:V/sqrt(Hz),可见在1KHz时噪声为4.2uV,10KHz时为1.4uV:

5) 运行AC仿真,选择VBD输出端查看扫描结果,单位dB20,可见电源抑制比在1KHz处为-66.43dB,10KHz处为-46.57dB,100KHz处为-25.67dB,如图:

综上,低温时各指标满足所需工作要求。

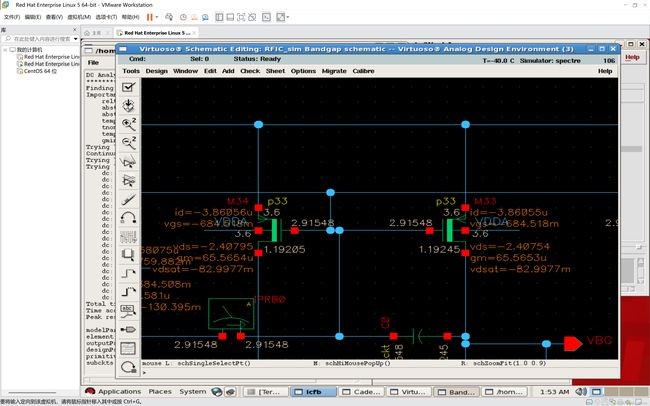

6)将整个电路工作环境温度设置为85℃,运行直流仿真后进入Bandgap原理图,确定各结点电压电流,核心电路电流镜各结点电压如下图,|Vds|>|Vdsat|,满足正常工作状态。但其PTAT电流上升为-6.24uA,较设计标准5uA大,对性能有影响。除此之外,依次检查其他晶体管,工作状态均满足要求。

7) 运行stb稳定性仿真后,选择Direct Plot—>Main from,可见相位裕度为62.4253度,大于60度,符合条件,如图:

8)噪声方面,仿真输出噪声结果如下图,单位:V/sqrt(Hz),可见在1KHz时噪声为6.13uV,10KHz时为1.845uV:

9) 运行AC仿真,选择VBD输出端查看扫描结果,单位dB20,可见电源抑制比在1KHz处为-67.86dB,10KHz处为-48.54dB,100KHz处为-27.02dB,如图:

综上,高温时各指标满足所需工作要求。

10)最高工作电压确定:设置电路工作温度为27℃,工作电压VDD=3.6V,执行直流温度扫描,仿真参数设置如下:

11)运行直流仿真后进入Bandgap原理图,确定各结点电压电流,核心电路电流镜各结点电压如下图,|Vds|>|Vdsat|,满足正常工作状态。其PTAT电流为5.05uA,符合标准。除此之外,依次检查其他晶体管,工作状态均满足要求。

启动电路中反相器漏电流为-190.485pA,较大但在可接受范围内,如图:

温度从-40扫描至85,VBG扫描结果抛物线顶点在25℃左右,符合要求,如图:

12)运行AC仿真,在VBD输出端查看扫描结果,单位dB20,可见电源抑制比在1KHz处为-60.9dB恶化,10KHz处为-47.5dB,100KHz处为-26.02dB,如图:

同理噪声、稳定性相较于VDD=3V时变化不大。

13)最低工作电压确定: 27℃,工作电压VDD=2V,执行直流温度扫描,核心电路电流镜各结点电压如下图,|Vds|>|Vdsat|,满足正常工作状态。其PTAT电流为5.05uA,符合标准。除此之外,依次检查其他晶体管,工作状态均满足要求。

运行AC仿真,选择VBD输出端查看扫描结果,单位dB20,可见电源抑制比在1KHz处为-65.22dB,10KHz处为-47.24dB,100KHz处为-26.02dB,变化不明显。

另外VDD=1.5V时工作不正常。综上,电源电压工作范围在2V到3.6V时可行。

14)工艺角偏差分析:工艺角SS85℃时,调入仿真如图:

此时Model Library设置中均为SS工艺偏差,如图:

工作温度85℃,工作电压VDD=3V,执行直流仿真,核心电路电流镜各结点电压如下图,|Vds|>|Vdsat|,满足正常工作状态。其PTAT电流为6.03uA,有增大但可接受。除此之外,依次检查其他晶体管,工作状态均满足要求。

温度从-40扫描至85,VBG非最佳曲线情况,属于正温度系数但可接受,如图:

运行AC仿真,选择VBD输出端查看扫描结果,单位dB20,可见电源抑制比在1KHz处为-66.22dB,10KHz处为-46.16dB,100KHz处为-25.22dB,变化不明显:

运行stb稳定性仿真,可见相位裕度为60.3971度,大于60度,符合条件,且环路增益为42.4dB,环路增益有所下降,如图:

另外,VDD=1.7V时,需要对电路Cascode级提供偏置电压的方式进行修改如图,其中电阻设置为80KΩ左右:

此时才能使电路运放与伪电流源部分正常工作且其stb仿真后相位裕度为61.2468度,大于60度,符合要求,如图:

环路增益41.67dB,如图:

运行AC仿真,选择VBD输出端查看扫描结果,单位dB20,可见电源抑制比在1KHz处为-60.85dB,10KHz处为-46.66dB,100KHz处为-25.62dB,如图:

综上,在工艺角SS85℃时电路可正常工作,并且在最低电压(修改电路Cascode级偏置方式后)与最高电压范围内性能可接受。

15)工艺角偏差分析:工艺角FF-40℃时,工作温度-40℃,工作电压VDD=3.6V,执行直流仿真,核心电路电流镜各结点电压如下图,|Vds|>|Vdsat|,满足正常工作状态。其PTAT电流为3.8uA,有些许增大但可接受。除此之外,依次检查其他晶体管,工作状态均满足要求。

温度从-40扫描至85,VBG非最佳曲线情况,属于负温度系数但可接受,如图:

运行AC仿真,选择VBD输出端查看扫描结果,单位dB20,可见电源抑制比在1KHz处为-63.05dB有衰减,10KHz处为-46.16dB,100KHz处为-27.12dB:

运行stb稳定性仿真,可见相位裕度为64.1703度,大于60度,符合条件,且环路增益为41.72dB,环路增益有所下降,如图:

另外,VDD=1.7V时,运行AC仿真,选择VBD输出端查看扫描结果,单位dB20,可见电源抑制比在1KHz处为-64.59dB,10KHz处为-48.26dB,100KHz处为-28.02dB,相较于常温条件变化不大,如图:

综上,在工艺角FF-40℃时电路可正常工作,并且在最低电压(修改电路Cascode级偏置方式后)与最高电压范围内性能可接受。

16)在FF-40℃下验证电路瞬态特性:首先设置阶跃信号如图所示:

运行仿真后可见Bandgap输出电压在最低工作电压(1.7V)与最高工作电压(3.6V)下工作的上升过程:Bandgap输出电压由过充到下降,最后稳定,可见电路在最低工作电压和最高工作电压范围内能够正常工作、快速启动,如图:

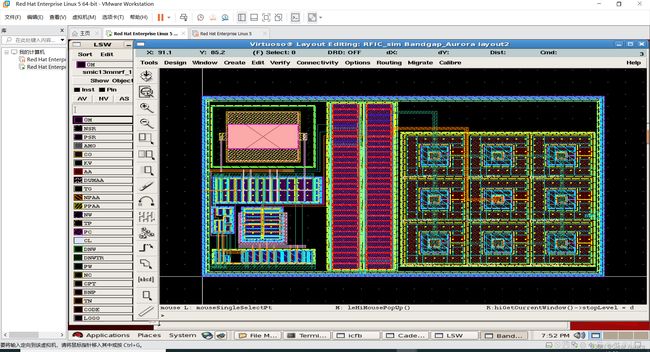

5、版图设计:

1)将仿真设计好的工程文件复制,为便于区分我命名为Bandgap_Aurora_Layout。

2)删除多余元器件,原理图如下:

3)打开Layout XL,创建新的版图文件命名为Layout_Aurora,如下左图,之后从原理图内导入元器件,操作如下右图:

调入元件后版图如图所示:

4)对调入的元器件进行布局,总体布局如图:

将PNP晶体管置于右侧阵列,如图:

电阻位于中部(部分电阻使用了蛇形交叉匹配)排列,如图:

核心电路电流镜位于左中部中间,最左边为PTAT输出电流源,伪电流源放在对称的右侧,可做到较好匹配性;PMOS电流镜M20、M21放于它们右侧,如图:

运放PMOS差分对位于左部靠下中间位置,采用十字交叉的匹配方式,如图:

NMOS伪电流源和为其Cascode级提供偏置的晶体管排为一列,电流镜晶体管左右交叉放置,单个提供偏置的晶体管放于最中间,Cascode级放于右侧,如图:

启动电路与反相器放置于整个电路左下角,如图:

密勒补偿电容放置在整个电路右上角,如图:

5)对布局整理排列便于后续布线,使元件在设计规则允许范围内尽量靠近,如图:

6)进行SUB环与WELL环布置,通过Multipart Path(F3)脚本实现,如图:

按设计规则设置不同层参数的脚本画各层的环,下图为PSUB环(接衬底):

下图(紫色)为NWELL环(接电源电压),为单排过孔:

整个CELL外围需布置保护环进行隔离,过孔为两排,如图:

7)版图连线:使用Path功能在不同金属层连线,将各个元器件连接起来。下图为PNP晶体管的SUB层连线:

使用金属二层将晶体管所有发射极连接在一起,如图:

使用金属三层将晶体管所有发射极引出其中一个发射极连接电阻,如图(红):

电阻连线为蛇形交叉方式连线,如图(只显示金属一层和GT层):

运放部分,差分对栅极由金属三层交叉连线实现较佳匹配特性,源端通过半包围金属二层,过孔接至金属一层与NWELL电位连接减小衬偏效应,如图:

伪电流源部分左右交叉连线,Cascode最终输出接差分运放PMOS电流镜,如图:

Bandgap核心电路电流镜也是采用交叉连线的匹配方式,如图:

密勒补偿电容跨接方式如图:

8)版图最终连线结果如图:

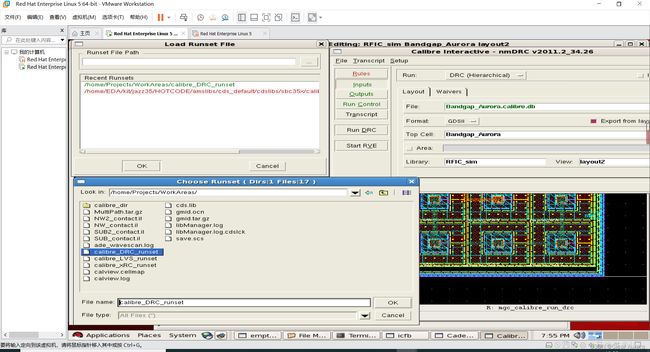

6、版图DRC验证:

1)从RFIC_Sim Bandgap_Aurora打开以上布好线的Bandgap版图如下:

2)在DRC对话框内Load calibre_DRC_runset文件,操作如图:

3)运行DRC后可得到结果,其中有十三个错误如下:

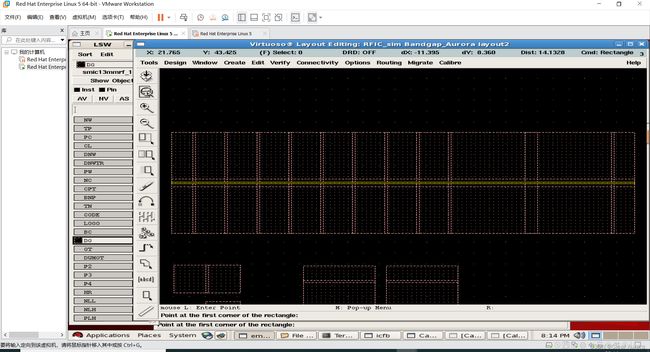

4)修改第一个DG层间距错误:在DG层绘制矩形使DG层覆盖,如图:

此时再次运行DRC可见第一个错误消除:

5)对于第二个错误如图,下方提示( For 0.11um design, 2.5/3.3V transistor channel (overlap of Poly and AA) enclosure by DG.( Designer can waive this rule for 0.13um design).>=0.30)可见,因为我们使用的是0.13um的工艺,故可忽略此错误:

6)对于第三个错误:GT层需要被SN或SP层所包围,如图:

则在SN、SP层逐一绘制矩形框将栅极所包围,如下若干图:

7)对于第四个错误:要求M1层间距大于0.17um,如图:

则将栅极过孔数设为2,如下两图,则可解决问题:

8)对于第五个错误:M1层最小面积问题,如图:

则在M1层绘制矩形框将该位置完全包围,如图:

9)对于第六个错误:要求M2层间距大于0.2um,如图:

则将M2层整体移动使之间距大于0.2um,如图:

10)第七到第十一个错误:金属密度不足,将在总图修正,此小单元中不处理:

11)最后两个错误:BORDER层须绘制包括住所有电路元件,并且BORDER层要比芯片最外围超出0.73um,如图:

则绘制BORDER层。至此,将所有DRC错误修改好后的最终版图如图:

![]()

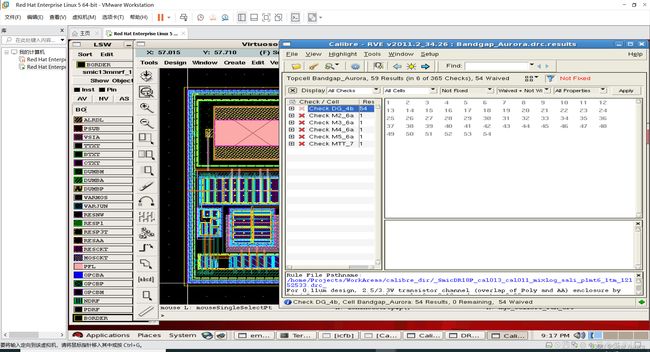

12)解决完所有错误,重新运行DRC,可见除了可忽略的错误以外无其他问题,至此可认为版图DRC验证通过,如图:

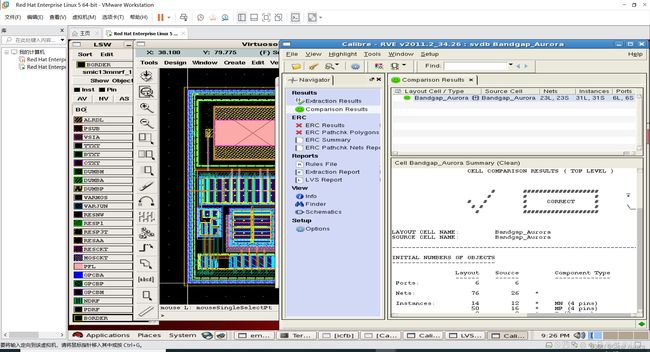

7、版图LVS验证:

1)在LVS对话框内Load calibre_LVS_runset文件,操作如图:

2)可见LVS验证可通过,但ERC中有ptap错误,如图:

事实上在设计过程中ptap(PSUB接触孔)已经接地(低电位),可通过在LVS内设置电源名称(VDDA)与地名称(GNDA和SUB)解决,如图:(实际上只要确认电源、地和PSUB的电位正确即可,此错误可忽略)

8、寄生参数提取:

1)在PEX对话框内Load calibre_xRC_runset文件,进行正确的Output设置如图:

2)运行PEX后,保存Calibre文件,选择阵列、原理图的形式保存,保存完成后需保证对话框提示无ERROR,如图:

3)提取出的寄生参数如图,上面部分为实际电路元件与端口,下部分为所有寄生参数,包括所有的寄生电容与寄生电阻,以及相互耦合的电容:

9、后仿真验证:

1)将Bandgap_testbench原理图内单元名改为上述步骤中提取过寄生参数的Bandgap_Aurora,如图:

2)载入之前的仿真参数,由于iprobe元件在此原理图中已不存在,故需要关闭stb仿真,如图:

3)在仿真顺序中将calibre加到原理图前面,如图:

4)运行仿真后得到后仿真结果,下图为DC仿真温度扫描在VBG端的输出结果,可见前后仿真(于同一图中)结果类似,无太大差别:

5)下两图为AC频率扫描在VBG端滤波后前仿真和后仿真的输出结果(于一图中),可见电源抑制比前后仿真结果差异很小:

6) 确定Bandgap_testbench原理图直流工作点如下图,可见直流工作点电流与前仿真差别不大,工作状态正确:

![]()

7)设置电源为阶跃信号,以便进行瞬态响应(启动状态)的后仿真,如图:

![]()

可见电源电压VDD和Bandgap输出电压工作上升过程如下图:Bandgap输出电压随VDD上升而上升,在12us左右稳定在正常工作状态。由此可见在进行版图设计后,考虑寄生参数的同时,电路可顺利启动。

8)下图为DC后仿真的PTAT电流随高低温变化的情况,其后仿真结果满足要求:

10、综上,整个Bandgap电路的电路原理图设计、直流仿真、频率与噪声分析、可靠性设计、版图设计和验证,以及后仿真验证全部完成。

写在最后:

通过这次模拟集成电路设计实践,可以了解并掌握了整个Bandgap电路的电路原理图设计、直流仿真、频率与噪声分析、可靠性设计、版图设计和验证过程,以及后仿真验证过程。

在此过程中,无论是原理图仿真环节,还是版图设计、验证环节,我都或多或少遇到了一些非常规问题,例如仿真失败、布线错误、验证时调入配置文件失败、DRC失败等等,并且自己尽力地解决,从而最后完整地完成了设计实践的整个过程。

其实,人生当中成功只是一时的,失败却是主旋律。但是如何面对失败,却把人分成了不同的样子。有的人会被失败击垮,有的人能够不断地爬起来继续向前。设计Bandgap电路原理图、不断调整晶体管尺寸是如此,进行电路版图设计、电阻排布匹配也是如此。我想,无论做什么事情,真正的成功并不是追求完美,而是直面自己的缺憾,这才是实践的本质。

罗曼-罗兰说过,这个世上只有一种真正的英雄主义,那就是认清生活的真相,并且仍然热爱它。电路设计过程中有任何失败,我都可以重头再来。难道向上攀爬的那条路,不是比站在顶峰更让人热血澎湃吗?我认为,设计集成电路的这个过程本来就是这样的,有时候咬咬牙,就已经走了很远。

我会一直热爱这个过程。