数字集成电路及其版图设计:带有预置数功能的8位二进制加减计数器设计及版图实现

数字集成电路及其版图设计

带有预置数功能的8位二进制加减计数器设计及版图实现

一、目的:

1、熟悉数字集成电路设计的基本流程;

2、熟悉虚拟机的安装及使用方法;

3、熟悉Linux系统及vi编辑器的操作;

4、熟悉Quartus II、Design Compiler、Encounter设计软件的使用方法。

二、原理:

1、设计原理:计数器是最常用的寄存器逻辑电路,从微处理器的地址发生器到频率计都需要用到计数器。一般的计数器可分为两大类:加法计数器和减法计数器。加法计数器每来一个脉冲计数值加1;减法计数器则减1。

2、要求:用Verilog HDL语言设计一个带有预置数功能的8位二进制加减计数器。电路包括一个时钟输入端clk,一个异步清除输入端clr,一个同步预置位控制输入load,1个8位预置数据输入端d[7:0],一个加减控制输入端updown,1个8位计数输出端q[7:0],一个进位输出端rc。此次任务是利用数字集成电路的设计方法进行N位二进制加法/减法/加减计数器的电路设计及版图实现。

三、步骤及结果:

1、行为设计及行为仿真:

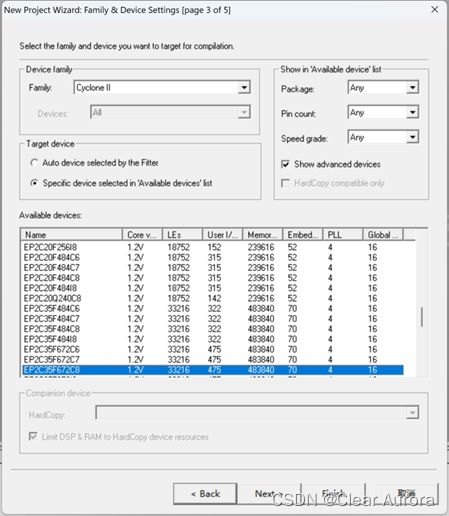

1)运行Quartus II,选择File>New Project Wizard,新建一个工程,FPGA芯片在Available device 列表中选择EP2C35F672C8:

2)按照设计要求,在新建的HDL文件中编写程序:带有预置数功能的8位二进制加减计数器,电路包括一个时钟输入端clk,一个异步清除输入端clr,一个同步预置位控制输入load,1个8位预置数据输入端d[7:0],一个加减控制输入端updown,1个8位计数输出端q[7:0],一个进位输出端rc,最终程序如下:

module LiTianhao(q,clk,load,d,reset,updown,RC);

output [7:0] q;

output RC;

input [7:0] d;

input clk,reset,load,updown;

reg [7:0] q;

reg RC;

wire clr;

always @(posedge clk)

begin

RC<=0;

q<=8'b0;

if(reset)

begin

q<=8'b0;

end

else begin

if(load)

begin

q<=d;

end

else if(load==0&updown==0)

begin

q<=q+1;

RC<=0;

end

else if(load==0&updown==1)

begin

q<=q-1;

RC<=0;

end

if(q>=8'd255)

begin

RC<=1;

end

end

end

endmodule

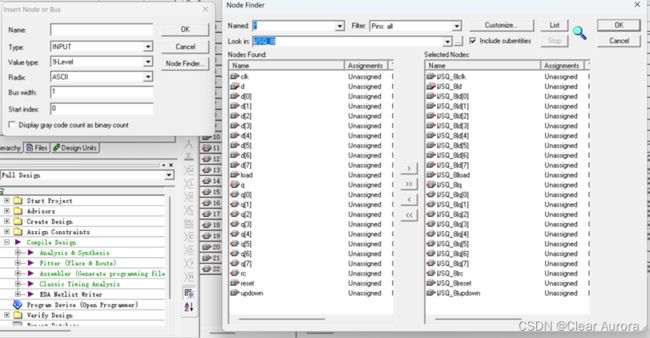

3)代码书写结束后,选择Processing>Start Compilation对编写的代码进行编译,编译通过后,建立波形文件,选择Insert Node or Bus,Node Finder,Filter中选择Pins:all,点击List,这样在Nodes Founder区域出现先前HDL文件中定义的输入、输出端口,点击>>,选择OK,如下图:

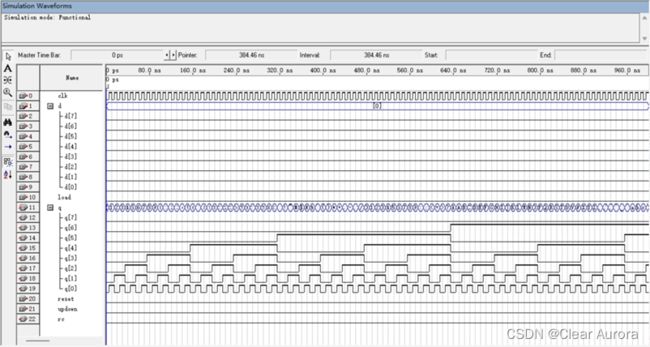

4)Processing>Simulation Tool,Simulation mode选择Functional(功能仿真),点击Generate Functional Simulation Netlist按键生成功能仿真网表(如要进行时序仿真,则Simulation Mode选择Timing),如下图:

5)结果:上述程序仿真结果如下图所示:

上图为无预置数、无异步清除、加计数的仿真结果。

上图为无预置数、无异步清除、减计数的仿真结果。

上图为异步清除的仿真结果。

上图为预置数输入10100000(十进制:160)、无异步清除的仿真结果。

综上所述,程序和仿真结果均达到设计要求。

2、逻辑综合:

1) Open Terminal打开操作终端,键入Linux系统命令打开Syn,在Syn下建立工作目录WorkArea如图:

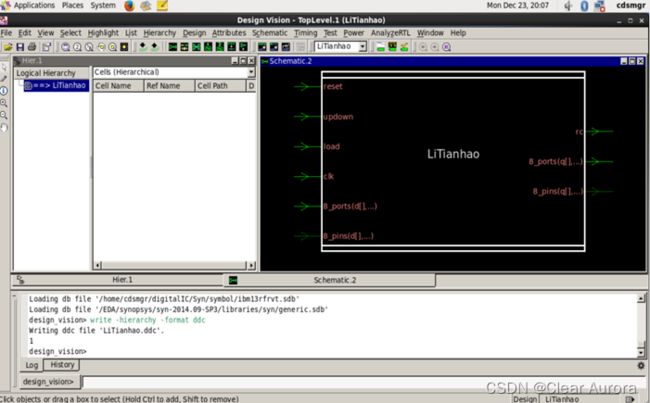

2)进入建好的工作目录,键入design_vision 命令启动用户图形界面如图:

3)File->Setup,设置综合时所要映射的在/home/cdsmgr/digitalIC/Syn目录下的逻辑单元库文件.db以及符号库文件.sdb,如图:

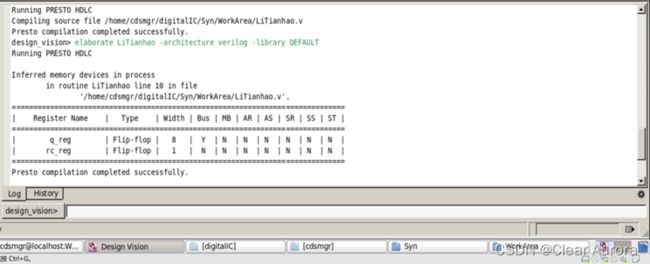

4)File->Elaboration,分析设计模型,进行综合前预处理,Create Design Schematic查看综合前电路图,如图:

5)命令执行信息窗口显示了使用的寄存器信息和清零端信息(AR:asynchronous reset)如图:

6)Create symbol view,生成综合前的电路元件符号如图:

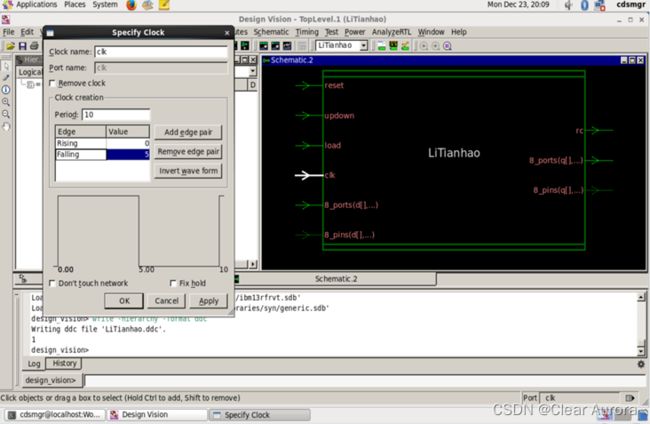

7)Attributes->Specify Clock ,设定时钟如图:(可在Attributes->Operation Environment 下设定输入延迟、驱动能力、连线负载等其他参数)

8)Attributes->Optimization Constraints–>Design Constraints,进行综合过程的条件约束设置,将面积优化到最小,如图:(可在Attributes->Optimization Constraints下设定优化时间等参数)

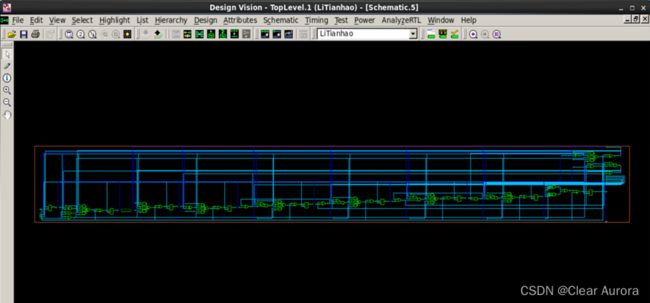

9)Design->Compile Design 进行编译后,综合后电路图与电路元件符号如图:

10)Timing->Report Timing Path,报告时序信息如下一图,其中slack(MET)大于0,满足设计时序要求;Design->Report Area,报告面积信息如下二图:

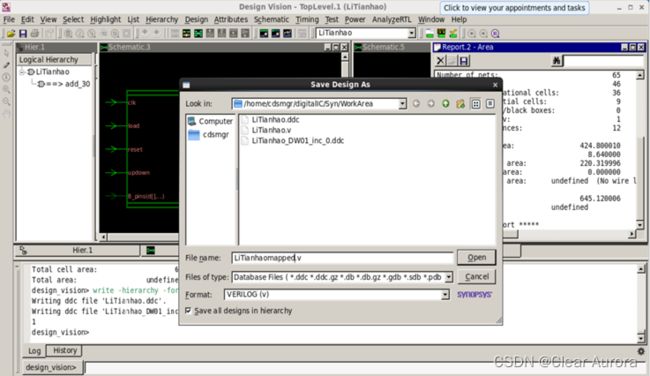

11)File->Save as,保存综合后网表文件LiTianhaomapped.v

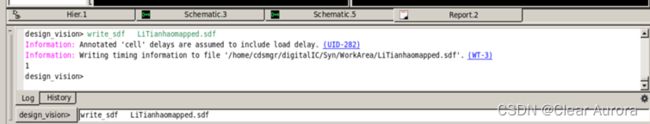

12)命令行键入write_sdf LiTianhaomapped.sdf,保存延时信息:

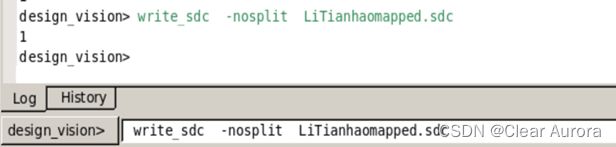

13)命令栏键入write_sdc -nosplit LiTianhaomapped.sdc ,保存时钟设计约束条件:

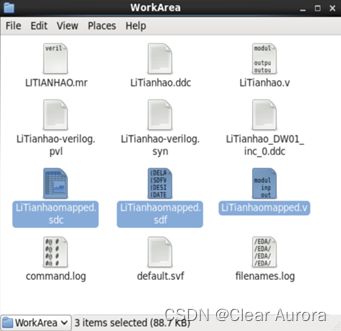

14)综合完成。在工作目录下找到综合后网表文件LiTianhaomapped.v和时钟约束条件文件LiTianhaomapped.sdc,用于后面的布局布线。

15)在工作目录将综合后的模块名改为和文件名一致(LiTianhaomapped),如图:

3、自动布局布线:

1)Xshell5—>属性,设置主机地址,然后点击“隧道”,勾选Xmanager,连接主机并登录,如图:

2)使用vi编辑器将综合后网表文件LiTianhaomapped.v和时钟约束条件文件LiTianhaomapped.sdc以及LiTianhaomapped.sdf文件导入主机,分别如下三图:

3)键入 encounter 命令启动用户图形界面如下两图:

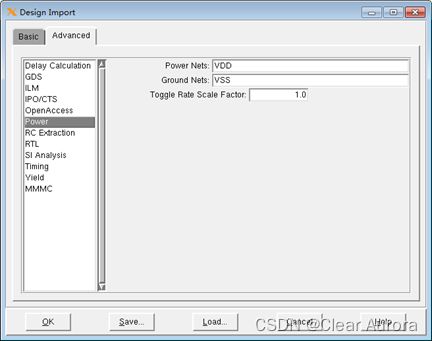

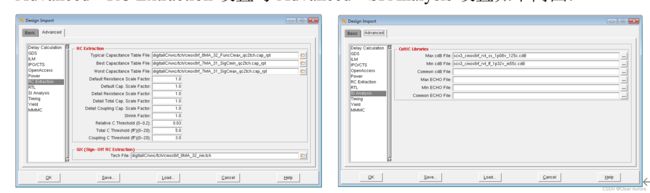

4)Design-> Design Import 设置输入文件,同时Advanced --Power设置如图:

Advanced --RC Extraction设置与Advanced --SI Analysis设置如下两图:

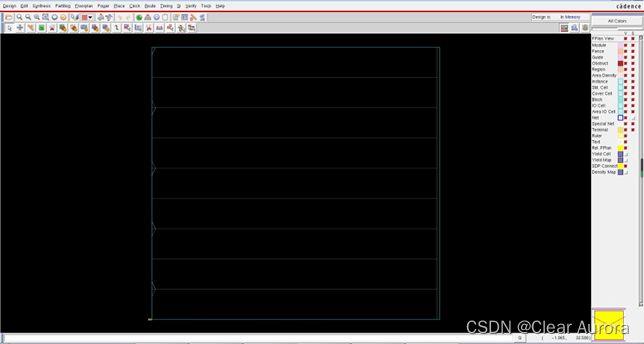

5)Save保存为LiTianhaomapped.conf文件,之后OK,得下图:

6)FloorPlan -> Specify Floorplan 进行版图的平面规划,设置与结果如下两图:

7)Power -> Power Planning -> Add Ring 添加电源线,设置与结果如下两图:

8)Edit -> Pin Editor进行端口定位,逐一设定各个端口的方位和使用的金属层、端口坐标,设置与结果如下两图:

9)Route -> Special Route进行布线,设置与结果如下两图:

10)FloorPlan -> Connect Global Net连接所有电源和地,如下左图,Place -> Place Standard Cell,把标准逻辑单元放入,结果如下右图:

11)Route -> Trail Route 进行布线,连接所有标准单元,如图:

12)Timing -> Extract RC抽取寄生参数,如下左图,Route -> NanoRoute -> Route进行精确布线,结果如下右图:

13)Place—>Physical Cells —>Add Filler,在Cell List栏选择Filler的Cell名,将Cell列表中的Cell都选择上,设置如下两图:

给Core中加入Filler,添加完Filler的版图如下:

14)Verify进行几何形状验证及连接验证:Geometry、Connectivity,如下两图:

15)输出布局布线后网表文件(.v)及时序信息文件(.sdf),Timing→ Extract RC,保存spf,spef文件。如下两图:

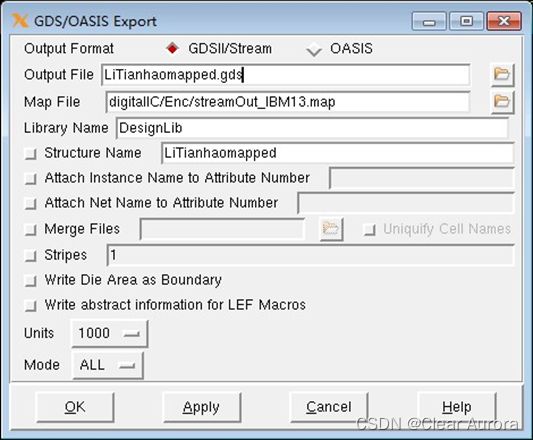

16)输出版图信息(.gds):Design →Save →GDS,保存GDSII格式版图文件,命名为LiTianhaomapped.gds,Map File选择streamOut_IBM13.map,如图:

17)最终版图如下: