cmos模拟集成电路设计 艾伦 课件_Hspice学习记录(一)CMOS模拟集成电路基础

2020/8/3 ~2020/8/4

1.1 标准的CMOS工艺流程:以标准单层多晶硅两层金属CMOS器件为例

1、初始清洗 2、前置氧化(热氧化法、降低应力)

3、淀积氮化硅(LPCVD、离子注入掩膜、后续工艺中帮助定义P阱区域)

4、P阱形成(光刻) 5、刻蚀氮化硅

6、P阱离子注入 7、P阱退火及氧化层形成(为之后的N阱注入形成掩膜)

8、去除氮化硅(热磷酸湿刻) 9、N阱离子注入 10、N阱退火

11、去除二氧化硅 12、前置氧化(减少应力)

13、氮化硅淀积(LPCVD、定义出元件隔离区)

14、元件隔离区的掩膜形成 15、刻蚀氮化硅(去除光刻胶)

16、元件隔离区的氧化(刻蚀掉氮化硅的区域形成场氧隔离)

17、去除氮化硅

18、利用氢氟酸去除电极区域的氧化层(去除氮化硅后还剩一层前置氧化形成的热氧化层,将其去除,以便重新生长品质更好的二氧化硅薄膜,作为栅氧化层)

19、栅氧化层的形成(热氧化) 20、多晶硅栅的淀积

21、多晶硅栅掩膜的形成 22、刻蚀出多晶硅栅(去胶)

23、热氧化(在晶圆表面形成一层热氧化层)

24、NMOS源极和漏极的形成(光刻、离子注入、去胶)

25、PMOS源极和漏极的形成

26、未掺杂的氧化层淀积(PECVD、保护原件表面免于后续工艺的影响)

27、CMOS源极和漏极的活化与扩散(退火)

28、淀积含磷硼的氧化层(硼硅玻璃熔点低,800摄氏度即可软化流动,可以用来进行表面初级平坦化)

29、接触孔的形成(光刻、刻蚀)

30、溅射M1(含钛/氮化钛/铝/氮化钛的多层金属膜)

31、定义出第一层金属的图形(光刻、刻蚀出导线结构)

32、淀积二氧化硅(PECVD、保护层)

33、涂上二氧化硅(将流态的二氧化硅旋涂【SOG,spin on glass】在晶圆表面,使其平坦化)

34、SOG烘干(流态二氧化硅溶于溶剂中需要把溶剂蒸干)

35、淀积介电层 36、M2接触孔(Via)的形成

37、M2形成 38、淀积保护氧化层(PECVD) 39、淀积氮化硅(PECVD)

40、PAD的形成(光刻刻蚀出焊盘区域【pad】,作为后续集成电路封装工艺时连接焊线的接触孔)

41、将元件退火(让器件又最优化的金属电性接触和可靠性)

1.2 CMOS模拟集成电路设计

特点:所有的有源和无源器件都制作在同一衬底上,尺寸及其微小,无法再用电路板进行设计验证。

1.1 CMOS模拟集成电路设计的一般流程1.3 MOS管理论基础

1.3.1 MOS管基本结构与I/V特性

1.2MOS管器件参数1、

2、

3、

4、击穿区 NMOS漏极-衬底之间的PN结由于

1.3.2 MOS管二阶效应

1、体效应

一般的分析中都认为MOS管的衬底和源极相连,所以有

考虑体效应后,阈值电压

2、沟长调制效应

*一般而言,沟道越长,λ越小

1.4沟长调制效应引起的饱和区有限斜率3、亚阈值导电特性

1.3.3 短沟道效应

1、垂直电场引起的迁移率下降

在强垂直电场的作用下,载流子更靠近界面,衬底表面散射增加,导致迁移率下降。

2、水平电场引起的速度饱和

载流子速度

3、热载流子效应

可能的危害:1)造成源衬之间PN结正偏 2)击穿栅氧

4、阈值电压变化

1.4 CMOS器件模型

包括大信号模型、小信号模型、计算机仿真模型

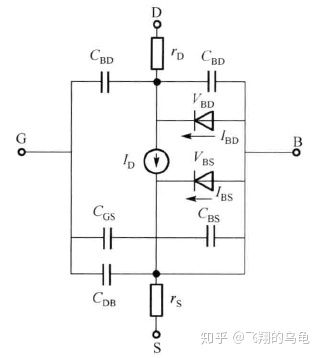

1.4.1 MOS管大信号模型

直流状态、稳定状态

1.5MOS管大信号模型1.4.2 MOS管小信号模型

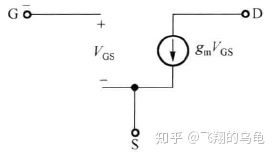

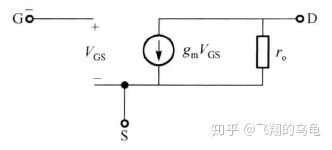

存在一定频率的交流信号。可以通过在直流偏置点上产生一个小的增量并通过计算它所引起的其他偏置参数的增量来构建小信号模型。

1.6基本的MOS管小信号模型由于沟长调制效应,

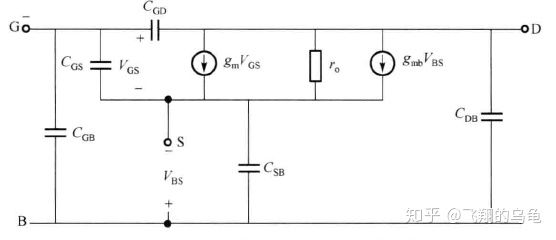

由于体效应,衬底电势将直接影响阈值电压,所以对栅-源过驱动电压(饱和电压)产生一定影响。

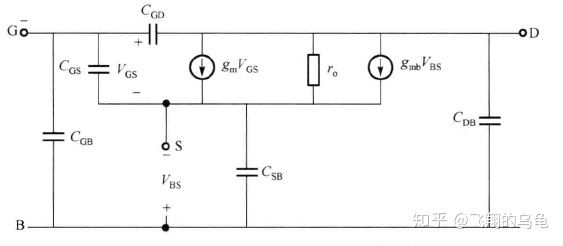

1.8考虑体效应的MOS管小信号模型上述模型适用于较低的工作频率下,频率升高时要考虑MOS管各极之间电容的作用,高频下完整的MOS管小信号模型如下图

1.9高频下完整的MOS管小信号模型*频率特征

定义MOS管电流增益为1时的工作频率为MOS管的特征频率

数字电路:

模拟电路:

一般电路而言,工作频率会在1/5

1.4.3 MOS管噪声模型

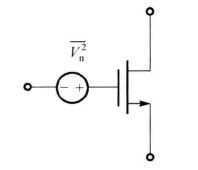

1、热噪声

产生原因:MMOS管具有沟道电阻

热噪声可以用一个连接在漏端和源端间的噪声电流源来表示

沟道等效电阻

也可以用一个栅极相对噪声电压源来表示

2、闪烁噪声

产生原因:晶体表面污染和晶体缺陷,在栅氧化层与硅衬底的界面上会出现许多悬挂键,产生额外能态,在这个界面上,有一些载流子被随机地俘获和释放。

闪烁噪声可以用一个与栅极串联地电压源表示

MOS管总噪声可以表示为

3、散粒噪声

产生原因:导体内通过某一给定表面的载流子数变化

对于MOS管来说,由于栅电流非常弱,故散粒噪声几乎可以忽略

1.4.4 MOS管计算机仿真模型

1、BSIM模型

2、BSIM3v3模型(Spice工具中称为Level 49 模型)