FPGA成神之路 ----- 菜鸟的武器(edk 开发使用)

给大家介绍菜鸟的第二款武器。xilinx edk 开发软件。

武器介绍:

名称:Xilinx Platform Studio

功能:xilinx 系列FPGA利用MicroBlaze或硬核开发的必备武器,属于ise套装中的一部分。此武器很少单独出现,一般都是和他的爱妻SDK一同闯荡江湖。

武力:4星。(与sdk合体后,武力值翻倍)

推荐等级: 9级(学习MicroBlaze开发的菜鸟必备)

备注:本版本开发套件,为xilinx公司ise产品最后一个版本。优点多多,BUG也多多,这里的BUG在EDK中表现无疑,具体问题具体解决。

获取方法:在xilinx官网上可以下载

装备方法:和普通的软件安装方法一致,没什么特殊强调的地方。一点安装时间很长,如果卡在某个地方20--30分钟,大家不要觉得是程序卡死,继续等下去。

安装好ise套件后,会自带EDK软件。

使用教程

1,打开方法:

确认正确安装后,一般会在桌面建立快捷方式,点击快捷方式即可进入软件。如没有,可以 开始----所有程序 ---- Xilinx Design Tools ---- ISE Design Suite 14.7

---- EDK-- Xilinx Platform Studio

进入EDK后出现以下界面,这里有很多导航。我们这里选择第一项创建新工程。其他的基本不怎么常用,有兴趣的朋友,可以看着英文注释,自己尝试一下。

2.总线类型选择

在这里,添加工程的所在文件夹。默认会生成一个system。xmp的文件,这里system可以更改名字。地下的两个对话框里是选择以前的工程文件,

打开以前的文件工程,一般也不常用。中间的是重点,这里有两个选项一个是AXI总线,一个是PLB总线。在xilinx 系列FPGA中,早期的版本支持PLB。这个

PLB是为了支持powerpc开发的。在高级一点的FPGA中开始抛弃powerpc。改成内置嵌入式RAM,为了支持改动,有开发了AXI总线。两个总线其实大同小

异。一般初学者可能接触的都是spanart3an。所以这里选择PLB来讲解。

3.go

这里问你是新建还是在以前工程基础上建。我们新建。

4.期间选择

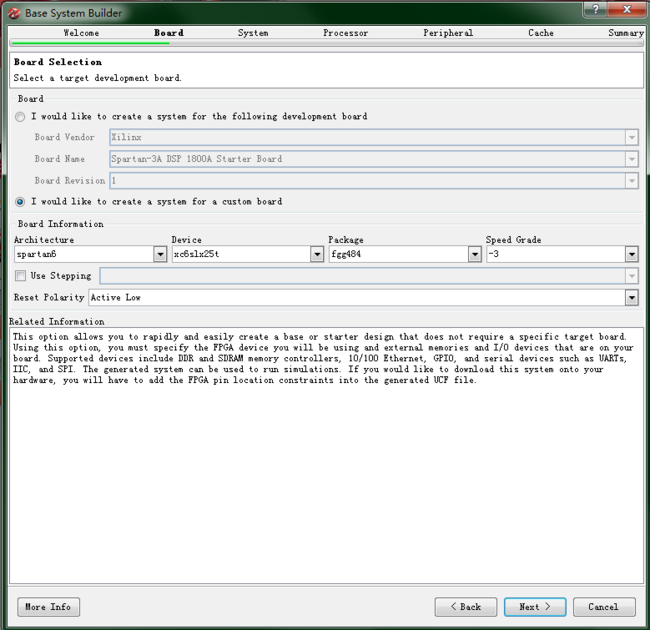

这里需要注意,xilinx自己有很多技术成熟的开发板。所以这里有两个选项,第一个就是问你是不是用的是xilinx自己设计的开发板

如果是,你就在第一项里选择。这里的好处就是,太会把需要的外设,ucf文件什么直接生成,很省心。如果不是现成的板子,是自己做的

等等,就要从下面进行FPGA型号的选择。这个器件手册都有。一般新手在上一项选择就好。这里以底下的为例,是因为,以前写过一段教程

结果有些朋友看完教程不知道如何添加自定义的开发板。在这里也提示一下各位朋友多动脑,不要什么都指着别人告诉你。复位的那个信号

要注意选择。如果工程建立好了,把生成的文件下载到FPGA里,发现不好使,首先要考虑的就是时钟和复位是否有问题。

5.选择核心数

单核就行。

6.时钟,和local memory

这里需要注意,系统时钟50Mhz,这个是可选的,你要看你开发板上是多少。66.67是驱动microblaze的,默认就行,也可以自己改

,要问根据什么改,这个一般要看你的系统带宽什么的。初学者先不要考虑。local memory 这一项是系统内部的存储容量,比如代码什么的

注意的是,在sdk中开发,如果你的代码量比较多,或者需要的存储较大,会提示local memory不够大,到时候大家不要慌就好。一般8kb够用

没底的化可以选大点,以后知道怎么算了,在确切选择就好。

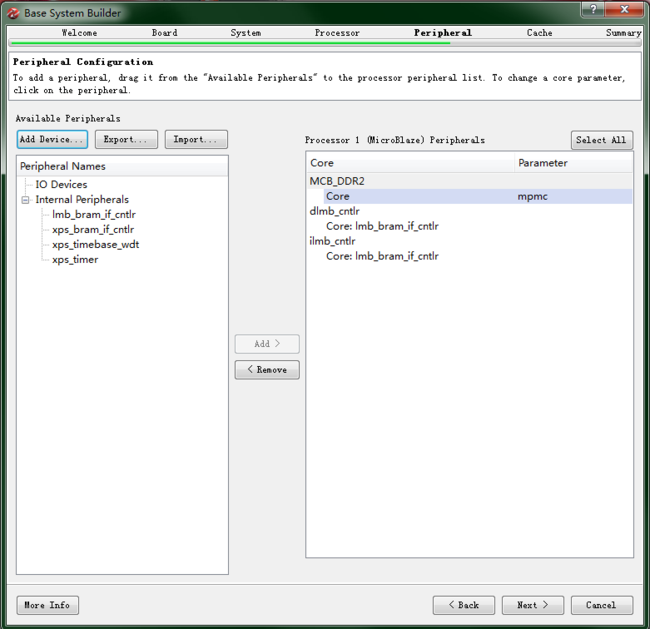

7.添加外设

在这里可以添加外设,不添加也行,在之后的界面也可以,这里dlmb和ilmb是系统必须的,没法删除。

8.容量选择

先前讲过local memory。如果不都大,也可以从你挂载的ddr上分配下来一些。下面的图片就是这个操作。如果在前面外设选择过程

中你没有选择ddr。这里是灰色不可选的。大小自己设置。我这里2k是我做的项目需要,大家不要学。

9.概要

这里会给你个概要信息。看看就行。点完成会出现一个提示信息,是询问你在生成工程前是否已经保证添加ucf和连接jtag线等。

可以不管,建议大家把这些警告什么的看看,不要一出警告就慌了。

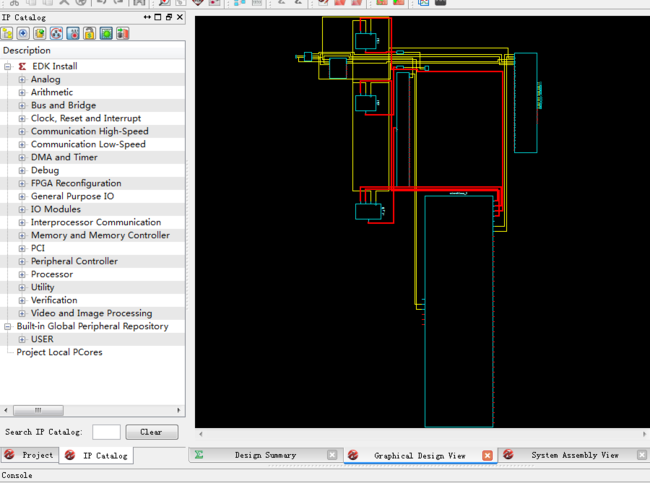

10.界面介绍

这里就到了工程界面了、ipcatalog里面全是iP核,大家可以点开看看,双击看看,以前写过的教程里,这里就简单的说了一句。后来有的朋友

说不知道怎么添加ip。这个,这个,你随便双击个ip,就添加进行啦。多试试吧。添加的情况和结构就在右侧,bus interfaces 下是你都添加了什么ip

,方便的网状结构就是你系统的连接结构,lmb是必有的可以不细研究,plb就是总线,大家可以看看都有什么挂载到这个总线上,其中实心表示已连接

,空心表示没有连接。需要说明一点的就是,在mcb——ddr2下有xcl0这么个东西,这个总线就是用来把内存中的一部分变成local mermory的。

11.端口设置

ports下,是你IP等等的端口,模块互联呀,和外围连接呀,就在这里设置。

12.地址范围

每个设备的地址范围。addresses

13.结构图

在graphical design view 可以看你的系统结构图。

14.生成。bit

在edk中左侧有一个快捷图标,这里不一一解释。以后遇到再说。

其中implement flow是经常用的,也是必用的。如果觉得edk的结构已经搭建好啦。可以分别点击generate netlist生成网表,

在点击generate bitstrem 生成。bit文件,也可以直接点击generate bitstream。这个过程很慢,如果工程大点,变个5,6小时都是

有可能的。上面的都完成后,可以点击export design 关联到sdk。有关sdk的下一篇在讲。如果没有这个快捷方式,在软件上面的选项里面

也可以找到。

总结。

xilinx edk 14.7中有一些瑕疵。以后有时间在统一说一说、

FPGA成神之路 我是 菜鸟0号

hongzhui1111@126.com

2014.05.28