几道题目总结(CMOS)

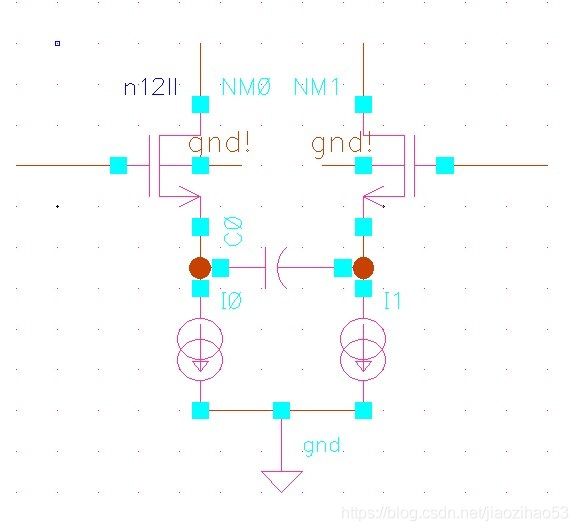

1、分析高通差动对

直观的分析,低频时I0和I1两个电流源输出点开路,则I0和I1各自为一个无穷大的电阻,源级负反馈之后gm为0,放大倍数也为0,所以低频放大倍数为0.

频率升高之后,C0阻抗逐渐减小,I0和I1逐渐短路,此时NM0和NM1的S端近似为虚地,电路变成一个正常的差动对。

2、分析闪烁噪声和什么相关

闪烁噪声产生于栅氧界面,因此等效为栅极的一个电压源:v^2=k/(Cox*W*L*f),所以只和面积有关。

注意这和MOS管的热噪声是不同的,热噪声等效为DS串联的电流:I^2=4kTλ*gm,假设负载电阻为ro,则等效到栅极的输入电压为:I^2*ro*ro/(gm*ro*gm*ro)=4kTλ/gm。

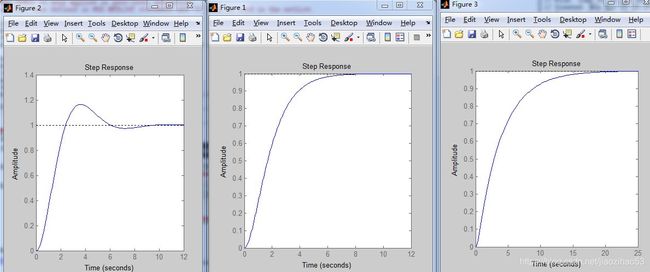

3、关于阻尼因子

阻尼因子的大概表达式为:Hs=A/(s^2+2*k*w0*s+w0^2),即将闭环系统的传递函数写成这个形式,k即阻尼因子。

阻尼因子分别为0.5,1,2时(欠阻尼、临界阻尼和过阻尼),阶跃响应如图:

插入一段代码,有助于分析阶跃响应:

%bode and nyquist plot

syms s;

beta=1;%反馈系数

fs0=1000/(1+s/1000)^2/(1+s/10000);%开环传递函数

fs0_2=fs0/(1+fs0*beta);%闭环传递函数

fs0=expand(fs0);

fs0_2=expand(fs0_2);

[N1,D1]=numden(fs0);

[N2,D2]=numden(fs0_2);

res1=double(fliplr(coeffs(N1,s)));

res2=double(fliplr(coeffs(D1,s)));%提取开环传递函数的系数

ses1=double(fliplr(coeffs(N2,s)));

ses2=double(fliplr(coeffs(D2,s)));%提取闭环传递函数系数

hs0=tf(res1,res2);

hs0_2=tf(ses1,ses2);

figure;

%bode(hs0);

margin(hs0_2);

figure;

step(hs0_2,39e-4);

%margin(hs0);

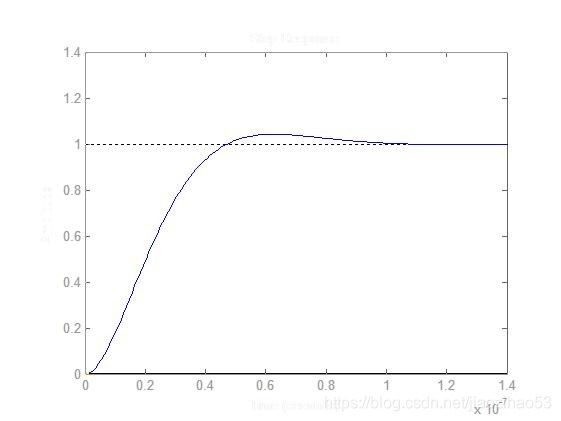

%nyquist(hs0);对于一个两级运放来说,假设增益为1000,w1=50k,w2=100M,这个运放w2~=2GBW。

则开环传递函数为:

Hs=1000/[(1+s/50e3)*(1+s/100e6)],

反馈系数为1时,闭环传递函数为:

H2s=Hs/(1+Hs)=1000*50e3*100e6/(s^2+(50e3+100e6)+1001*50e3*100e6));

其阶跃响应为:

4、共源放大器中源级负反馈电阻的作用?

1中看到,源级负反馈电阻会减小gm,另外,电阻产生热噪声,增加了整个系统的噪声。

好处就是,能够使得增益表达式受gm的影响小一点,但是这种电路的具体应用在哪呢?

5、单端运放的开环增益仿真方法

开环增益的常规仿真用STB,不过加ac=0,DC=∞的电阻和一个ac=∞,dc=0的电阻,环路更清晰。

题目给了一个选项同样具有上述效果:

6、 版图效应:LOD,WPE,OSE,PSE

PSE:poly spacing effect;OSE:oxide spacing effect

即边缘器件和中间器件会有差别,解决方案就是加dummy。

WPE:阱临近效应,产生原因是对阱进行离子注入时,边缘由于散射导致更大的载流子密度,这样导致阱不同位置的MOS管性能不同。Sca、scb、scc参数即来源于此。

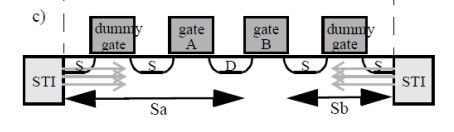

LOD效应:length of diffusion。深亚微米下不再采用会产生“鸟嘴”的隔离技术LOCOS,而是换成STI:shallow trench isolation。这种技术会通过侧壁对阱内部产生压力,对于一个MOS管来说,其受到的应力和其距离阱两侧的STI岛的距离有关,即sa和sb参数。

注:部分参考网页:http://rt2innocence.net/integrated-circuit/wpe-and-lod-effect/

7、jitter对ADC信噪比的影响

对于一个正弦波fin=Asin(wt)输入的ADC,假设抖动的平均值为k(每次采样时钟偏移量的平均值为k),则jitter带来的噪声为:

d(fin)/dt *k=Acos(wt)*w*k(由于jitter是随机的,所以这个表达式代表一个随机信号而不是余弦信号),

则信号和jitter噪声的SNR为:

-20lg(k*w),也就是说输入频率增加一倍,jitter噪声相比输入信号增加6dB;具体SNDR降低了多少还需要结合热噪声和量化噪声来评估。

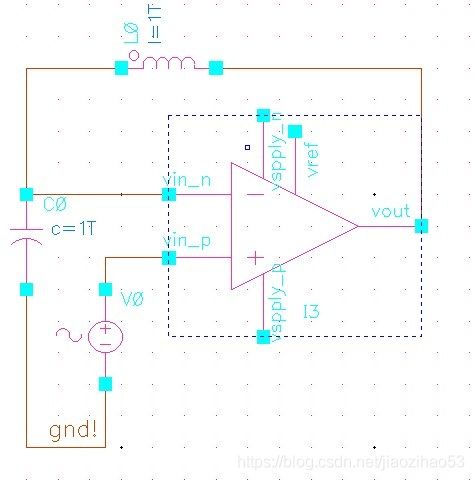

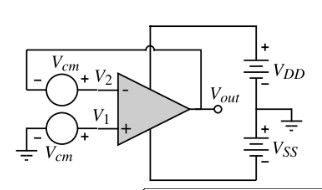

8、单端运放的CMRR仿真

根据此电路图求CMRR:

Vo=Adm*(Vip-Vin)+Acm(Vip+Vin)/2,

Vip=2/3,

(1-Vin)/R=(Vin-Vo)/2R,

综合得到Vo*(Adm+1-Acm/6)=Acm*2/3,由于Acm相对Adm较小,近似得到CMRR=1/Vo*2/3.

参考了这篇网页:

http://rt2innocence.net/integrated-circuit/testbench-for-cmrr-psrr-simulation/的仿真方法:

之前仿真CMRR都是差分输入短接到一个ac小信号上来仿真开环的Acm,而这两种仿真方法都接成了环路,能够获得合理的直流工作点。其中,图1的输出直流点还受到V0和反馈电阻的影响,图2的直流工作点完全由反馈来得到,更适合OTA。