HDMI设计5--GT Transceiver的总体架构整理

在Xilinx中,为HDMI 1.4/2.0 RX/TX Subsystem提供时钟和GTH接口的IP是PHY Controller,Video PHY Controller是为了能够方便使用串行收发器(serial transceivers)和实现专用域的配置。在了解Video PHY Controller之前,我认为需要对GTX/GTH的结构有一定的了解,可以帮助我们更好的了解Video PHY Controller.

Reference:https://china.xilinx.com/content/dam/xilinx/support/documentation/user_guides/ug476_7Series_Transceivers.pdf

1. Xilinx 7系列FPGA高速收发器GTX/GTH的一些基本概念

1.1 GTP, GTX, GTH, GTZ

这四个是Xilinx 7系列FPGA全系所支持的GT, GT的意思是Gigabyte Transceiver(G比特收发器)。通常称为Serides,高速收发器,GT等。

7系列中,按支持的最高线速率排序,GTP是最低的,GTZ是最高的。GTP被用于A7系列,GTZ被用于少数V7系列。从K7到V7,最常见的是GTX和GTH。GTH的最高线速率比GTX稍微高一点。

2.2 TX and RX

TX是Transmitter,表示发送部分。

图 1

RX是Receiver,表示接收部分。

图 2

1.3 PMA and PCS

从TX和RX的结构图可以看到一个共同点:结构图主体分为两个部分,左边的小框图和右边的大框图。

(1)PMA的功能可以简单描述为:串并转换(SIPO and PISO),模拟部分

(2)PCS中的功能,都是并行的数字电路处理。

Note: 理论上说GTX的最小必要单元是PMA,其主要原因就是核心的模拟部分。而PCS理论上可以全部由FPGA的普通逻辑来实现,当然作为硬核提供的PCS功能更多,性能更好,使用更方便。

1.4 Elastic Buffer

一般称为弹性Buffer,基本结构是一个FIFO,常用于处理buffer两边的跨时钟问题。也可以用作:Clock Correction or Channel Bonding.

Note:另外也可以不用Elastic buffer的模式, 称为buffer bypass模式。

1.5 8B10B

通常说的8B10B是一种编码方式。在这里指GTX PCS中的一个模块。

作为编码,8B10B有平衡电平,防止连续1/0的功能。编码分为正负码和特殊K码。最常用的K码是k28.5。8B10B最大的优势在于自带错误检测。当出现8B10B错误时,大概率是链路质量的问题。8B10B的最大劣势是效率比较低,有20%的额外开销,所以常用于低于8G的场景。

Note:作为GTX的一个模块,发送端提供了方便使用的编码接口,接受端提供了方便使用的输出提示,直接使用即可。另外,GTX还提供了Gearbox。除了8B10B外,还有其他很多编码方式,比如64B66B,Gearbox就是为这一类编码做准备的。

1.6 PRBS

PRBS是伪随机序列码,GTX自带了PRBS的生成器(在TX内部)和PRBS接受/检查模块(在RX内部)。ibert中的误码率检查是基于内置的PRBS模块。

从结构图可以看到,PRBS和8B10B没有项目连接的直接关系,所以ibert的测试中没有使用8B10B编码(也没有使用其他编码)。同时内部的PRBS也不支持使用其他编码。所以如果想在GTX外部使用PRBS信号源,可以另外单独做PRBS的生成器和校验模块。

1.7 ibert

ibert是xilinx提供的一个用于GT辅助调试的IP。

2. GT Transceiver的总体架构

前言

对于7系列的FPGA,共有3个系列,每个系列都有各自的高速收发器,称为吉比特收发器,即Gigabit Transceiver, 简称GT。每个系列的GT叫法略有不同,分别为:1,A7的GTP; 2,V7的GTH; 3,K7的GTX;4,少量V7的GTZ。它们之间的区别在于最高线速率不同,GTZ>GTH>GTX>GTP。结构大致相同。

正文

下面以K7而言,梳理一下GTX Transceiver的结构。以XC7K325T为例,其包含总的Transceiver数量以及分布如下:

图 2.1

可见,一个K7325T FPGA的Transceiver总体架构是由:

(1)4个GTX QUAD。

(2)每个GTX QUAD包含4个GTX Channel,故该FPGA包含了16个GTX Channel。

(3)每个GTX Channel对应一个GTX Transceiver。

(4)一个GTX Transceiver由一个GTX Transmitter 和一个GTX Receiver组成。

GTX QUAD的组成如下图:

图 2.2

可见,它是由4个GTXE2_CHANNEL primitive 和1个GTXE2_COMMON primitive组成的。

在GTXE2_COMMON primitive中包含一个QPLL,之所以叫做QPLL,其中的Q含义就是QUAD,即一个GTX QUAD共用的PLL。每个GTXE2_CHANNEL primitive中包含: 1个Channel PLL(CPLL),1个Transmitter,1个Receiver。之所以叫CPLL,含义是每一个Channel共用的PLL。

GTXE2_CHANNEL原语的拓扑结构:

图 2.3

图中上半部分为Transmitter的结构,其由PCS和PMA组成。同理,Receiver也是由PCS和PMA构成。PCS以及PMA使用的时钟来源于CPLL或者QPLL,经过分频后提供给PCS以及PMA,如下图所示。

图 2.4

Transmitter的数据流大致为:FPGA用户逻辑的数据,进入FPGA TX接口,进入PCS,再经过PMA,转换为高速串行数据输出。

图 2.5

Receiver的数据流大致为:数据由PMA部分进入,转换为并行数据后进入PCS,再经过RX接口输出给FPGA用户逻辑处理。

图 2.6

3. GT Transceiver中的重要时钟及其关系--GT Transceiver参考时钟

前言

(1)QPLL以及CPLL的命令来源: QPLL -> Quad-based LC tank PLL, CPLL ->Channel-based ring oscillator PLL。

(2)GTXE2_CHANNEL/GTH2_CHANNEL是例化1个GTX/GTH Transceiver通道的原语。

(3)GTXE2_COMMON/GTH2_COMMON是例化1个QPLL的原语。

(4)GT Quad是由4个GT Transceiver通道,1个QPLL,2个差分输入时钟对,1个模拟输入引脚组成的集合。

图 3.1

正文

在GT Transceiver的总体架构介绍中,提到了transceiver由两部分构成,一部分是PCS,一部分是PMA。暂时可以理解PCS是transceiver的协议部分,较软核的东西,PMA是更偏硬核的东西。

如QUAD的结构图所示,每一个transceiver独有一个CPLL,4个transceiver共有一个QPLL,2个外部参考时钟输入对,和REFCLK Distribution(专用参考时钟布线)。

注意:在QUAD中,GTXE2_CHANNEL/GTHE2_CHANNEL原语以及GTXE2_COMMON/GTHE2_COMMON原语都必须例化,需要注意的是不管使用还是不使用QPLL,GT_COMMON都是要例化的。(这是由工具自动操作的)

外部参考时钟输入对IBUFDS_GTE2就是Transceiver的参考时钟输入端口,1个QUAD有2个参考时钟,我们称之为REFCLK0,REFCLK1,具体用哪一个,根据外部板块设计时,实际给了那一路。

REFCLK Distribution的上下参考时钟引脚分别为南北时钟输入引脚。用于Quad之间共享参考时钟(也就是说,不一定每一个Quad都需要外部参考时钟,有的Quad可以和其他Quad共享参考时钟,而共享的来源就是南北时钟输入引脚)。Quad的南北参考时钟称为GTSOUTHREFCLK和GTNORTHREFCLK。

如果transceiver内部使用QPLL,这时候外部参考时钟就要接入QPLL,如图3.1所示。

图 3.1

总结来说,每个Quad中的GT Transceiver通道有6个可用的参考时钟输入:

(1)两个外部参考时钟输入对,GTREFCLK0和GTREFCLK1

(2)来自Quad上部的两个参考时钟引脚对,GTSOUTHREFCLK0和GTSOUTHREFCLK1。

(3)来自Quad下部的两个参考时钟引脚对,GTNORTHREFCLK0和GTNORTHREFCLK1。

GT Transceiver通道的参考时钟首先来自于上面所说的6个可用时钟来源,之后,这些参考时钟进入QPLL或者CPLL.

QPLL的参考时钟选择详情:

图 3.2

上图所示是一个多路选择器结构,时钟的来源就是刚才说的6个可用的时钟来源,多了一个GTGREFCLK,这个时钟是由内部FPGA逻辑产生的参考时钟。这个输入只用于内部测试。QPLLREFCLKSEL是多路选择器的选择信号,选择那一路输入作为QPLL的输入来源。

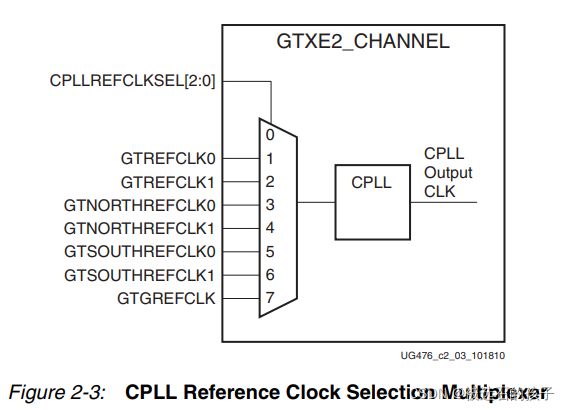

CPLL的参考时钟选择详情:

图 3.3

CPLL与QPLL的输入相似。每个Quad都有两个专用的差分参考时钟输入,可以连接外部时钟源。必须例化IBUFDS_GTE2 primitive才能使用这些专用的参考时钟引脚对。

用户设计将IBUFDS_GTE2输出连接到GTXE2_COMMON/GTHE2_COMMON(包含QPLL)或者GTXE2_CHANNEL/GTHE2_CHANNEL(包含CPLL)原语的GTREFCLK0或者GTREFCLK1,参考时钟选择多路复用器就位于该端口。

参考时钟的使用详情如下图所示:

图 3.4

4. GT Transceiver中的重要时钟及其关系--多个外部参考时钟使用模型

情形1:同一个QUAD中,多个GTX Transceiver使用多个参考时钟

每个QUAD有两个专用的差分时钟输入引脚(MGTREFCLK0[P/N]或者MGTREFCLK1[P/N]),可以连接到外部时钟源。在多个外部参考时钟使用模型中,每个专用的参考时钟引脚对必须例化它们对应的IBUFDS_GTE2,以使用这些专用的参考时钟资源。

如图所示,在同一个QUAD中,多个GTX Transceiver使用多个参考时钟。

图 4.1

第一个外部参考时钟MGTREFCLK0[P/N],用户设计将其IBUFDS_GTE2的输出连接到GTXE2_COMMON和GTX transceiver的GTXE2_CHANNEL原语以及GTHE2_COMMON和GTH transceiver的GTHE2_CHANNEL原语的GTREFCLK0管脚。用户设计需要根据设计需求设置QPLLREFCLKSEL[2:0]和CPLLREFCLKSEL[2:0]

情形2:不同QUAD中,多个GTX Transceiver使用多个参考时钟

图 4.2

一个QUAD的Transceiver通过NORTHREFCLK和SOUTHREFCLK管脚从另一个QUAD访问专用参考时钟。

在每个GTX或GTH Transceiver PLL有多个参考时钟选项的情况下,用户设计需要根据设计需求设置QPLLREFCLKSEL[2:0]和CPLLREFCLKSEL[2:0].

共用参考时钟的必须遵守一下规则:

源QUAD上方的QUAD数量不能超过1个,源QUAD下方的QUAD数量不能超过1个;1个外部参考时钟所驱动的QUAD总数不超过3个,或者驱动的Transceiver不超过12个。

注意:一个时钟针对可以驱动的Transceiver的最大数量是12个。超过12个Transceiver的设计需要使用多个外部时钟引脚,以确保控制抖动的规则得到遵守。当使用多个时钟引脚时,可以用一个外部缓冲器从同一个振荡器驱动它们。对需要动态改变参考时钟源的多速率设计。QPLLREFCLKSEL和CPLLREFCLKSEL端口用于动态选择参考时钟源。在选择之后,用户设计要负责通过高电平有效的CPLLRESET和QPLLRESET端口重置CPLL和QPLL,并负责后续的初始化过程。

5. GT Transceiver中的重要时钟及其关系--CPLL的工作原理介绍

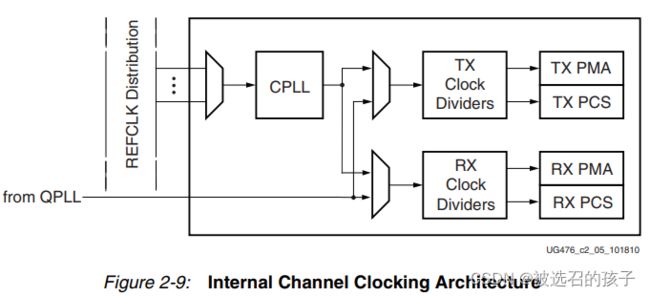

Transceiver内部时钟架构如下:

图 5.1

Transceiver内部时钟来源可以是QPLL也可以是自己的CPLL。其内部TX和RX时钟分频器可以单独从QPLL或CPLL中选择时钟,允许TX和RX数据通道使用不同的参考时钟输入在异步频率工作。这个单独二字表明了TX和RX可以独立的选择时钟分频器的时钟来源。

CPLL的输出,输入到TX和RX的时钟分频器模块,控制PMA和PCS模块使用的串行和并行时钟的生成。如果TX和RX数据通道的运行速率是相同VCO(压控振荡器)频率的整数倍,则可以在它们之间共享CPLL。

CPLL架构的概念结构图如下所示:

图 5.2

其工作原理是:输入时钟在进入相位频率检测器之前可以被除以M的系数。反馈分频器N1和N2决定了VCO的乘法比率和CPLL的输出频率。锁定指示块比较参考时钟和VCO反馈时钟的频率,以确定是否已实现频率锁定。

GTX收发器中的CPLL的额定工作范围在1.6GHz至3.3GHz。GTH收发器中的CPLL的标准工作范围为1.6GHz至5.16GHz。7系列FPGAs Transceiver Wizard根据应用要求选择适当的CPLL设置。

下面的两个公式决定了PLL时钟输出频率以及transceiver的线速率。

其中M,N1,N2和D都是CPLL的一些属性,可以配置。

表 5.1

举例说明: 如下Aurora标准协议的线速率与外部参考时钟之间的关系:

表 5.2

以第一行为例:Line rate = REFCLK*N1*N2*2/(M*D) = 312.5*5*2*2 =6.25 Gbps

注意:一些协议被显示为单速率配置和多速率配置。在单速率配置中,只需要一个线速,参考时钟为该特定线速进行了优化。在多速率配置中,为最高的线路速率选择参考时钟,并选择适当的分频器来支持较低的线路速率。

6. GT Transceiver中的重要时钟及其关系--QPLL的工作原理介绍

每个QUAD都包含一个QPLL,QPLL可以被同一个QUAD内的Transceiver共享,但是不能被其他Quad内的transceiver共享。

注意:当以高于CPLL操作范围的线速率操作通道时,需要使用QPLL。GTXE2_COMMON原语封装了GTX QPLL,并且必须在使用GTX QPLL时实例化。QPLL输出为同一QUAD内的每个transceiver的TX和RX时钟分频器块提供信号,该块控制PMA和PCS块使用的串行和并行时钟的产生。

QPLL架构的结构图如下所示:

图 6.1

大部分结构与CPLL几乎一致。输入的时钟在进入相位频率检测器之前可以被除以一个系数M。反馈分频器N决定了VCO的乘法比率。QPLL的输出频率是VCO频率的1/2。锁定指示块比较参考时钟和VCO反馈时钟的频率,以确定是否已经实现了频率锁定。

QPLL VCO在两个不同的频段内工作。下表描述了这些Band的标准工作范围。

表 6.1

当选择低频段VCO时,高频段VCO会自动断电,反之亦然。7系列FPGA Transceiver向导根据应用要求选择适当的频段和QPLL设置。下面两个公式分别决定了QPLL的输出频率以及transceiver的线速率。

其中,N,M以及D表示QPLL分频器的属性,如下表:

表 6.2

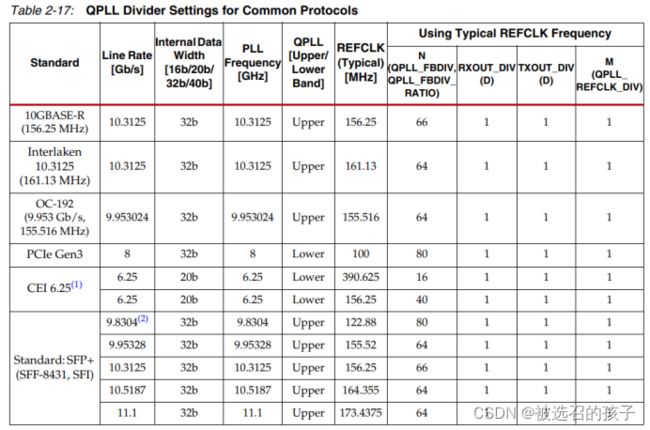

下面是几个通用协议的QPLL分频器属性设置值:

表 6.3

7. GT Transceiver中的重要时钟及其关系--TXUSERCLK以及TXUSERCLK2的用途与关系

图 7.1

首先是框图最右边的FPGA TX Interface,即FPGA TX接口,它是FPGA通往GT Transceiver TX数据通路的通道。The FPGA TX接口包含两个并行时钟,TXUSERCLK和TXUSERCLK2。TXUSERCLK是GTX/GTH transceiver中PCS逻辑的内部时钟。TXUSERCLK所需要的速率取决于GTXE2_CHANNEL/GTHE2_CHANNEL源的内部数据通路宽度和GTX/GTH发射器的TX线速率。

下面公式显示了如何计算TXUSERCLK的所需速率。

TXUSERCLK2是进入GTX/GTH Transceiver TX端所有信号的主要同步时钟。进入GTX/GTH Transceiver TX端的大多数信号都是在TXUSERCLK2的正沿上采样的。接口上的并行时钟(TXUSERCLK2)的速率由TX线路速率,TXDATA端口的宽度以及是否启用8B/10B 编码决定。

TXUSERCLK2和TXUSERCLK有一个基于TX_DATA_WIDTH和TX_INT_DATAWIDTH设置的固定速率关系。下图显示了每个TX_DATA_WIDTH和TX_INT_DATAWIDTH值与TXUSERCLK2和TXUSERCLK之间的关系。

注意:当线路速率大于6.6Gb/s时,需要一个4字节的内部数据通路,将TX_INT_DATAWIDTH设置为1。

表 7.1

注意:对于TXUSRCLK和TXUSRCLK2,必须遵守以下关于时钟之间关系的规则。-> TXUSRCLK和TXUSRCLK2必须是正边对齐的,它们之间的偏移尽可能小。因此,低偏移的时钟资源(BUFG,BUFH,BUFR)应被用来驱动TXUSRCLK和TXUSRCLK2。-> 即使它们可能以不同的频率运行,TXUSRCLK,TXUSRCLK2和Transmitter参考时钟必须有相同的振荡器作为其来源。因此,TXUSRCLK和TXUSRCLK2必须是发射器参考时钟的倍频或分频版本。

8. GT Transceiver中的重要时钟及其关系--TXUSRCLK以及TXUSRCLK2的产生

前言

(1)TXUSRCLK以及TXUSRCLK2的作用以及关系

-> TXUSRCLK是GTX/GTH transceiver中PCS逻辑的内部时钟。

-> TXUSRCLK2是进入GTX/GTH transceiver TX端所有信号的主要同步时钟。

(2)TXUSRCLK和TXSURCLK2必须遵守的时钟关系

-> TXUSRCLK和TXUSRCLK2必须是正边对齐的,它们之间的偏移尽可能小。因此,低偏移的时钟资源(BUFG,BUFH和BUFR)应被用来驱动TXUSRCLK和TXUSRCLK2。

-> 即使它们可能以不同的频率运行,TXUSRCLK,TXUSRCLK2和Transmitter参考时钟必须有相同的振荡器作为其来源。因此,TXUSRCLK和TXUSRCLK2必须是发射器参考时钟的倍频或者分频版本。

正文

根据TXUSRCLK和TXUSRCLK2的频率,有不同方式可以使用FPGA时钟资源来驱动TX接口的并行时钟。在这些例子中,TXOUTCLK来自MGTREFCLK0[P/N]或者MGTREFCLK1[P/N]

TXOUTCLK在2字节或4字节模式下驱动GTX/GTH收发器TX如下图:

图 8.1

TXOUTCLK用于驱动单通道配置中的2字节模式(TX_DATA_WIDTH=16或20,TX_INT_DATWIDTH=0)或4字节模式(TX_DATA_WIDTH=32或40,TX_INT_DATWIDTH=1)的TXUSRCLK和TXUSRCLK2。在这两种情况下,TXUSRCLK2的频率都等于TXUSRCLK.

图 8.2

TXOUTCLK在4字节或8字节模式下驱动GTX/GTH收发器TX,如下图所示:

图 8.3

TXOUTCLK用于驱动TXUSRCLK2的4字节模式(TX_DATA_WIDTH=32或40,TX_INT_DATWIDTH=0)或8字节模式(TX_DATA_WIDTH=64或80,TX_INT_DATWIDTH=1),在这两种情况下,TXUSRCLK2的频率都等于TXUSRCLK频率的一半。

MMCM是位于器件上半部的时钟管理单元(CMT)的一部分,它只能驱动器件上半部的BUFG。同样,位于下半部的MMCM也只能驱动下半部的BUFG.注意:在Kintex-7器件中,需要BUFH/BUFG。在Virtex-7器件中,BUFH/BUFG是不需要的。

图 8.4

如上图所示,TXUSRCLK以及TXUSRCLK2都来自于TXOUTCLK。注意:1, TXOUTCLK在2字节或4字节模式下驱动GTX/GTH收发器TX;2, TXOUTCLK在4字节或8字节模式下驱动GTX/GTH收发器TX;

以上分别对应两种情况-> 1, 单lane; 2,lane

9. GT Transceiver中的重要时钟及其关系--RXUSERCLK和RXUSER_CLK2的生成

前言

USRCLK以及USRCLK2必须成对,有TXUSERCLK和TXUSER_CLK2那么与之对应的时钟就是RXUSRCLK和RXUSR_CLK2.

正文

如下图所示为RX端的架构图。

图 9.1

FPGA RX接口是GT Transceiver的RX数据路径通道。应用程序通过GTX/GTH收发器接受数据,在RXUSRCLK2的正沿从RXDATA端口读取数据。

接受处的并行时钟(RXUSRCLK2)的速率由RX线路速率,RXDATA端口的宽度以及是否启用8B/10B编码决定。在某些工作模式下,必须为发射器的内部PCS逻辑提供第二个并行时钟(RXUSRCLK)。

RXUSRCLK以及RXUSRCLK2的产生

FPGA的RX接口包括两个并行时钟RXUSRCLK和RXUSRCLK2。RXUSRCLK是GTX/GTH发射器中PCS逻辑的内部时钟。RXUSRCLK所需的速率取决于GTXE2_CHANNEL/GTHE2_CHANNEL原语的内部数据通路宽度和GTX/GTH发送器的RX线速率。下面公式显示了如何计算RXUSRCLK的所需速率。

RXUSRCLK2是进入GTX/GTH收发器RX侧的所有信号的主要同步时钟。大多数进入GTX/GTH收发器RX端的信号都是在RXUSRCLK2的正边沿进行采样。RXUSRCLK2和RXUSRCLK有一个基于RX_DATA_WIDTH和RX_INT_DATAWIDTH设置的固定速率关系。

下表显示了每个RX_DATA_WIDTH和RX_INT_DATAWIDTH值的RXUSRCLK2和RXUSRCLK之间的关系。大于6.6Gb/s的线速率需要通过设置RX_INT_DATAWIDTH为1来使用一个4字节的内部数据通路。

表 9.1

对于RXUSRCLK和RXUSRCLK2,必须遵守这些关于时钟之间关系的规则:

-> RXUSRCLK和RXUSRCLK2必须是正边对齐,它们之间的偏移尽可能小。因此,应使用低偏移的时钟资源(BUFG和BUFR)来驱动RXUSRCLK和RXUSRCLK2。

-> 如果通道被配置成由同一个振荡器驱动发射器和接收器的参考时钟,TXOUTCLK可以用来驱动RXUSRCLK和RXUSRCLK2,其方式与驱动TXUSRCLK和TXUSRCLK2相同。当时钟校正被关闭或RX缓冲器被旁路时,必须使用RX相位校准来校准串行时钟和并行时钟。

-> 如果单独的振荡器驱动通道上发射器和接收器的参考时钟,并且不使用时钟校正,RXUSRCLK和RXUSRCLK2必须由RXOUTCLK驱动(RXOUTCLKSEL = 3'b010用于RXOUTCLKPMA),并且必须使用相位校正电路。

-> 如果使用时钟校正,RXUSRCLK和RXUSRCLK2可以由RXOUTCLK或TXOUTCLK提供源