HDMI设计3--HDMI 1.4/2.0 Transmitter Subsystem IP

Reference: https://china.xilinx.com/content/dam/xilinx/support/documentation/ip_documentation/v_hdmi_tx_ss/v3_2/pg235-v-hdmi-tx-ss.pdf

对于支持4K视频的HDMI接口,可以参考Xilinx给出的HDMI1.4/2.0 Transmitter Subsystem, HDMI1.4/2.0 Receiver Subsystem, Video PHY Controller这三个IP。以下是个人参考相应文档后对这三个IP设计细节的理解。

1. 序

首先,对于HDMI 1.4/2.0 Transmitter Subsystem IP是一个集成的IP子系统,整个IP以HDMI 1.4/2.0 Transmitter core为核心。

图 1

如图1所示为,左侧的TX Subsystem是整个HDMI 1.4/2.0 Transmitter Subsystem的基本架构(该架构的video interface为axi-stream,因此,会有个stream-to-video bridge;如果是native interface则不需要stream-to-video bridge)。

1,TX Subsystem的基本构成。整个TX Subsystem由HDMI TX Core, AXI4-Stream to Video Bridge, Video Timing Controller(产生视频或者图像时序信息),HDCP(用于视频数据的加密,主要应用于3D视频居多),AXI4 Interconnect(用于互联内部多个axi4-lite接口,以便CPU软核或者硬核进行Subsystem中各IP的重配置)。

2,TX Subsystem的时钟关系。整个TX Subsystem存在两个跨时钟域的问题。第一个是axis_video_aclk时钟域到video_clk时钟域。axis_video_aclk时钟是axi4-stream video的launch时钟,而video_clk时钟是native video也就是video bridge的输出数据时钟。第二个是在HDMI TX Core, 其输入数据时钟是video clk,输出数据时钟是Link clk。这里要注意的是时钟来源的问题,axis_audio_aclk,axis_video_aclk两个时钟在系统设计时根据需求自定义。而video_clk,link clk则是通过Phy Controller来生成。

1.1 支持的功能

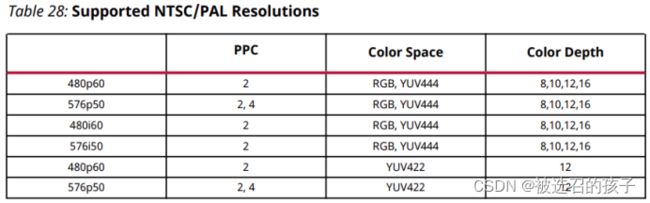

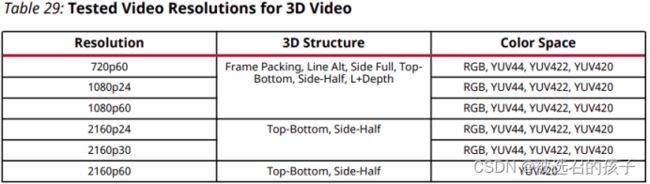

HDMI Transmitter Subsystem支持的功能有:兼容HDMI1.4/2.0协议;每个时钟2个或者4个像素采样;支持8,10,12和16-bit的颜色深度;支持RGB,YUV444,YUV422,YUV420的颜色格式;支持AXI4-Stream video或者native video格式输入;音频通道支持32通道;支持HBR(High bit rate) Audio;支持3D Audio;可选择的支持HDCP 2.4/1.4加密;支持信息帧;支持DDC(Data Display Channel);支持热插拔检测(HPD);支持DDC clock stretching;支持3D视频;Optional video over AXIS compliant NTSC/PAL support; Optional video over AXIS compliant YUV420 support; Optional HPD active polarity; Supports HDR video transport (Dynamic Range and Mastering info frames)

1.2 不支持的功能

Lip sync; CEC; HEAC; Dual view; Multi-stream audio

关于该IP的License,如果购买了比较高级的板子比如(zcu106),可以获得一个为期一年使用权的license,如果没有,则可以去官网申请Hardware Evaluation license,该license可以使用3个月。如果前两者都没有,则需要购买license。

2. 详细规格说明(Product Specification)

图 2

如图2所示,对于HDMI TX Subsystem, 接口有视频数据接口Video Interface(AXI4-Stream/Native Video), 音频数据接口(可以不使用)Audio Interface(AXI4-Stream), CPU控制接口CPU Interface(AXI4-Lite), 来自PHY Layer的三个接口信号(Link clock,Link data, Video clock),用于HDCP加密的HDCP key值数据接口,DDC接口,HPD接口,和一些其他的信息接口。

HDMI TX Subsystem这个IP可以在例化时,在Vivado Integrated Design Environment(IDE)里面进行一些参数的设置。比如video interface是选择AXI4-Stream或者是Native Video(DE Vector/no-DE Vector),HDCP的支持选择等。

2.1 Video interface

HDMI 1.4/2.0 TX Subsystem 支持三种视频数据接口:AXI4-Stream Video Interface, Native Video Interface, Native Video(Vectored Data Enable) Interface.

(1)AXI-Stream Video Interface于Native Video Interface的区别是AXI-Stream Video Interface只传输有效像素数据(也就是active pixels),没有Hsync,Vsync这些时序信号,因此,当选择AXI-Stream Video Interface时, 整个Subsystem会加入一个AXI-Stream video to Bridge的接口转换IP和一个提供视频时序(Timing)的Video Timing Controller IP。对于VTC IP, 该IP可以由CPU来控制,当输出视频时序发生变化后,CPU通过实际视频时序去配置VTC IP,以产生正确的视频时序信息。

(2)Native Video Interface相比AXI-Stream Video Interface则是具有了Hsync,Vsync等时序信号,因此在选择Native Video Interface后,Subsystem中不用集成AXI-Stream video to Bridge IP和Video Timing Controller IP, 相比之下节省了资源。Native Video Interface中又分成了两种接口形式: Native Video(Vectored Data Enable)相比Native Video多出了字节使能信号,用于指明数据总线上那些像素数据是有效的。因为,在IP支持2或4像素传输,对于视频分辨率中的像素数目不能被4整除的,则在数据总线上将存在无效数据,因此,Vectored Data Enable信号用于标识数据总线上的数据是否有效。避免采样无效数据。

2.2 HDCP

不论是使用Native video Interface还是AXI-Stream Video Interface。HDMI 1.4/2.0 TX Subsystem在内部都可以选择是否支持HDCP1.4或者HDCP2.3加密方式。这里要注意的是,如果要使用HDCP功能,需要独立于HDMI 1.4/2.0 Transmitter的License,就是需要两个License。

2.3 数据位宽(Data width)

对于Video Interface上的数据位宽,是在例化IP是通过设置Number of Pixels Per Clock on Video Interface和Max Bits Per Component两个参数决定的。这里需要理解这两个参数生成的像素数据位宽和HDMI 1.4b协议中以8-bit像素数据进行DC编码的过程。

需要注意的是,赛灵思官方对于HDMI 1.4/2.0 TX Subsystem只提供了API函数而没有提供内部具体的寄存器信息。

整个subsystem会将视频数据和音频数据转换成HDMI stream, 然后HDMI stream 转换成Link stream进入PHY controller后,由PHY controller将Link-Stream转换TMDS信号输出。

2.4 Audio Clock Regeneration Signals

因为audio clock regeneration architecture并没有在HDMI 1.4/2.0 TX Subsystem中,因此,在使用HDMI 1.4/2.0 TX Subsystem IP需要用到Audio Clock Regeneration时,需要根据audio clock的要求(采样频率,时钟抖动等),通过内部PLL或者外部时钟源来产生audio clock。需要注意的时,当HDMI 1.4/2.0 TX Subsystem用于DVI模式,或者不需要传输Audio时,该ACR inputs信号可以被忽略。可以自定义将它们接到一个固定的值。(比如,将acr_cts, acr_n, acr_valid固定为0)。

2.5 Display Data Channel (DDC)

DDC本质就是I2C总线,用来作为HDMI Source去读取HDMI Sink中的EDID/E-EDID, 以便HDMI Source知道HDMI Sink支持什么样的功能(比如,支持什么样的分辨率,是否支持3D视频显示,支持怎样的3D帧格式等,具体的可以看关于HDMI的EDID/E-EDID内容)。

2.6 Status and Control Data Channel (SCDC)

HDMI 1.4/2.0 TX Subsystem提供了一个偏移地址为0x20的SCDC register用于TMDS的设置。这个寄存器是支持HDMI2.0所提供的。该寄存器中有两位:

-> Bit 1: TMDS_Bit_Clock_Ratio

-> Bit 0: Screambling_Enable

(1)Screambling_Enable

这个位是为了HDMI 2.0 video进行加扰的标志位。HDMI 2.0相比HDMI1.4 video不同的是,HDMI2.0在进行对video数据做DC平衡编码前,还有一个加扰的过程。使用XV_HdmiTx_Scambler(InstancePtr->HdmiTxPtr)来对HDMI 2.0 video使能scrambler(加扰器),和对HDMI1.4 video禁止scrambler。

(2)TMDS_Bit_Clock_Ratio

使用V_HdmiTx_ClockRatio(InstancePtr->HdmiTxPtr)来为HDMI 2.0 video设置TMDS clock ratio bit. 使用XV_HdmiTx_ShowSCDC(XV_HdmiTx *InstancePtr)可以读出HDMI TX subcore所连接的HDMI Sink中的SCDC寄存器的值。

2.7 Hot Plug Detect

热插拔检测信号是HDMI source和HDMI sink设备之间的一种通信机制。当HDMI线连接到HDMI source和HDMI sink之间时,将会产生一个类似脉冲信号的机制,通知HDMI source可以去和HDMI sink通信了,比如这时HDMI Source通过DDC通道去读取HDMI sink里面的EDID/E-EDID.

2.8 HDCP

HDCP是用于保证视频类容在两个设备之间传输的安全性的一种加密机制。在HDMI 1.4/2.0 TX Subsystem中有4种HDCP加密方案的选择,可以通过Vivado IDE来进行配置。第一种是不使用HDCP;第二种是只使用HDCP 1.4; 第三种是只使用HDCP 2.3; 第四种是HDCP 1.4和HDCP 2.3都使用。HDCP 1.4和HDCP 2.3不同的是,HDCP 2.3是用于加密高清视频类型(Ultra-High Definition)的,而HDCP 1.4是用于加密低分辨率的视频内容,同时也有出于兼容性的考虑。

图 3

如图3所示,HDCP 1.4 Transmitter和HDCP 2.3 Transmitter首尾相连,由图3可知,首先视频数据流由HDMI TX Core, 此时并未被加密,然后未加密的视频数据流再流入HDCP 1.4 Transmitter和HDCP 2.3 Transmitter,这里要注意对于HDCP 1.4Transmitter和HDCP 2.3 Transmitter只有一个是使能的,意思就是在例化HDMI TX Subsystem时,可以只选择实现HDCP 1.4和HDCP 2.3中的一种加密方案,但是选择两种加密方案都包含时,在HDMI TX Subsystem实际运行中,需要通过CPU去选择使能那一种加密方案,而不能两者都使能。

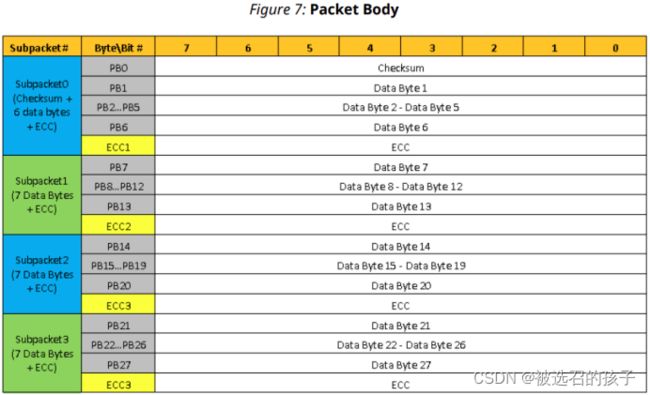

2.9 AUX Packets

在HDMI 1.4b中已经知道,在Data Island Period中,会传输附加视频信息包。该包包含有4字节的包头(packet header)和32字节的包体(packet contents).

在表中,Packet Type右上角标识为1,表示该数据包被硬件直接处理,标识为2,表示该数据包需要由软件来根据内容进行处理。

关于各种Aux packet的具体格式和字段信息,可以参考HDMI 1.4b。这里,主要了解在Xilinx的SDK中调用那些API函数来处理Aux packets.

(1)Sending auxiliary packets

XV_HdmiTxSs_SendGenericAuxInfoframe(XV_HdmiTxSs *InstancePtr, void *Aux);使用该API函数在SDK中发送aux packets。InstancePtr是HDMI 1.4/2.0 TX Subsystem的指针,Aux是包含了36个字节的完整AUX packet.

AUX packet在软件中的数据结构定义如下:

typedef union{

u32 Data;

u8 Byte[4];

}XHdmiC_AuxHeader;

typedef union{

u32 Data[8];

u8 Byte[32];

}XHdmiC_AuxData;

typedef struct{

XHdmiC_AuxHeader Header;

XHdmiC_AuxData Data;

}XHdmiC_Aux;2.10 InfoFrames

关于在HDMI 中InfoFrames具体格式和字段信息的定义,可以参考HDMI 1.4b.这里,我们主要关注在软件中对于Vendor Specific InfoFrame(VSIF), Auxiliary Video Information(AVI) InfoFrame, Auido InfoFrame, Dynamic Range and Mastering InfoFrame这四种帧格式的数据结构定义。

(1) AVI InfoFrame

typedef struct XHDMIC_AVI_InfoFrame{

unsigned char Version;

XHdmiC_Colorspace ColorSpace;

u8 ActiveFormatDataPresent;

XHdmiC_BarInfo BarInfo;

XHdmiC_ScanInfo ScanInfo;

XHdmiC_Colorimetry Colorimetry;

XHdmiC_PicAspectRatio PicAspectRatio;

XHdmiC_ActiveAspectRatio ActiveAspectRatio;

unsigned char Itc;

XHdmiC_ExtendedColorimetry ExtendedColorimetry;

XHdmiC_RGBQuantizationRange QuantizationRange;

XHdmiC_NonUniformPictureScaling NonUniformPictureScaling;

unsigned char VIC;

XHdmiC_YccQuantizationRange YccQuantizationRange;

XHdmiC_ContentType ContentType;

XHdmiC_PixelRepetitionFactor PixelRepetition;

u16 TopBar;

u16 BottomBar;

u16 LeftBar;

u16 RightBar;

}XHdmiC_AVI_InfoFrame;(2) Audio InfoFrame

typedef struct XHdmiC_Audio_InfoFrame{

unsigned char Version;

XHdmiC_AudioChannelCount ChannelCount;

XHdmiC_AudioCodingType CodingType;

XHdmiC_SampleSize SampleSize;

XHdmiC_SamplingFrequency SampleFrequency;

u8 CodingTypeExt;

u8 ChannelAllocation;

XHdmiC_LFEPlaybackLevel LFE_Playback_Level;

XHdmiC_LevelShiftValue LevelShiftVal;

unsigned char Downmix_Inhibit;

}XHdmiC_AudioInfoFrame;(3) Vendor Specific InfoFrame (VSIF)

typedef struct{

u8 Version;

u32 IEEE_ID;

XHdmiC_VSIF_Video_Format Format;

union{

u8 HDMI_VIC;

XHdmiC_3D_Info Info_3D;

};

}XHdmiC_VSIF;(4) Dynamic Range and Mastering InfoFrame

typedef struct XHdmiC_DRM_InfoFrame{

XHdmiC_DRM_EOTF EOTF;

XHdmiC_DRM_Static_Metadata_Descp_Id Static_Metadata_Descriptor_ID;

struct{

u16 x,y;

}disp_primaries[3];

struct{

u16 x,y;

}whit_point;

u16 Max_Disp_Mastering_Luminance;

u16 Min_Disp_Mastering_Luminance;

u16 Max_Content_Light_Level;

u16 Max_Frame_Average_Light_Level;

}XHdmiC_DRMInfoFrame;当将上述的各种帧数据结构进行更新赋值后,调用一下对应帧的转换API函数,可以将不同类型帧的数据结构,转化为统一的Aux packet,在构造Aux packet的同时,将会为包头(packet header)和包体(packet body)计算对应的CRC.之后可以调用发送Aux packet来控制HDMI TX发送Aux packet给HDMI RX。

XHdmiC_Aux XV_HdmiC_AVIF_GeneratePacket(XHdmiC_AVI_InfoFrame *infoFramePtr);

XHdmiC_Aux XV_HdmiC_AudioIF_GeneratePacket(XHdmiC_AudioInfoFrame *AudioInfoFrame);

XHdmiC_Aux XV_HdmiC_VSIF_GeneratePacket(XHdmiC_VSIF *VSIFPtr);

void XV_HdmiC_DRMIF_GeneratePacket(XHdmiC_DRMInfoFrame *DRMInfoFrame,XHdmiC_Aux *aux);2.11 General Control Packet

General Control Packet主要是由硬件来直接处理的,但是也能被软件获得以便调整系统功能。

General Control Packet会由HDMI 1.4/2.0 TX Subsystem根据视频流自动生成,并在vsync信号到来的384个时钟周期内发送出去。以下4个API用于设置或清零AVMUTE field.

void XV_HdmiTxSs_SetGcpAvmuteBit(XV_HdmiTxSs *InstancePtr);

void XV_HdmiTxSs_ClearGcpAvmuteBit(XV_HdmiTxSs *InstancePtr);

void XV_HdmiTxSs_SetGcpClearAvmuteBit(XV_HdmiTxSs *InstancePtr);

void XV_HdmiTxSs_ClearGcpClearAvmuteBit(XV_HdmiTxSs *InstancePtr);2.12 Port Descriptions

对于HDMI 1.4/2.0 TX Subsystem的接口定义,基本如图2所示,关于具体的信号接口,可以Reference: pg235-v-hdmi-tx-ss

3. 设计细节

因为,在我的设计中只针对于Video Data.,并没有音频(Audio)的传输需求,因此关于Audio Data的就忽略。

3.1 Video Input Stream Interface

在此之前,曾说过,在设置HDMI 1.4/2.0 TX Subsystem时,会对Number of Pixels Per Clock on Video Interface和Max Bits Per Component两个参数进行设置。Number of Pixels Per Clock on Video Interface的值表示同时传输多少个像素数据,可以选择2个或者4个;Max Bits Per Component的值表示一个像素用多大的数据位表示(这里指的是HDMI系统中固定位宽,需要和实际传输的视频像素的颜色深度(Color Depth)结合考虑)。

当Max Bits Per Component比Actual Bits Per Component大时,也就是Actual Bits Per Component的所有位数都可以放到Max Bits Per Component大小的Video数据线上,这时涉及的是,是如何放上去的。采用的是高位对齐,低位补零的机制,即Actual Bits的最高位与Max Bits的最高位对齐,不足的用零补充。

当Max Bits Per Component比Actual Bits Per Component小时,也就是Actual Bits Per Component的所以位数无法都放到Max Bits Per Component大小的Video 数据线上,这时涉及的是,如何截断多余的像素位数。采用的是高位对齐,低位截断的机制,即Actual Bits的最高位与Max Bits的最高位对齐,多余的低位直接截断。

3.2 隔行扫描视频(Interlaced Video)

HDMI 1.4/2.0 TX Subsystem既支持逐行扫描(progressive)也支持隔行扫描(interlaced)。目前主流的视频显示都是逐行扫描显示,逐行扫描方式是最简单的扫描方式,就是每一帧图像由电子束顺序地一行接着一行连续扫描而成。隔行扫描就是把一个视频帧在垂直方向上分成两个视频帧,由原帧的奇数行组成的帧称为奇数场,由原帧的偶数行组成的帧称为偶数场。奇数场和偶数场交错组成一个视频帧,采用这种扫描方式,其行扫描频率是逐行扫描时的一半。

当使用AXI4-Stream Interface时,使用fid信号来对齐每一场数据。当使用Native Interface时,使用HSYNC和VSYNC信号来标识(这里我也不清楚,只是使用了fid信号来标识)

这里要注意的是对于线速率低于25MHz的分辨率,在传输的时候需要进行像素重复的机制(pixel-repetition scheme)。Pixel-repetition只能用于AXI4-Stream Interface,同时,pixel-repetition只支持RGB和YUV444颜色空间,而不支持YUV422.

4. Clocking

在HDMI TX Subsystem中,存在5个独立的时钟,分别是s_axi_cpu_aclk, s_axis_video_aclk, s_axis_audio_aclk, link_clk 和video_clk。

这里要注意的是,audio streaming clock必须大于或等于audio sample clock的128倍。而且因为audio clock regeneration并不是HDMI 1.4/2.0 TX Subsystem的一部分,所以需要使用内部PLL或者外部时钟源生成提供。

如图所示,标识出了5个时钟,其中TMDS clock, Video clock, Link clock是实际存在的时钟,而Data clock,Pixel clock这两个时钟则是运算计算推导的时钟。这里可以根据带宽平衡来了解各时钟之间的关系。所谓带宽平衡指的是模块的输入数据率和输出数据率相等。

输入总线位宽x输入时钟频率 = 输出总线位宽x输出时钟频率

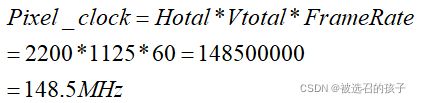

首先,我们首先知道是视频格式信息,比如分辨率,帧率。通过分辨率和帧率,我们可以计算出Pixel clock.其中像素颜色深度BPC为12,每次传输像素值PPC为2

如图,是1080p60的时序信息,以此可以计算出Pixel clock的值。

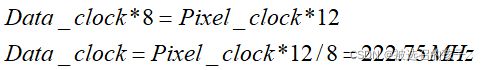

接着,我们可以通过Pixel clock计算出Video clock,由带宽平衡的公式计算过程如下:

同理,我们可以通过Pixel clock计算出Data clock,这里有点需要注意的时,在HDMI对video数据进行DC平衡编码时,始终是将8 bit数据编码成10 bit数据,然后通过TMDS data channel 串行输出,不论像素颜色深度是8,10,12。所以,这里涉及了如何用8 bit数据单元对10 bit,12 bit,14 bit的像素颜色深度进行package,会单独进行介绍,这里我们只要知道Data clock这里的数据位宽固定为10 bit。在这里有个细节就是,在Data clock中的是10 bit 位宽数据,在Data clock数据进入Pixel clock时,会被解码成 8 bit位宽数据。具体可参考:pg235-v-hdmi-tx-ss和HDMI 1.4b Spec.由带宽平衡的公式计算过程如下:

然后,由Data clock来计算Link clock,由带宽平衡公式计算如下:

之后,计算TMDS clock, TMDS clock是采用由数据率(data rates)进行分段计算的。同时,记得TMDS通道每次传输1 bit数据,因此,数据位宽是1。

最后,就计算出了PHY controller给HDMI TX Subsystem的video clock和link clock时钟值,以及为了产生这两个时钟所需要的TMDS clock值,对应于Video PHY Controller的tx_gtrefclk clock p/n。

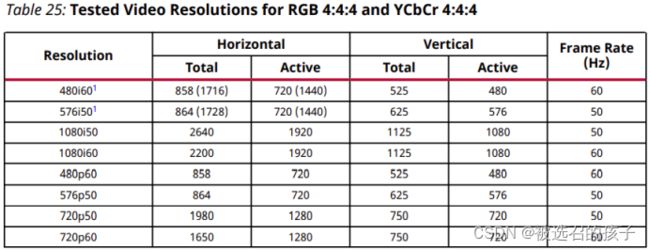

5, Test Video Resolutions

以下所示Xilinx官方为HDMI1.4/2.0 TX Subsystem在不同颜色空间和分辨率进行的测试。

6. 应用软件相关(Application Software Development)

6.1 HDMI TX Subsystem Flow

HDMI 1.4/2.0 TX Subsystem提供了一系列的API函数给应用程序去使用。当HDMI 1.4/2.0 TX Subsystem的中断产生时,会调用相应的回调函数去配置HDMI 1.4/2.0TX Subsystem的各种参数,当然,也会去配置PHY Controller。

在HDMI 1.4/2.0 TX Subsystem中通常会响应两种事件:

(1)来自HDMI sink设备的热插拔信号(Hot-plut signal-HPD)

(2)应用软件去指定视频流格式如何改变。

HDMI 1.4/2.0 TX Subsystem中的基本流程如下图所示:

这里忽略HDCP的内容,因为HDCP是一个比较大的独立模块。

6.2 Video PHY Controller

因为HDMI 1.4/2.0 TX Subsystem是和Video PHY Controller成对存在的,毕竟Video PHY Controller需要通过TMDS Clock去产生HDMI 1.4/2.0 TX Subsystem所需要的link clock和video clock.

(1)在软件中,要能用到Video PHY Controller需要加入xvphy.h头文件

(2)接着,定义phy对象: XVphy Vphy;

(3)定义配置对象指针: XVphy_Config *XVphyCfgPtr;

(4)初始化Video PHY Controller/HDMI GT Subsystem

XVphy_Config *XVphy_LookupConfig(u16 DeviceId);

u32 XVphy_HdmiInitialize(XVphy *InstancePtr,u8 QuadId,XVphy_Config *CfgPtr,u32 SystemFrequency);SystemFrequency是系统时钟,具体值可以在xparameters.h中找到。需要留意的是:Xilinx推荐在将HDMI 1.4/2.0 TX Subsystem初始化完成后再初始化PHY Controller.

6.3 HDMI 1.4/2.0 TX Subsystem

当硬件系统集成了HDMI1.4/2.0 TX Subsystem这个IP后,在软件中,也是向PHY Controller一样去映射配置。

(1) 在软件中,要能用到HDMI 1.4/2.0 TX Subsystem需要包含头文件xv_hdmitxss.h

(2) 接着,定义HDMI 1.4/2.0 TX的对象:XV_HdmiTxSs HdmiTxSs

(3) 定义配置对象指针:XV_HdmiTxSs_Config *XV_HdmiTxSs_ConfigPtr

(4) 初始化HDMI 1.4/2.0 TX Subsystem

XV_HdmiTxSs_Config* XV_HdmiTxSs_LookupConfig(u32 DeviceId);

int XV_HdmiTxSs_CfgInitialize(XV_HdmiTxSs *InstancePtr,XV_HdmiTxSs_Config *CfgPtr,u32 EffectiveAddr);(5) 连接中断回调函数,使能中断控制器,以便处理中断,调用中断回调函数。

int XIntc_Connect(XIntc *InstancePtr, u8 Id, XInterruptHandler Handler,void *CallBackRef);

void XIntc_Enable(XIntc *InstancePtr,u8 Id);6.3 HDMI 1.4/2.0 TX Subsystem Interrupts

在HDMI 1.4/2.0 TX Subsystem Flow由各种中断调用回调函数来推进整个Flow,比如HPD中断后,调用回调函数去进行PHY Controller的设置; PHY Controller输出时钟稳定后,会产生Link Ready; 接着数据帧有效后,会产生STREAM_UP类型的中断等等。

以下是HDMI1.4/2.0 TX Subsystem中的各种中断源。

(1)HPD - Peripheral I/O to detect HDMI cable 5.0V signal

a.Rising edge -- 当HDMI线插入,维持超过10ms产生。

b.Falling edge -- 当HDMI线拔出,维持超过100ms产生。

c.Toggle - 当在HPD上出现一个脉冲宽度为50ms到99ms的脉冲时产生。

(2) Link Ready - 每次PHY Controller被重配置,link_clk重新生成时产生。

在HDMI TX sub-core的寄存器中有一位link status bit受link_clk状态的影响。当link_clk稳定时,该位被置1。当link_clk不稳定时,该位被清0.

a.Rising edge -- 标识link_clk稳定

b.Falling edge -- 标识link_clk不稳定

(3) Vertical Sync - 当HDMI TX sub-core的vsync输入信号有效时产生。

a.Rising edge - Vsync信号被检测到

(4) Video Bridge Unlocked - 当Subsystem的video interface类型是AXI4 Video Stream时,会集成一个AXI4-Stream to Video Out Bridge的IP在子系统中,当Video Out Bridge中的数据流unlock时,便会产生该类型中断。

(5) HDCP 1.4 Interrupt(使用HDCP1.4才能产生该中断)

(6) HDCP 1.4 Timer Interrupt(HDCP 1.4的定时器中断)

(7) HDCP 2.4 Timer Interrupt(HDCP 2.4的定时器中断)

6.4 HDMI 1.4/2.0 TX Subsystem Callback Functions

使用下面的API函数对HDMI TX Subsystem设置中断回调函数。

int XV_HdmiTxSs_SetCallback(XV_HdmiTxSs *InstancePtr,u32 HandlerType,void *CallbackFuncPtr,void *CallbackRef);在该API函数中的HandlerType已经在xv_hdmitxss.h中定义,有XV_HDMITXSS_HANDLER_CONNECT,XV_HDMITXSS_HANDLER_STREAM_UP, XV_HDMITXSS_HANDLER_STREAM_DOWN,XV_HDMITXSS_HANDLER_VS,XV_HDMITXSS_HANDLER_HDCP_AUTHENTICATE

(1) XV_HDMITXSS_HANDLER_CONNECT

该中断在每次插拔HDMI线缆时会被调用。在该回调函数中,基本操作功能如下:

a. 检测中断产生原因是HDMI线缆插入引起,还是HDMI线缆拔出引起的。

XV_HdmiTxSs *HdmiTxSsPtr = (XV_HdmiTxSs*)CallbackRef;

/*

HdmiTxSsPtr->IsStreamConnected

1 - Connected; 0 - Disconnected

*/b.当HDMI线缆连接时,使能PHY Controller中的差分输入时钟buffer;当HDMI线缆断开时,无效PHY Controller中的差分输入时钟buffer.

void XVphy_IBufDsEnable(XVphy *InstancePtr,u8 QuadId,XVphy_DirectionType Dir,u8 Enable)c.如果HDMI线缆连接了,检查HDMI Sink连接的是HDMI 2.0的线缆。

int XV_HdmiTxSs_DetectHdmi20(XV_HdmiTxSs *InstancePtr);d.当HDMI Sink连接上后,就可以通过DDC获取Sink中的EDID/E-EDID信息了,然后将其存放在本地buffer中。

int XV_HdmiTxSs_ReadEdid(XV_HdmiTxSs *InstancePtr,u8 *Buffer);(2) XV_HDMITXSS_HANDLER_STREAM_UP

该中断在每次Video PHY Controller/HDMI GT Subsystem被重配置,输出时钟稳定后会产生。

a. 如果系统中有使用到HDMI Retimer或者equalizer,根据视频流分辨率以及帧率信息,计算出相应的线速率(line rate),去配置Retimer.

b.通过调用下面的API函数,使能TX TMDS clock.

void XVphy_Clkout1OBufTdsEnable(XVphy *InstancePtr,XVphy_DirectionType Dir,u8 Enable);c. 设置HDMI 1.4/2.0 TX Subsystem中的采样速率(sampling rate)

void XV_HdmiTxSs_SetSamplingRate(XV_HdmiTxSs *InstancePtr,u8 SamplingRate);(3) XV_HDMITXSS_HANDLER_STREAM_DOWN

该中断在每次Video PHY Controller/HDMI GT Subsystem被重配置,输出时钟不稳定的时候会产生。

a. 无效使能Video PHY Controller/HDMI GT Subsystem中TX TMDS clock

void XVphy_Clkout1OBufTdsEnable(XVphy *InstancePtr,XVphy_DirectionType Dir,u8 Enable);(4) XV_HDMITXSS_HANDLER_VS

该中断在每次HDMI 1.4/2.0 TX Subsystem中的HDMI TX sub-core检测到vertical sync信号时产生。

a. 向HDMI Sink发送Aux InfoFrames

void XV_HdmiTxSs_SendAuxInfoframe(XV_HdmiTxSs *InstancePtr,void *Aux);(5)XV_HDMITXSS_HANDLER_HDCP_AUTHENTICATE

该中断在HDMI线缆连接上,HDCP 1.4或者HDCP 2.3被使能,且HDCP进入了认证状态(当HPD持续100~500ms的时间进入)时产生。

a. 使能HDCP加密

b. 向系统内发出认证已经成功完成的信号

6.5 Video PHY Controller/HDMI GT Subsystem Callback functions

对于Video PHY Controller,有给HDMI 1.4/2.0 TX Subsystem服务的中断,也有给HDMI 1.4/2.0 RX Subsystem服务的中断,这些中断句柄(interrupt handlers)已经被定义在了xvphy.h中。

给HDMI 1.4/2.0 TX Subsystem服务的中断句柄如下:XVPHY_HDMI_HANDLER_TXINIT, XVPHY_HDMI_HANDLER_TXREADY

同样的,Video PHY Controller也像HDMI 1.4/2.0 TX Subsystem一样去绑定设置中断回调函数。

void XVphy_SetHdmiCallback(XVphy *InstancePtr,XVphy_HdmiHandlerType *HandlerType,void *CallbackFunc,void *CallbackRef);(1) XVPHY_HDMI_HANDLER_TXINIT

该中断在每次Video PHY Controller/HDMI GT Subsystem 检测到HDMI TX参考时钟(Referenceclock)发生了变化时产生。

a. 为HDMI 1.4/2.0 TX Subsystem初始化参考时钟变化

void XV_HdmiTxSs_RefClockChangeInit(XV_HdmiTxSs *InstancePtr);(2) XVPHY_HDMI_HANDLER_TXREADY

该中断在每次Video PHY Controller/HDMI GT Subsystem TX reset lock完成,或者是Video PHY Controller/HDMI GT Subsystem TX alignment(这里?)完成时产生。该中断回调函数给应用软件程序,提供更新Video PHY Controller/HDMI GT Subsystem的TX相关信息。

6.5 Example Use Cases

(1) Cable Plug In

当HDMI线缆连接时,HPD中断产生。调用的中断回调函数的中断类型为XV_HDMITXSS_HANDLER_CONNECT

(2) Cable Plug out

当HDMI线缆断开时,HPD中断产生。调用的中断回调函数的中断类型为XV_HDMITXSS_HANDLER_CONNECT

(3) Send Infoframe

当Vertical Sync信号被检测到时,VS中断产生。调用的中断回调函数的中断类型为XV_HDMITXSS_HANDLER_VS

(4) Send Video Stream

a.无效Video PHY Controller/HDMI GT Subsystem为HDMI 1.4/2.0 TX Subsystem提供的TMDS clock.

/* XVphy_Clkout1OBufTdsEnable(XVphy *InstancePtr,XVphy_DirectionType Dir,u8 Enable);*/

XVphy_Clkout1OBufTdsEnable(VphyPtr,XVPHY_DIR_TX,(FALSE));b. 给HDMI 1.4/2.0 TX Subsystem设置视频流参数。在设置完成后,会返回一个对应的参考时钟值。

/*

u32 XV_HdmiTxSs_SetStream(XV_HdmiTxSs *InstancePtr,XVidC_VideoMode VideoMode,

XVidC_ColorFormat ColorFormat,XVidC_ColorDepth Bpc,XVidC_3DInfo *Info3D);

*/

TmdsClock = XV_HdmiTxSs_SetStream(HdmiTxSsPtr,VideoMode,ColorFormat,Bpc,NULL);c. 给Video PHY Controller/HDMI GT Subsystem 设置TX参考时钟(reference clock)

VphyPtr->HdmiTxRefClkHZ = TmdsClock;d. 为Video PHY Controller/HDMI GT Subsystem设置HDMI TX的参数

/*

u32 XVphy_SetHdmiTxParam(XVphy *InstancePtr,u8 QuadId,

XVphy_ChannelId ChId,XVidC_PixelsPerClock Ppc,

XVidC_ColorDepth Bpc, XVidC_ColorFormat ColorFormat);

*/

Result = XVphy_SetHdmiTxParam(VphyPtr,0,XVPHY_CHANNEL_ID_CHA,

HdmiTxSsVidStreamPtr->PixPerClk,

HdmiTxSsVidStreamPtr->ColorDepth,

HdmiTxSsVidStreamPtr->ColorFormatId);d. 配置Video PHY Controller/HDMI GT Subsystem提供Reference TMDS clocks的外部时钟生成器。

e. Video PHY Controller的HDMI TX Init中断产生--XVPHY_HDMI_HANDLER_TXINIT

f. Video PHY Controller的HDMI TX Ready中断产生--XVPHY_HDMI_HANDLER_TXREADY

g. HDMI TX Stream UP 中断产生--XV_HDMITXSS_HANDLER_STREAM_UP

(5) Enable HDMI mode

XV_HdmiTxSs_SetHdmiMode(&HdmiTxSs);

XV_HdmiTxSs_AudioMute(&HdmiTxSs,FALSE);(6) Enable DVI Mode

XV_HdmiTxSs_SetDviMode(&HdmiTxSs);

XV_HdmiTxSs_AudioMute(&HdmiTxSs,TRUE);