PCB布线及后仿真验证过程(干货满满,建议收藏)

一、布线的基本要求

布线次序考虑

1) 规则驱动布线遵循的基本步骤

- 定义禁布区,或控制区

- 若有规则约束,要求设置规则

- 试布线,评估单板是否可以布通,若不能布通,需要采用策略

- Fanout后对覆盖率检查,通常要求满足100%的覆盖率;自动Fanout不能完全覆盖时,要求手工调整达到100%覆盖,采用Fanout策略

- 分析单板自动布线的可行性,对初始阶段和收敛阶段进行判断

- 优先布关键信号线或附有规则的信号线,规则检查,要求有规则的关键信号线满足相应的约束规则

- 其次对非关键信号线走线,总体规则检查,要求非关键信号线满足普通的设计要求

- 综合使用布线策略,解决冲突

- 对布线进行后处理,以改善信号质量,利于加工

2) 规则优先:若有规则存在,则优先布置有规则要求的信号线,然后布置非关键信号线;

3) 关键信号线优先:电源、摸拟信号、高速信号、时钟信号、差分信号和同步信号等关键信号优先布线;

4) 密度优先:从单板上连接关系最复杂的器件着手布线,从单板上连线最密集的区域开始布线。

二、约束规则设置基本要求

1) 在布线之前需进行物理规则和电气规则的定义,以便在设计过程中对设计规则进行检查,使设计满足规则要求

2) 物理约束规则应综合考虑DFM、DFT、DFA,同时也要考虑印制线的电流、电压以及禁布区和属性问题

3) 电气约束规则应从器件资料和预仿真分析过程中合理提取

三、布线处理的基本要求

1) 规则驱动布线时,保证规则的合理性,使用并提供过程Do文件

2) 过孔、线宽、安全间距避免采用极限值

3) 规则驱动布线的过程中尽可能考虑ICT测试点设计

4) 管脚引线尽可能从PIN中心引出

5) 信号线与PIN间尽可能拉开距离

6) 无通孔或机械盲孔上焊盘

7) 走线到板边的距离通常情况下需≥2mm,在不能满足条件的情况下,至少保证不小于20mil

8) 表面除短的互连线和Fanout的短线外,信号线尽可能布在内层

9) 金属外壳器件下,不允许有过孔、表层走线

10) 尽量为时钟信号、高频信号、敏感信号等关键信号提供专门的布线层,并保证其最小的回路面积。采用屏蔽和加大安全间距等方法,保证信号质量

11) 电源层和地层之间的EMC环境较差,应避免布置对干扰敏感的信号线

12) 有阻抗控制要求的网络应布置在阻抗控制层上

13) 布线尽可能靠近一个平面,并避免跨分割。若必须跨分割或者无法靠近电源地平面,这些情况仅允许在低速信号线中存在

14) 高速信号线区域相应的电源平面或地平面尽可能保持完整

15) 平面层和布线层分布对称,介质厚度分布对称,过孔跨层保持对称

16) 平面层分割避免出现直角或锐角

17) 大面积敷铜时参考网络采用地网络

18) 敷铜时避免出现直角或锐角,并且上下铜皮须有过孔相连,尤其在铜皮的边缘处,边缘相邻过孔相距约200~400mils

19) 布线保持均匀,大面积无布线的区域需要敷铜,但要求不影响阻抗控制

20) 布线无DRC错误,无同名网络错误

21) 所有信号线必须倒角,倒角角度为45度,特殊情况除外

22) PCB设计完成后无未布完的网络,且PCB网表与原理图网表一致

四、布线所遵循的基本规则

1) 地线回路规则

地线回路规则图

环路最小规则,即信号线与其回路构成的环面积要尽可能小,环面积越小,对外的辐射越少,接收外界的干扰也越小。针对这一规则,在地平面分割时,要考虑到地平面与重要信号走线的分布,防止由于地平面开槽等带来的问题;在双层板设计中,在为电源留下足够空间的情况下,应该将留下的部分用参考地填充,且增加一些必要的地过空孔,将双面地信号有效连接起来,对一些关键信号尽量采用地线隔离,对一些频率较高的设计,需特别考虑其地平面信号回路问题,建议采用多层板为宜。

2) 串扰控制规则

串扰(CrossTalk)是指PCB上不同网络之间因较长的平行布线引起的相互干扰,主要是由于平行线间的分布电容和分布电感的作用。克服串扰的主要措施是:

加大平行布线的间距,遵循3W规则;

在平行线间插入接地的隔离线;

减小布线层与地平面的距离。

3) 屏蔽保护规则

屏蔽保护规则图

对应地线回路规则,实际上也是为了尽量减小信号的回路面积,多见于一些比较重要的信号,如时钟信号,同步信号;对一些特别重要,频率特别高的信号,应该考虑采用铜轴电缆屏蔽结构设计,即将所布的线上下左右用地线隔离,而且还要考虑好如何有效的让屏蔽地与实际地平面有效结合。

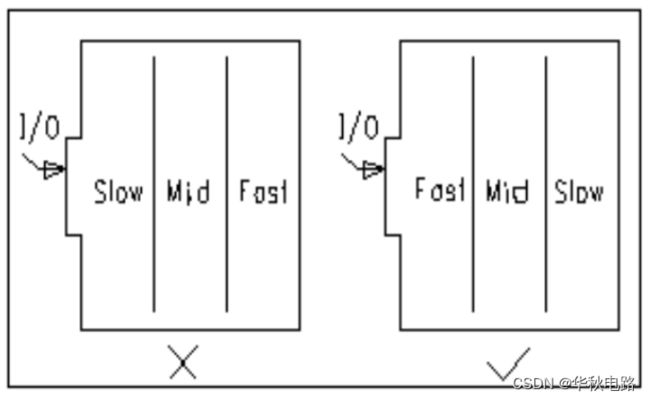

4) 走线的方向控制规则

走线的方向控制规则图

走线的方向控制规则,即相邻层的走线方向成正交结构。避免将不同的信号线在相邻层走成同一方向,以减少不必要的层间窜扰;当由于板结构限制(如某些背板)难以避免出现该情况,特别是信号速率较高时,应考虑用地平面隔离各布线层,用地信号线隔离各信号线。

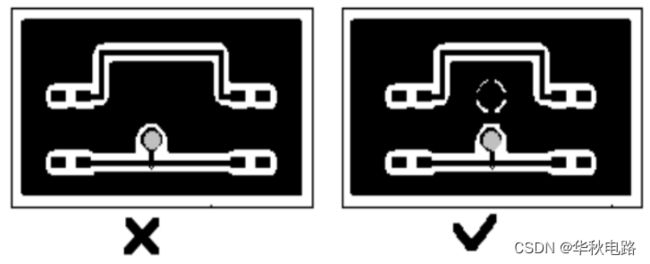

5) 走线的开环检查规则

走线的开环检查规则图

一般不允许出现一端浮空的布线(Dangling Line),主要是为了避免产生"天线效应",减少不必要的干扰辐射和接受,否则可能带来不可预知的结果。

6) 走线闭环检查规则

防止信号线在不同层间形成自环。在多层板设计中容易发生此类问题,自环将引起辐射干扰。

7) 倒角规则

倒角规则图

PCB设计中应避免产生锐角和直角,产生不必要的辐射,同时工艺性能也不好。

8) 器件去藕规则

器件去藕规则图

在印制版上增加必要的去藕电容,滤除电源上的干扰信号,使电源信号稳定。推荐电源经过滤波电容后连到电源管脚上。

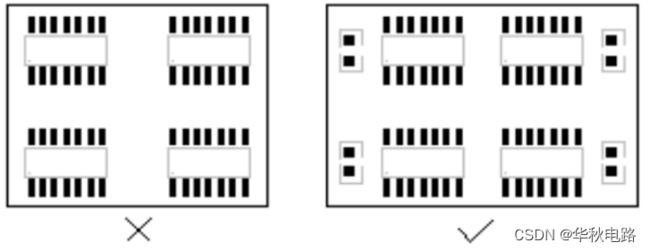

9) 器件布局分区/分层规则

器件布局分区/分层规则图

主要是为了防止不同工作频率的模块之间的互相干扰,同时尽量缩短高频部分的布线长度。通常将高频的部分布设在接口部分以减少布线长度,当然,这样的布局仍然要考虑到低频信号可能受到的干扰。同时还要考虑到高/低频部分地平面的分割问题,通常采用将二者的地分割,再在接口处单点相接。对混合电路,也有将模拟与数字电路分别布置在印制板的两面,分别使用不同的层布线,中间用地层隔离的方式。

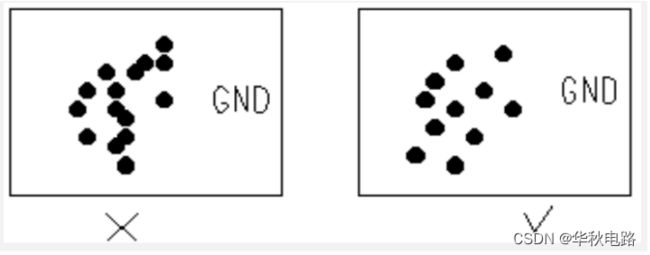

10) 孤立铜区控制规则

孤立铜区的出现,将带来一些不可预知的问题,因此将孤立铜区与别的信号相接,有助于改善信号质量,通常是将孤立铜区接地或删除。在实际的制作中,PCB厂家将一些板的空置部分增加了一些铜箔,这主要是为了方便印制板加工,同时对防止印制板翘曲也有一定的作用。

11) 电源地平面完整性规则

对于导通孔密集的区域,要注意避免孔在电源和地层的挖空区域相互连接,形成对平面层的分割,从而破坏平面层的完整性,并进而导致信号线在地层的回路面积增大。为避免破坏平面层,做Fanout时过孔间距至少保证能走一根信号线。

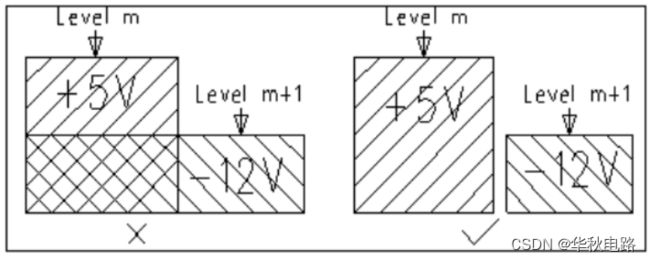

12) 电源地平面层重叠规则

不同电源层在空间上要避免重叠。主要是为了减少不同电源之间的干扰,特别是一些电压相差很大的电源之间,电源平面的重叠问题一定要设法避免,难以避免时可考虑中间隔地层。

13) 3W规则

为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持70%的电场不互相干扰,称为3W规则。如要达到98%的电场不互相干扰,可使用10W的间距。

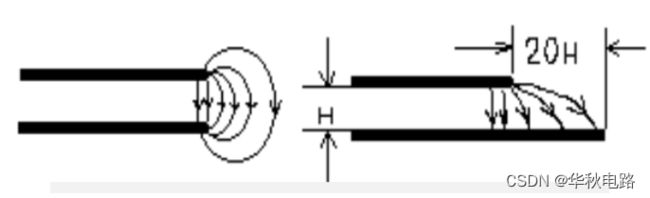

14) 20H规则

由于电源层与地层之间的电场是变化的,在板的边缘会向外辐射电磁干扰。称为边沿效应。解决的办法是将电源层内缩,使得电场只在接地层的范围内传导。以一个H(电源和地之间的介质厚度)为单位,若内缩20H则可以将70%的电场限制在接地层边沿内;内缩100H则可以将98%的电场限制在内。

总结:本篇文章很长,每个规则都配有图片案例展示,更容易看懂。有兴趣的小伙伴,可以收藏关注哦。