PCIE知识点-008:PCIE switch的结构

1、Switch基本结构

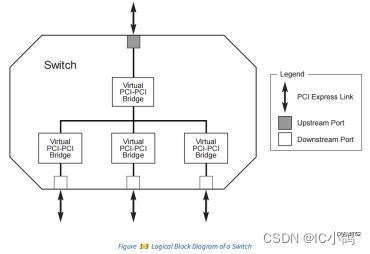

Switch结构图如图1-3所示,switch包含一个upstream port和若干个downstream port,upstream port和downstream port是通过virtual PCI-PCI bridge进行连接。

以下是PCIE 5.0原文描述:

• Switches appear to configuration software as two or more logical PCI-to-PCI Bridges.

• A Switch forwards transactions using PCI Bridge mechanisms; e.g., address-based routing except when engaged in a Multicast, as defined in Section 6.14 .

• Except as noted in this document, a Switch must forward all types of Transaction Layer Packets (TLPs) between any set of Ports.

• Locked Requests must be supported as specified in Section 6.5 . Switches are not required to support Downstream Ports as initiating Ports for Locked Requests.

• Each enabled Switch Port must comply with the Flow Control specification within this document.

• A Switch is not allowed to split a packet into smaller packets, e.g., a single packet with a 256-byte payload must not be divided into two packets of 128 bytes payload each.

• Arbitration between Ingress Ports (inbound Link) of a Switch may be implemented using round robin or weighted round robin when contention occurs on the same Virtual Channel. This is described in more detail later within the specification.

• Endpoints (represented by Type 00h Configuration Space headers) must not appear to configuration software on the Switch’s internal bus as peers of the virtual PCI-to-PCI Bridges representing the Switch Downstream Ports.

2、Switch中的downstream port数量与device number

以不支持ARI结构的switch作为案例讲解:

2.1 Single-function 类型的switch

常见设计中,Downstream Ports和upstream port都是Single-function ,即单个function。其中所有(数量不大于32)Downstream Ports公用一个总线号,如图1-3所示结果。不同的downstream port仅仅device number(8-bit)不一样,从0~31。

2.1 Multifunction 类型的switch

当switch中downstream port数量超过32个时,Single-function 类型的switch的旧无法满足需求了。此时downstream port或者upstream port 都需要实现为Multifunction 的设备。

如图21-10 所示,仅仅downstream port实现为Multifunction,所有的downstream port依旧公用一组总线号,,每个function都拥有一个type1 类型的配置空间。

如图21-11 所示,upstream port和downstream port均实现为Multifunction,downstream port分别公用两组总线。

但是非non-ARI 的upstream port只能使用单个device(见PCIE 5.0协议 P680)

3、参考文献

MindShare_PCI_Express_System_Architecture P819 图21-10 和图21-11

PCI Express Base Specification Revision 5.0, Version 1.0 7.3.1 Device Number P680

With non-ARI Devices, PCI Express components are restricted to implementing a single Device Number on their primary interface (Upstream Port), but are permitted to implement up to eight independent Functions within that Device Number. Each internal Function is selected based on decoded address information that is provided as part of the address portion of Configuration Request packets.