硬件设计2---什么是电阻?

时间:2018.1.24 作者:Tom 工作:HWE 说明:如需转载,请注明出处。- 什么是电阻?

百度百科中介绍"电阻(Resistance,通常用"R"表示),是一个物理量,在物理学中表示导体对电流阻碍作用的大小。导体的电阻越大,表示导体对电流的阻碍作用越大。不同的导体,电阻一般不同,电阻是导体本身的一种特性。电阻将会导致电子流通量的变化,电阻越小,电子流通量越大,反之亦然。"

电阻对于硬件工程师来说是一个非常重要的元件,对电阻的熟练应用也是属于重要的基本功之一。说实话不是单独搜了下百度百科,我都忘了电阻的定义了,但是我首先想到的用水管举例,水管的开口大小比作电阻,水流比作电流,水管开口越小(电阻越大),水流越小(电流越小)。水管的举例在三极管章节会有一个经典的举例,后面再看!

如果说芯片是电路的骨架,那么电阻就是芯片之间起连接作用的关节。电阻的阻值、布放位置等,对设计的成功起着至关重要的作用!!

抛开一些简单理论,下面主要讨论一些实用的东西。

- 贴片电阻的分类及封装

电阻只是统称,一般我们在研发时候会直接具体到数值及封装,比如我需要33Ω 0402的电阻。

电阻一般能见到的不是贴片式的就是插针式,你如果非要说滑动变阻器,那我也无法反驳。这里我们主要讨论一些贴片电阻,因为在研发过程中是最常见的。

贴片电阻:是将金属粉和玻璃铀粉混合,采用丝网印刷发印在基板上制成的电阻器。这个看起来像画PCB一样。

贴片电阻的特点:体积小、重量轻、电性能稳定、可靠性高、装配成本低、机械强度高、高频特性优越、适用回流焊与波峰焊(回流焊是因为气体在焊机内循环流动产生高温达到焊接目的。波峰焊是让插件板的焊接面直接与高温液态锡接触达到焊接目的。这两个焊你必须要知道的!!)。

题外话:现在生产电阻的工艺越来越成熟,单个电阻价格很低,但这个是走量的,目前生产电阻电容的厂家确实很赚钱的,因为消耗比较大,一般公司采购量都是十万级或者百万级。

贴片电阻分为常规类系列厚膜电阻、高精度高稳定性贴片电阻、常规系列薄膜贴片电阻等等,这个分类说多了也没什么意思,我们需要知道我们一般情况下用的都是薄膜贴片电阻,除非特殊情况下才会使用其他的。

电阻的封装才是我们需要关注的。为什么这么说呢?有时候别人会问0204封装的电阻长宽多大?有时候你自己都会好奇,0402封装的电阻功率多大,通流量是多少?封装的大小关系到PCB布局布线,通流量大小关系到我们是设计!!

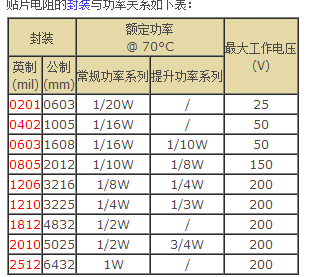

需要明确的是,我们所说0402,0603封装都是英制的,单位是mil,1mil/40=0.025mm,mil除以40可以转换成mm单位,这个必须要记住。在网上搜索了一下,看下封装与尺寸的关系:

一般情况下,我们使用最大到1206封装,再大的封装使用的就少了,其实随着产品集成化程度越来越高,设计时候倾向选择小电阻,比如0402封装的。需要注意的是尽量不要使用0201封装的电阻,千万不要自寻死路。上述图片的下面三行字很重要,可以直观计算大致的长宽!!!(封装除以4!这个和上述单位转换不同,这个可以当做是经验公式。)

封装与功率关系如下表所示:

计算公式大家必须要熟练应用计算通流,P=UI = U^2/R。这在后面应用中会再次讲到。

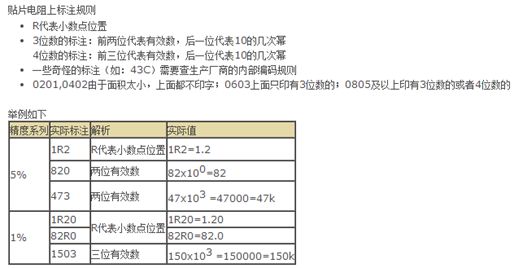

对于电阻的标注规则,这里不再细说,说实话不用万用表测量,我就是看出来了我也不敢用(手动尴尬)。下面贴出来,或许以后会有用:

-

电阻的应用

直接进入主题:

-

应用一:分压

有耐心的可以看下知乎中提问的"电阻为什么会分压?",哈哈。(https://www.zhihu.com/question/64669081/answer/223553370)

这个比较经典的举例就是DC/DC或者LDO电路。比如MP2315数据手册中推荐的电路如下图所示:

R1和R2是分压电阻,而且对于所有的DC/DC和LDO输出反馈端的分压电阻必须是精度1%的。(科普:在电源芯片输出管脚上一般选择分压电阻的精度很高,电阻的精度直接决定了输出电压的精度,如5%的电阻输出电压波动范围为10%,1%精度的电阻输出电压波动范围达到2%,因此选择精度高的;这个可以计算一下大致差不多的误差。)这个参考电压与输出的关系在DC/DC或者LDO章节再详细讨论。

在这张图中还有一个分压电阻应用就是R6和R7的应用。图中R7是空贴的,对于EN管脚,以前不理解为什么标注是空贴,非常需要注意一下,因为我在这个地方吃过亏。因为EN必须大于1.6V,在电路移植的时候,一定要注意输入电压分压之后与EN阈值的关系以便及时调整R7电阻,切记!!!

电阻分压在芯片管脚做逻辑阈值或者上下电时应用还是比较多的。其他例子也类似,关键点在于一定要搞清管脚的阈值(门限电压范围),这种错误属于低级错误,在设计时一定要多确认几遍。

- 应用二:限流/分流

需要说明的是限流和分流是不同的概念,说是不同,但其实应用原理差不多,都是U/R的灵活应用。但不管限流还是分流目前我碰到的情况也是不多的。先给出两种吧,等以后遇到了,再补充。

左图的原理比较简单就不说了。右图中R1称为分流电阻,电流中的一部分流过电阻R1,三极管流过的电流有所减少,而输出端的总电流并没有减小,R1起到保护三极管的作用。

其实限流的目的应用最广泛的就是保护器件的工作安全。暂时讲这么多,以后遇到再补充。

- 应用三:阻抗匹配

阻抗匹配:严格来讲,当高速电路中,信号再传输介质上的传输时间大于信号上升沿或者下降沿的1/4时,该传输介质就需要阻抗匹配。

-

源端阻抗:一般传输线的阻抗为50Ω左右,而TTL电路输出电阻大概为13Ω左右,在源端串联一个33Ω的电阻,13+33=46Ω大致和50Ω相当,这样就可以抑制从终端反射回来的信号再次反射。

需要说明的是,匹配电阻不一定都是33欧,从几Ω到几十Ω都有,具体试情况而定。而确定匹配电阻具体数字是并不是理论给出的,最让人信服也是最能说的通的就是根据实际情况就行尝试和整改的。但不管怎样一般都加载驱动器端。接收端也可以做匹配,例如采用电阻并联,但在数字系统一般比较少用,因为比较麻烦,而且很多时候是一发多收,如DDR的地址总线,不如源端匹配易做。在网上看到了33欧姆电阻在电路中常见的作用,贴在下面:

-

终端阻抗:若信号接收端的输入阻抗很大,可以并接一个51Ω的电阻,电阻另一端接参考地,以抑制信号终端反射。信号接收端接串阻,那只能是终端输入阻抗小于50Ω。但IC设计时,考虑到接收能量,不会将接收端的输入阻抗设计的小。这也是为什么驱动器端加串阻,而接收端一般不加串阻的原因,终端开路的情况下反射系数为1。

但有时终端会加上匹配电阻,比如:LVDS的终端匹配电阻100欧姆。DDR的差分时钟终端匹配电阻100欧姆等等

-

阻抗匹配电阻在接口防护范围还有一个重要作用就是防止ESD。

比如USB等

- 应用四:全带宽滤波(吸收毛刺)

在一些芯片的电源管脚,采用LC滤波,有时会在L之后串联一个几欧姆的电阻,电阻起到全频段滤波的作用,还有一个作用就是降低电路的品质因数Q,Q定义为回路发生谐振时,储存能量与一周期内消耗能量之比。Q=(LC)1/2/R。

1)在储能电路中,Q值越大意味着损耗小,虑除其他频带信号的能力越强,希望Q越大越好;

2)在电源或信号线路中,Q越大,通频带内特性曲线越陡峭,越容易引发振铃,信号越容易失真。希望Q越小越好;

其实在实际应用中,利用电阻进行全带宽滤波的应用非常多。其次串接电阻也可解决针对信号的上升沿下降沿产生的过冲、抖动等,比如音频的I2S信号中,串接33欧姆出现上冲,更换为50欧姆明显上冲小了很多!!

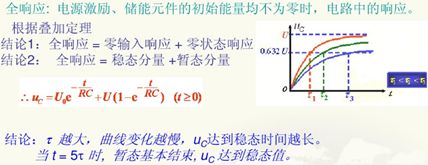

- 应用六:RC电路

RC电路的是电阻和电容一起使用的。

直接给出RC电路的全响应计算公式:

-

应用七:上下拉

上下拉在电路设计中是一个非常重要的作用,一般来说基本上所有中等及以上电路中绝对会有上下拉电阻的应用!!!

(参考:http://www.cnblogs.com/emouse/archive/2012/03/19/2406888.html http://www.360doc.com/content/17/0514/22/42387867_653878627.shtml)

>>>首先需要明白的是:什么是上下拉???

在嵌入式接口的相关应用中经常提到上拉电阻与下拉电阻,顾名思义,上拉电阻就是把端口连接到电源的电阻,下拉电阻就是把端口连接到地的电阻。虽然电路形式非常简单,然而上拉电阻与下拉电阻在很多场合却扮演着非常重要的作用。

>>>那问题来了,为什么上拉就能产生高电平,下拉就能产生低电平呢???

一般情况下,我们所说的上下拉主要应用在芯片端口,像三极管、MOS管对应着芯片接口的TTL电平与CMOS电平。

我们来看下一个简单的GPIO结构图:

我们知道GPIO的输出一般有两种:推挽输出和开漏输出(具体在下一章节讲述),推挽输出可配置输出为高或者低,开漏输出可配置为低或者高阻。而输入根据上图可配置高、低或者不定状态(不定状态实际上是存在的)。除了开漏输出,其他配置我们可以将GPIO等效为下图:

一般来说GPIO的等效为弱上下拉,有时你在数据手册中会告诉你比如100KΩ。上图可以解释上拉可以将拉高电平。通过红色电阻将上拉电阻接入,此时10K电阻与1K并联,小于1K,而下面的电阻是10K,1K与10K串联,很显然端口输出是高电平!

>>简单的说,上拉电阻的主要作用在于提高输出信号的驱动能力、确定输入信号的电平(防止干扰)等,具体的表现为:

-

当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般为3.5V), 这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值。

-

OC门电路必须加上拉电阻,以提高输出的高电平值。

-

为加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻。

-

在COMS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗,提供泄荷通路。

-

芯片的管脚加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限增强抗干扰能力。

-

提高总线的抗电磁干扰能力。管脚悬空就比较容易接受外界的电磁干扰。

-

长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。

>>>上拉电阻阻值的选择原则包括:

1)从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。

2)从确保足够的驱动电流考虑应当足够小;电阻小,电流大。

3)对于高速电路,过大的上拉电阻可能边沿变平缓。

综合考虑以上三点,通常在1K到10K之间选取。对下拉电阻也有类似道理。

上拉电阻实际上是集电极输出的负载电阻。下拉电阻同理。一般来说上下拉在信号接收端配置。

- 0欧姆电阻的11个作用

最后需要说一下0欧姆电阻的作用,不管是参考电路,还是设计电路,你会经常看到0Ω电阻的,那么为什么要设计这么一个电阻呢?

零欧姆电阻又称为跨接电阻器,是一种特殊用途的电阻,0欧姆电阻的并非真正的阻值为零(那是超导体干的事情),正因为有阻值,也就和常规贴片电阻一样有误差精度这个指标。

1)留个后手。万一设计疏忽,可以跳线。不然整板报废岂不尴尬!!

2)用于选择功能模块电路。如果某段线路不用,直接不贴该电阻即可(不影响外观)

3)可调的匹配电阻。在匹配电路参数不确定的时候,以0欧姆代替,实际调试的时候,确定参数,再以具体数值的元件代替。

4)功耗测量。想测某部分电路的耗电流的时候,可以去掉0ohm电阻,接上电流表,这样方便测耗电流。

5)在高频信号下,充当电感或电容。(与外部电路特性有关)电感用,主要是解决EMC问题。如地与地,电源和IC Pin间

6)单点接地(指保护接地、工作接地、直流接地在设备上相互分开,各自成为独立系统。)

7)拟地和数字地单点接地。把数模地分开,只是工程师为了解决干扰的一种手段。用0欧姆电阻的方便之处就是它很容易拆卸,拆卸下来可以换其他的器件代替以观察最终的效果进行对比,而导线不能拆卸。

网上搜了一堆对不同地搭接的解释,说的都有道理:

只要是地,最终都要接到一起,然后入大地。如果不接在一起就是"浮地",存在压差,容易积累电荷,造成静电。地是参考0电位,所有电压都是参考地得出的,地的标准要一致,故各种地应短接在一起。人们认为大地能够吸收所有电荷,始终维持稳定,是最终的地参考点。虽然有些板子没有接大地,但发电厂是接大地的,板子上的电源最终还是会返回发电厂入地。如果把模拟地和数字地大面积直接相连,会导致互相干扰。数字地会有高频地噪声,地隔离隔离的是高频噪声,同时保证地电平。连接应该用若干0欧姆电阻:不短接又不妥,理由如上有四种方法解决此问题:

(1)用磁珠连接;磁珠的等效电路相当于带阻限波器,只对某个频点的噪声有显著抑制作用,使用时需要预先估计噪点频率,以便选用适当型号。对于频率不确定或无法预知的情况,磁珠不合。低频接近0欧电阻,高频则会出现阻抗。

(2)用电容连接;电容隔直通交,造成浮地。

(3)用电感连接;电感体积大,杂散参数多,不稳定。据说会有危险,可能打坏低压器件。不推荐。

(4)两个肖特基二极管背对背连接,保护电源插拔等造成的地平面见直流电压。

(5)用0欧姆电阻连接。0欧电阻相当于很窄的电流通路,能够有效地限制环路电流,使噪声得到抑制。电阻在所有频带上都有衰减作用(0欧电阻也有阻抗),这点比磁珠强。

其实EMC很关键一点就是环流路径最小化,如果进行地分割,就要非常注意,一旦信号线跨越地分割线,环流路径必然增大,EMC性能变差。而采用统一地的电路板,事先必须对布局做足考虑,对电路模块进行物理分区(不分割),保证模块都有自己的回路,就不会影响其他模块,同时因为地没有分割,保证了地的完整性。直接用0欧电阻的做法比较常见但并不规范。模拟部分对噪声不敏感可以这么干。

8)熔丝作用。

9)跨接时用于电流回路。当分割电地平面后,造成信号最短回流路径断裂,此时,信号回路不得不绕道,形成很大的环路面积,电场和磁场的影响就变强了,容易干扰/被干扰。在分割区上跨接0欧电阻,可以提供较短的回流路径,减小干扰。

10)配置电路。一般,产品上不要出现跳线和拨码开关。有时用户会乱动设置,易引起误会,为了减少维护费用,应用0欧电阻代替跳线等焊或者空贴在板子上。但在高频时空置跳线在高频时相当于天线,用贴片电阻效果好。

11)测试电路使用。比如电路中电压输入端,串接一个磁珠,如果不需要磁珠,或者磁珠不好怎么办?用相同封装的0欧姆(或者其他阻值)代替,封装一样,贴片可兼容。还有就是不同尺寸0欧电阻允许通过电流不同,一般0603的1A,0805的2A,所以不同电流会选用不同尺寸的还有就是为磁珠、电感等预留位置时,得根据磁珠、电感的大小还做封装,所以0603、0805等不同尺寸的都有了。

12)调试电路使用。很简单,说一个例子:假如你的产品比较复杂或者你的电源开关比较复杂,驱动调试或者自检时候太麻烦装整机,或者开关老是失效影响调试开发进度怎么办呢?预留一个0欧姆对地电阻,可以完全脱离开关结构的困扰,比如:

这种方法在电源模块电路中经常遇到。虽然预留0欧姆空贴并不是最好的方法,可以更改为跳线帽或者拨码开关,但这种做法的成本是最低的,占用空间也小,缺点就是要手动焊接。

- 其他的一点说明:

-

对于电阻的应用有四个关注点:电阻的阻值、电阻的封装、电阻的额定功率、电阻的精度;

-

对于阻值,可根据电路的要求计算得到,有时候计算得到的阻值属于不经常用的阻值,从节省成本的角度考虑,建议采用常用阻值的电阻通过串联或者并联的方式构成该电阻,因不常用的器件价格越高;

-

在功耗高的路径上,如果串联了电阻,应针对额定功率的选型,需要注意至少降额20%使用,如电阻的额定电流和实际工作电流比较接近会有风险,比如USB串阻,以前使用共模扼流圈,阻抗比较低,经常挂掉,现在使用10欧姆串阻,不会挂掉;

-

电阻用于设定器件的工作参数时,应选择高精度电阻;

-

磁珠的电阻一般只有零点几欧姆。