软考笔记——1.2计算机体系结构分类、指令流水线、存储系统、系统可靠性分析

一、计算机体系结构分类

Flynn分类法:

| 体系结构类型 | 结构 | 关键特性 | 代表 |

| 单指令流单数据流SISD | 控制部分:1个 处理器:1个 主存模块:1个 |

单处理器系统 | |

| 单指令流多数据流SIMD | 控制部分:1个 处理器:多个 主存模块:多个 |

各处理器以异步的形式执行同一条指令 | 并行处理机 阵列处理机 超级向量处理机 |

| 多指令流单数据流MISD | 控制部分:多个 处理器:1各 主存模块:多个 |

被证明不可能,至少是不实际 | 目前没有,有文献称流水线计算机为此类 |

| 多指令流多数据流MIMD | 控制部分:多个 处理器:多个 主存模块:多个 |

能够实现作业、任务、指令等各级全面并行 | 多处理机系统 多计算机 |

二、计算机指令

计算机指令的组成:一条指令由操作码和操作数两部分组成,操作码决定完成操作,操作数指参加运算的数据及其所在的单元地址

在计算机中,操作要求和操作数地址都由二进制数码表示,分别称作操作码和地址码,整条指令以二进制编码的形式存放在存储器中

计算指令执行过程:取指令——分析指令——执行指令三个步骤,首先将程序计数器PC中的指令地址取出,送入地址总线,CPU依据指令地址去内存中取出指令内容存入寄存器IR;而后由指令译码器进行分析,分析指令操作码;最后执行指令,取出指令执行所需的源操作数

指令寻址方式:

- 顺序寻址方式

- 跳跃寻址方式

指令操作数的寻址方式:

- 立即寻址方式

- 直接寻址方式

- 间接寻址方式

- 寄存器寻址方式:操作数在寄存器中的寻址方式

三、指令(重点)

1、指令系统

CISC是复杂指令系统,兼容性强,指令繁多,长度可变,由微程序实现

RISC是精简指令系统,指令少,使用频率接近,主要依靠硬件实现(通用寄存器、硬布线逻辑控制)

具体区别如下:

| 指令系统类型 | 指令 | 寻址方式 | 实现方式 | 其它 |

| CISC(复杂) | 数量多,使用频率差别大,可变长格式 | 支持多种 | 微程序控制技术(微码) | 研制周期长 |

| RISC(精简) | 数量少,使用频率接近,定长格式,大部分为单周期指令,操作寄存器,只有Load/Store操作内存 | 支持方式少 | 增加了通用寄存器;硬布线逻辑控制为主;适合采用流水线 | 优化编译,有效支持高级语言 |

2、指令流水线

指令流水线原理:将指令分成不同段,每段由不同的部分去处理,因此可以产生叠加的效果,所有的部件去处理指令的不同段

流水线相关计算:

- 流水线周期:指令分成不同执行段,其中执行时间最长的段为流水线周期

- 流水线执行时间:1跳指令总执行时间 + (总指令条数-1)* 流水线周期

- 流水线吞吐率:总指令条数/流水线执行时间

- 流水线加速比:不使用流水线总执行时间/使用流水线总执行时间

超标量流水线技术:常规流水线式度为1的,即每个流水线阶段只执行一个部分,当度大于1时,就是超标量技术,当度为3时,相当于3条流水线并行执行,即取指、分析、执行每个阶段都同时处理3条指令,因此,当题目提到度的概念时,计算时需要将:指令条数=指令条数/度。然后再套流水线执行时间的公式

【试题1】流水线的吞吐率是指流水线在单位时间里完成的任务数或输出的结果数。设某流水线有5段,有1段的时间为2ns,另外4段的每段时间为1ns,利用此流水线完成100个任务的吞吐率约为( 490*10^6 )个/s。

解答:100/[(2+4)+(100-1)x2]=100/204=490ns

1s=10^9ns

490ns=490*10^6

【试题2】流水线技术是通过并行硬件来提高系统性能的常用方法。对于一个k段流水线,假设器各段的执行时间均相等(设为t),输入到流水线中的任务是连续的理想情况下,完成n个连续任务需要的总时间为( (k+n-1)t )。若某流水线浮点加法运算器分为5段,所需要的时间分别为6ns、7ns、8ns、6ns和9ns,则其最大加速比为( 4 )

解答:完成n个连续任务需要的总时间:kt+(n-1)t = (k+n-1)t

完成n个连续任务的最大加速比为:(6+7+8+9+6)n/(6+7+8+6+9)+(n-1)/9 = 36n/(9n+27) = 36/9 = 4

四、存储系统

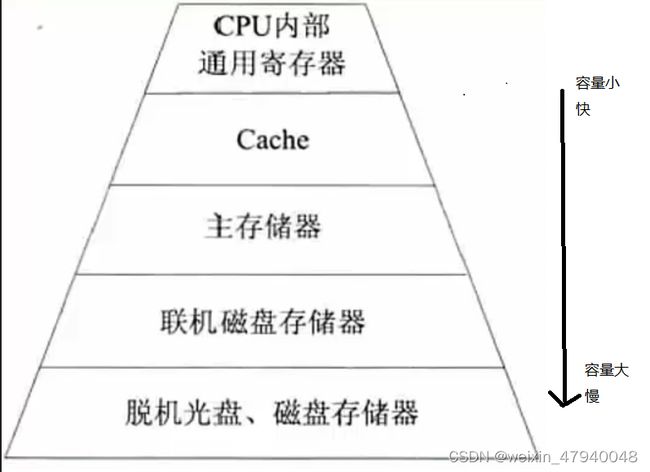

计算机存储系统的层次结构

计算机采用分级存储体系的主要目的是为了解决存储容量、成本和速度之间的矛盾问题

两级存储:Cache-主存、主存-辅存(虚拟存储体系)

局部性原理:总的来说,在CPU运行时,所访问的数据会趋于一个较小的局部空间地址内,包括下面两个方面:

- 时间局部性原理:如果一个数据项被访问,那么在近期它很可能会被再次访问,即在相邻的时间里会访问同一个数据项

- 空间局部性原理:在最近的将来会用到的数据的地址和现在正在访问的数据的地址很可能是相近的,即相邻的空间地址会被连续访问。

高速缓存Cache:

高速缓存cache用来存储当前最活跃的程序和数据,直接与CPU交互,位于CPU和主存之间,容量小,速度为内存的5-10倍,由半导体材料构成。其内容是主存内存的副本拷贝,对于程序员来说是透明的。

Cache由控制部分和存储器组成,存储器存储数据,控制部分判断CPU要访问的数据是否在Cache中,在则命中,不再则依据一定的算法在主存中替换

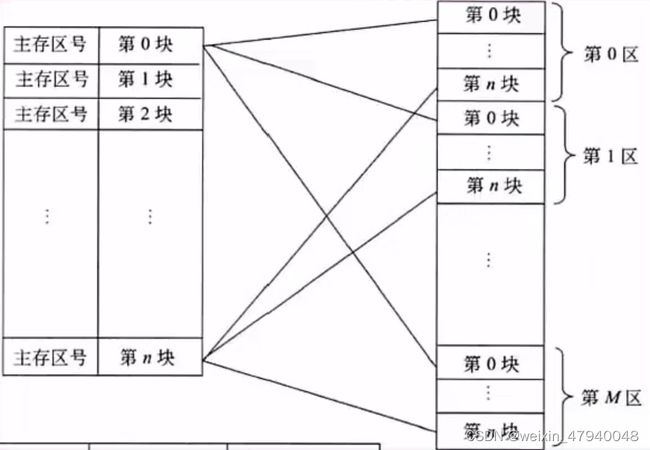

地址映射:在CPU工作时,送出的是主存单元的地址,而应从Cache存储器中读/写信息。这就需要将主存地址转化为Cache存储器地址,这种地址的转换称为地址映像,由硬件自动完成映射,分为下列三种方法:

1.直接映像:将cache存储器等分成块,主存也等分为块并编号。主存中的块与cache中的块对应关系是固定的,也就是二者块号相同才能命中。地址变换简单但不灵活,容易造成资源浪费。(如图所示)

2.全相联映像:同样都等分成块并编号。主存中任意一块都与cache中任意一块对应。因此可以随意调入cache任意位置,但地址变换复杂,速度较慢。因为主存可以随意调入cache任意块,只有当cache满了才会发生块冲突,是最不容易发生块冲突的映像方式。(如图所示)

3.组相连映像:前面两种方式的结合,将cache存储器先分块再分组,主存也同样先分块再分组,组间采用直接映像,即主存中组号与cache中组号相同的组才能命中,但是组内全相联映像,也就是组号相同的两个组内的所有块可以任意调换

按照Cache地址映像的块冲突,从高到低排列的是:直接映像-组相联映像-全相联映像

Cache命中率:当CPU所访问的数据再Cache中时,称为命中,直接从Cache中读取数据,否则没有命中,需要从主存中读取所需的数据。

【试题】使用Cache改善系统性能的依据是程序的局部性原理。程序大部分指令是( 顺序存储、顺序执行 )的。设某计算机主存的读/写时间为100ns,有一个指令和数据和一的Cache,已知该Cache的读/写时间为10ns,取指令的命中率为98%,取数的命中率为95%。在执行某类程序时,约有1/5指令需要额外存/取一个操作数。假设指令流水线在任何时候都不阻塞,则设置Cache后,每条指令的平均读取时间约为( 14.7 )ns.

解析:(100*2%+10*98%)+(100*5%+10*95%)*20%=14.7

主存编址:

1KB = 1024B

1kB=1000B

1B = 8bit(一个字节等于8位)

内存单元个数 = 末地址 - 首地址 + 1

【例题】地址编号从80000H到BFFFFH且按字节编址的内容存量为( 256 )KB,若用16K*4bit的存储器芯片构成该内存,共需( 32 )片

解析:首先计算出地址段包含的存储空间数,为BFFFFH-80000H+1=40000H,按字节编制,即一个存储空间占一个字节,共40000H个字节,转换为十进制即256KB;该存储芯片总容量为16K*0.5B=8KB,因此共需256/8=32片该芯片才能够存储。

五、总线结构

从广义上讲,任何连接两个以上电子元器件的导线都可以称为总线,通常分为以下三类:

- 内部总线:内部芯片级别的总线,芯片与处理器之间通信的总线

- 系统总线:时板级总线,用于计算机内各部分之间的连接,具体分为数据总线(并行数据传输位数)、地址总线(系统可管理的内存空间的大小)、控制总线(传送控制命令)。代表的有ISA总线、EISA总线、PCI总线

- 外部总线:设备一级的总线,微机和外部设备的总线。代表的有RS232(串行总线)、SCSI(并行总线)、USB(通用总线,即插即用,支持热插拨)

六、 系统可靠性分析

平均无故障时间MTTF=1/失效率

平均故障修复时间MTTR=1/修复率

平均故障间隔时间MTBF=MTTF+MTTR

系统可用性=MTTF/(MTTF+MTTR)*100%

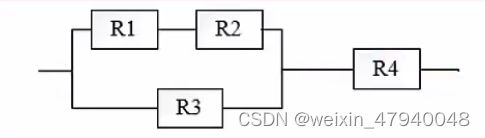

无论什么系统,都是由多个设备组成的,协同工作,而这多个设备的组合方式可以时串联、并联,也可以是混合模式,假设每个设备的可靠性为R1, R2......Rn,则不同系统的可靠性R的计算公式如下:

- 串联系统,一个设备不可靠,整个系统崩溃:R=R1 x R2 x...xRn

- 并联系统,所有设备都不可靠,整个系统才崩溃:1-(1-R1) x (1-R2) x...x (1-Rn)

- 混合系统,划分串联、并联:R x (1-(1-R)^3) x (1-(1-R)^2)

【例题】某计算机系统的可靠性结构如下所示,若所构成系统的每个部件的可靠度分别为R1、R2、R3和R4,则该系统的可靠度为( (1-(1-R1R1)(1-R3))R4 )