Verilog语言菜鸟教程知识关键点记录

Verilog语言菜鸟教程知识关键点记录

1.两类数据类型:线网数据类型与寄存器数据类型,线网表示物理元件之间的连线,寄存器表示抽象的数据存储元件。

2.Verilog 作为硬件描述语言,主要用来生成专用集成电路(ASIC)。专用集成电路,就是具有专门用途和特殊功能的独立集成电路器件。

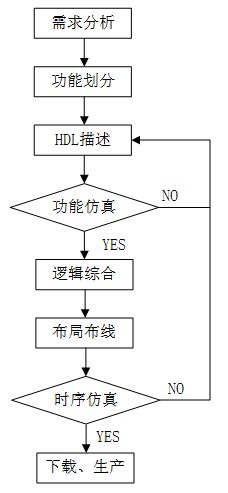

3.Verilog 的设计多采用自上而下的设计方法(top-down)。即先定义顶层模块功能,进而分析要构成顶层模块的必要子模块;然后进一步对各个模块进行分解、设计,直到达到无法进一步分解的底层功能块。

4.设计流程

5.Verilog 是区分大小写的。每个语句分号为结束符。空白符在编译阶段可忽略。

6.用 // 进行单行注释:用 /* 与 */ 进行跨行注释:

7.Verilog HDL 有下列四种基本的值来表示硬件电路中的电平逻辑:

0:逻辑 0 或 “假”

1:逻辑 1 或 “真”

x 或 X:未知

z 或 Z:z 意味着信号处于高阻,常见于信号没有驱动时的逻辑结果。逻辑值和上下拉的状态有关系。上拉则逻辑值为 1,下拉则为 0 。

8.数字声明时,合法的基数格式有 4 中,包括:(难点)

十进制('d 或 'D),

十六进制('h 或 'H),

二进制('b 或 'B),

八进制('o 或 'O)。

数值可指明位宽,也可不指明位宽。

一般直接写数字时,默认为十进制表示,下划线 _ 可以增强数的可读性。

9.字符串是由双引号包起来的字符队列。字符串不能多行书写,即字符串中不能包含回车符。Verilog 将字符串当做一系列的单字节 ASCII 字符队列。例如,为存储字符串 “www.runoob.com”, 需要 14*8byte 的存储单元。

10.wire 类型表示硬件单元之间的物理连线,如果没有驱动元件连接到 wire 型变量,缺省值一般为"Z"。

wire interrupt ;

wire flag1, flag2 ;

wire gnd = 1’b0 ;

11.寄存器(reg)用来表示存储单元,他会保持原有的值,直到被改写。

reg clk_temp;

reg flag1, flag2 ;

12.当位宽大于 1 时,wire 或 reg 即可声明为向量的形式。

reg [3:0] counter ; //声明4bit位宽的寄存器counter

wire [32-1:0] gpio_data; //声明32bit位宽的线型变量gpio_data

wire [8:2] addr ; //声明7bit位宽的线型变量addr,位宽范围为8:2

reg [0:31] data ; //声明32bit位宽的寄存器变量data, 最高有效位为0

13.对于上面的向量,我们可以指定某一位或若干相邻位,作为其他逻辑使用。例如:

wire [9:0] data_low = data[0:9] ;

addr_temp[3:2] = addr[8:7] + 1’b1 ;

14.Verillog 还支持指定bit位后固定位宽的向量域选择访问。

[bit+: width] : 从起始位bit开始递增,位宽为 width。

[bit-: width] : 从起始位bit开始递减,位宽为 width。

//下面 2 种赋值是等效的

A = data1[31-: 8] ;

A = data1[31:24] ;

//下面 2 种赋值是等效的

B = data1[0+ : 8] ;

B = data1[7:0] ;

15.整数,实数,时间等数据类型实际也属于寄存器类型。

integer

real

time:宽度一般为 64 bit,通过调用系统函数 $time 获取当前仿真时间

16.在 Verilog 中允许 reg, wire, integer, time, real 及其向量类型的数组(多维也可)

integer flag [7:0] ; //8个整数组成的数组

reg [3:0] counter [3:0] ; //由4个4bit计数器组成的数组

wire [7:0] addr_bus [3:0] ; //由4个8bit wire型变量组成的数组

wire data_bit[7:0][5:0] ; //声明1bit wire型变量的二维数组

reg [31:0] data_4d[11:0][3:0][3:0][255:0] ; //声明4维的32bit数据变量数组

17.存储器变量就是一种寄存器数组,可用来描述 RAM 或 ROM 的行为。

reg membit[0:255] ; //256bit的1bit存储器

18.字符串保存在 reg 类型的变量中,每个字符占用一个字节(8bit)。因此寄存器变量的宽度应该足够大,以保证不会溢出。

19.Verilog 中提供了大约 9 种操作符,分别是算术、关系、等价、逻辑、按位、归约、移位、拼接、条件操作符。

20.以反引号 ` 开始的某些标识符是 Verilog 系统编译指令

define,undef

ifdef,ifndef,elsif,else,endifinclude

`timescale

21.assign 为连续赋值语句关键词,任何已经声明变量的连续赋值语句都是以 assign 开头

wire Cout, A, B ;

assign Cout = A & B ; //实现计算A与B的功能

22.Verilog 时延

连续赋值时延一般可分为普通赋值时延、隐式时延、声明时延。

//普通时延,A&B计算结果延时10个时间单位赋值给Z

wire Z, A, B ;

assign #10 Z = A & B ;

//隐式时延,声明一个wire型变量时对其进行包含一定时延的连续赋值。

wire A, B;

wire #10 Z = A & B;

//声明时延,声明一个wire型变量是指定一个时延。因此对该变量所有的连续赋值都会被推迟到指定的时间。除非门级建模中,一般不推荐使用此类方法建模。

wire A, B;

wire #10 Z ;

assign Z =A & B

23.Verilog 过程结构——initial, always

initial 语句从 0 时刻开始执行,只执行一次,多个 initial 块之间是相互独立的。

与 initial 语句相反,always 语句是重复执行的。

24.Verilog 过程赋值

阻塞赋值属于顺序执行,即下一条语句执行前,当前语句一定会执行完毕。

阻塞赋值语句使用等号"="作为赋值符。

非阻塞赋值属于并行执行,即下一条语句的执行和当前语句的执行是同时进行的,它不会阻塞位于同一个语句块中后面语句的执行。

非阻塞赋值语句使用小于等号"<="作为赋值符。

25.Verilog 时序控制

时延控制,事件触发,边沿触发,电平触发

26.Verilog 语句块

顺序块,并行块,嵌套块,命名块,disable

顺序块用关键字 begin 和 end 来表示。

并行块有关键字 fork 和 join 来表示。

嵌套块:顺序块和并行块还可以嵌套使用。

命名块:我们可以给块语句结构命名。

disable :可以终止命名块的执行,可以用来从循环中退出、处理错误等。

27.Verilog 条件语句

if,选择器

if (condition1) true_statement1 ;

else if (condition2) true_statement2 ;

else if (condition3) true_statement3 ;

else default_statement ;

28.Verilog 多路分支语句

case,选择器

case(case_expr)

condition1 : true_statement1 ;

condition2 : true_statement2 ;

……

default : default_statement ;

endcase

29.Verilog 循环语句

while, for, repeat, forever

循环语句只能在 always 或 initial 块中使用,但可以包含延迟表达式。

while (condition) begin

…

end

for(initial_assignment; condition ; step_assignment) begin

…

end

repeat (loop_times) begin

…

end

forever begin

…

end

30.Verilog 过程连续赋值

deassign,force,release

assign(过程赋值操作)与 deassign (取消过程赋值操作)表示第一类过程连续赋值语句。赋值对象只能是寄存器或寄存器组,而不能是 wire 型变量。

force (强制赋值操作)与 release(取消强制赋值)表示第二类过程连续赋值语句。

使用方法和效果,和 assign 与 deassign 类似,但赋值对象可以是 reg 型变量,也可以是 wire 型变量

因为是无条件强制赋值,一般多用于交互式调试过程中,不要在设计模块中使用。

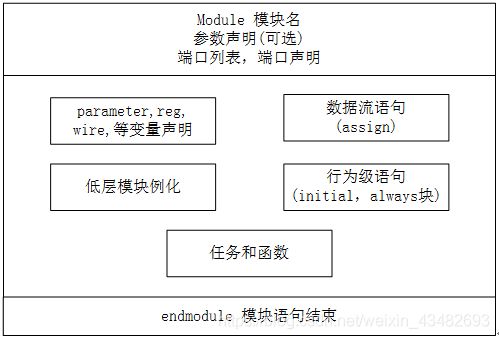

31.Verilog 模块与端口

模块是 Verilog 中基本单元的定义形式,是与外界交互的接口

模块定义必须以关键字 module 开始,以关键字 endmodule 结束。

端口模块与外界交互的接口。对于外部环境来说,模块内部是不可见的,对模块的调用只能通过端口连接进行。模块的定义中包含一个可选的端口列表,一般将不带类型、不带位宽的信号变量罗列在模块声明里。下面是一个 PAD 模型的端口列表

module pad(

DIN, OEN, PULL,

DOUT, PAD);

一个模块如果和外部环境没有交互,则可以不用声明端口列表。例如之前我们仿真时 test.sv 文件中的 test 模块都没有声明具体端口。

module test ; //直接分号结束

… //数据流或行为级描述

endmodule

32.Verilog 带参数例化

defparam,参数,例化,ram

可以用关键字 defparam 通过模块层次调用的方法,来改写低层次模块的参数值。

第二种方法就是例化模块时,将新的参数值写入模块例化语句,以此来改写原有 module 的参数值。