Quartus 12的TimeQuest Timing Analyzer

Quartus 12的TimeQuest Timing Analyzer

1.在Quartus II软件打开和设置设计

安装路径下\qdesigns\fir_fliter文件。在Processing 菜单上,指向Start,点击Start Analysis &Synthesis。

2.运行TimeQuest Timing Analyzer

在Tools 菜单中,单击TimeQuest Timing Analyzer,如图。

3.创建一个Post-Map时序网表

1. 在Netlist 菜单上,点击Create Timing Netlist。 出现Create Timing Netlist 对话框。

2. 在Input netlist 中,选择Post-Map。

3. 点击OK。

注意:您不能在Tasks面板中使用Create Timing Netlist命令来创建一个post-map时序网表。默认情况下,Create Timing Netlist 需要一个post-fit 数据库。

Input netlist选"Post-map",按OK,即会建立Timing Netlist完成。 (看到"Create Timing Netlist"項,打綠色勾勾) (看 到"Create Timing Netlist"项,打绿色勾勾)

5.指定时序要求

必须在fir_filter 设计中定义两个时钟。每个时钟的属性列表请参考。

| 时钟端口名称 |

要求 |

| Clk |

50/50占空比的50MHz |

| Clkx2 |

60/40占空比的100MHz |

1. 在Constraints 菜单中,点击Create Clock。出现CreateClock 对话框。

2. 在表2-2 中对50 MHz 时钟指定参数。对100 MHz 时钟重复这些步骤。

执行到第三步时会出现下图所示对话框,进行相应设置。

6.更新时序网表

在Tasks 面板中,双击Update Timing Netlist 命令。

7保存Synopsys Design Constraints (SDC)文件。

1. 在Tasks 面板中,双击Write SDC File 命令。出现WriteSDC File 对话框。

2. 在File Name 栏输入filtref.sdc。

8 对初始时序网表生成时序报告。

在Tasks 面板中,双击Report SDC 命令。

Task面板中双击Report Clock命令,总结所有的时钟。

Task面板中双击Report Clock Transfer命令,验证所有时钟到时钟的传输是有效的。

Clock Transfers 报告表明在clk (源时钟)和clkx2 (目的时钟)之间存在跨时钟域

路径。共有16 条路径,其中clk 为源节点提供时钟, clkx2 为目的节点提供时钟。

在fir_filter 设计中,不必分析clk 至clkx2 的时钟传输,因为它们是忽略路径。通

过表2-13 中的程序声明clk 至clkx2 的路径为伪路径。当完成该程序后,TimeQuest

Timing Analyzer 表明Clock Transfers 报告是过时的。

生成伪路径1. 在Clock Transfers 报告中,在From Clock 列选择clk。

2. 右击并选择Set False Paths Between Clock Domains。这个命令表明将所有由clk 驱动的源寄存器到由clkx2 驱动的目的寄存器之间的路径设为伪路径。

更新时序网表。

保存约束文件到SDC

9 执行Timing-Driven 编译

1. 在Project 菜单中,点击Add/Remove Files In Project。出

现Add/Remove Files In Project 对话框。

2. 通过浏览来选择.sdc。

3. 点击OK。

在Processing 菜单中,点击Start Compilation。

10 要充分约束fir_filter 设计,约束所有的输入和输出端口。使用Set Input Delay 和

Set Output Delay 对话框,或set_input_delay 和set_output_delay 约束来指定输

入和输出延迟值。

1. 在Constraints 菜单中,点击Set Input Delay。出现Set

Input Delay 对话框。

2. 输入以下内容:

Clock name: clk

Delay value: 2

Targets: [get_ports {d[0] d[1] d[2] d[3] d[4] d[5] d[6] d[7] newt reset}]

3. 在Constraints 菜单中,点击Set Output Delay。出现SetOutput Delay 对话框。

4. 输入以下内容:

Clock name: clk

Delay value: 1.5

Targets: [get_ports {yn_out[0] yn_out[1] yn_out[2] yn_out[3] yn_out[4] yn_out[5]\yn_out[6] yn_out[7] yvalid follow}]

记住读取新的约束后更新时序网表。

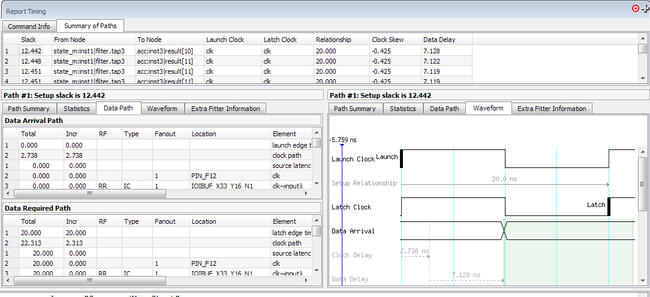

1. 在Tasks 面板中,双击Report Timing。出现Report Timing

对话框。

2. 输入以下内容:

To Clock: clk

To: acc:inst3|result*

Report number of paths: 10

3. 剩下其它的栏使用默认的设置。

双击Report Timing得到如下图