TLD7002学习笔记(一)-芯片介绍

文章目录

-

- 1. 前言

- 2. TLD7002-16ES简介

- 3. TLD7002-16ES基本功能介绍

-

- 3.1 引脚和功能框图

- 3.2 状态机

-

- 3.2.1 正常工作时状态机

- 3.2.2 OTP烧录或者仿真时的状态机

- 3.3 GPIN0和GPIN1引脚

- 3.4 器件地址

- 3.5 电流配置

- 3.6 PWM配置

- 3.7 并行输出&热降额&热过载保护

- TLD7002-16ES诊断功能

-

- 4.1 VFWD测量

- 4.2 VGPIN、VLED、VS测量

- 4.3 VOUT最小值测量

- 4.4 电压调节反馈

- 4.4 开路检测

- 4.5 单颗LED短路检测

- 4.6 警告

- 4.7 错误管理以及重复确认

- 4.8 诊断的使能、采样延时、去抖动

- 4.9 ERRN引脚

- 4/10 错误标志的清除

- TLD7002-16ES通讯协议

-

- 5.1 物理层

- 5.2 数据链路层

- 5.3 传输层

- 5.4 帧结构

- 5.5 帧类别

- 参考资料

1. 前言

英飞凌最近推出了符合功能安全ASIL-B等级的LED多通道线性恒流源驱动,有许多客户已经投入资源在熟悉该芯片。笔者最近也在学习该芯片,并将学习过程记录下来,分享给大家。

本篇文档是学习笔记的第一篇,主要是对TLD7002-16ES的整体介绍,为后面的软件控制以及OTP烧录等做铺垫。

2. TLD7002-16ES简介

TLD7002-16ES的features如下:

- 16路低边的LED恒流输出通道

- 每通道电流最高到76.5mA

- 通道之间可以并联输出

- 16个通道都可以单独配置电流大小,范围从5mA到76.5mA,分辨率为6-bit

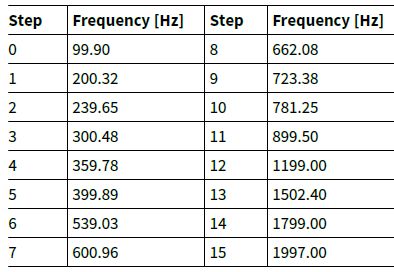

- PWM频率的配置范围从100Hz到2kHz,分辨率为4-bit

- 每个通道的PWM占空比可以单独配置,范围从0%到100%,分辨率为14-bit

- 可配置的热降额(thermal derating)

- 可配置的LED开路,短路和单一LED短路的阈值

- 两路模拟输入可用于外部器件(NTC/PTC)的电压测量

- 集成CAN FD收发器,使用HSLI通信(基于UART),最高通讯速率可达2MBit/s

- 根据ISO26262流程开发,达到ASIL-B功能安全等级

- 符合AEC-Q100

3. TLD7002-16ES基本功能介绍

3.1 引脚和功能框图

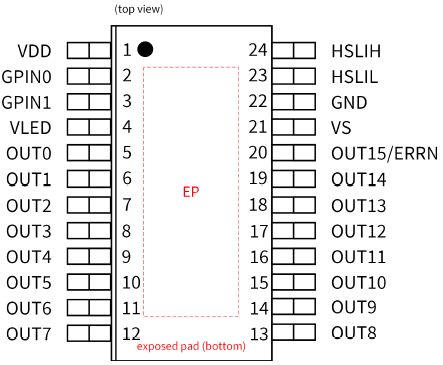

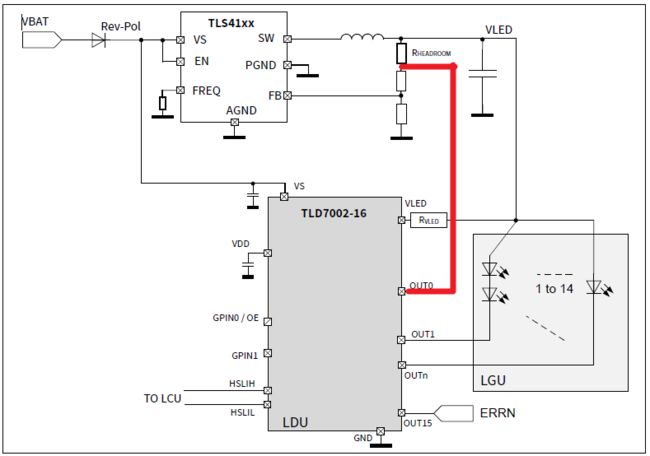

TLD7002-16ES的引脚分布如下图:

其中,各引脚说明如下:

- VS是电源供电引脚,也可用于LED的正向电压测量

- VLED可用于LED的正向电压测量

- VDD可用作NTC/PTC电阻的电压参考,或者作为HSLI总线的电压参考,或者给CAN收发器供电

- EP用作散热焊盘

- OUT0-OUT15,恒流源输出,连接到LED的阴极

- ERRN 错误反馈引脚

- GPIN0和GPIN1,用作电压测量(模拟输入)或者功能切换(数字输入)

- HSLIH和HSLIL,用作HSLI通讯,全称为High Speed Lighting Interface

TLD7002-16ES的功能框图如下:

主要的功能在上面的features已经罗列,这里就不再赘述。

补充说明下OTP:

TLD7002-16ES内部有一块OTP区域(只能写一次),包含了44个寄存器,其中地址靠前的39个用于配置TLD7002-16ES的功能,地址靠后的第40个留给用户放置客制化信息,最后4个存放OTP烧录反馈。同时和前39个OTP寄存器对应的还有存在RAM区域的可变寄存器,上电之后会从对应的OTP寄存器获取配置值。

3.2 状态机

TLD7002-16ES有两种状态机,分别是指示正常工作和OTP烧录/仿真时的状态切换。

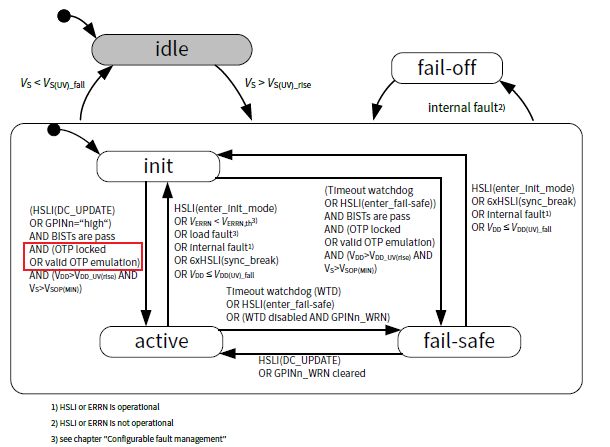

3.2.1 正常工作时状态机

正常工作时的状态机如下图:

- TLD7002-16ES的绝大部分功能配置(电流,PWM,诊断信息读取)都需要进入active mode才能生效。

- 如上图红框所示,全新的芯片在进入active mode时有一个必要条件是需要进行OTP烧录或者进入OTP仿真。

- fail-safe mode下芯片的功能参数需要在对应的OTP寄存器提前写入。

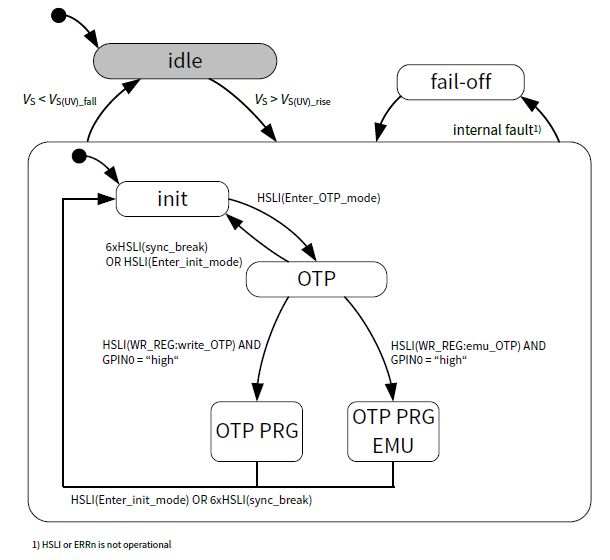

3.2.2 OTP烧录或者仿真时的状态机

OTP烧录或者仿真时的状态机如下图:

- 当芯片进行OTP烧录时,VS电压需要在15.5V到20V之间。

- 由于OTP烧录只有第一次有效,所以如果前期参数不确定且芯片紧缺的情况下建议先OTP仿真模式配置需要的参数,然后切换芯片状态到init mode再到active mode,最后进行功能测试。

3.3 GPIN0和GPIN1引脚

GPIN0和GPIN1都可以配置为模拟输入或者数字输入引脚,需要通过OTP进行烧录配置。未进行过OTP烧录的芯片默认GPIN0为数字输入,GPIN1为模拟输入。

当作为数字输入引脚时,有如下几种用途:

- 当其他条件满足时,即使HSLI不发DC_UPDATE命令,拉高GPIN0或者GPIN1也可以使芯片进入active mode。

- GPIN0可以通过OTP配置为控制所有通道输出全开(GPIN0=high)或者全关(GPIN=low),即ouput enable (OE) feature。

- GPIN1和GPIN0都可以通过OTP配置为直接驱动相关联的输出通道输出预设值的PWM占空比(GPIN0,GPIN1=low),GPIN1的优先级比GPIN0高。

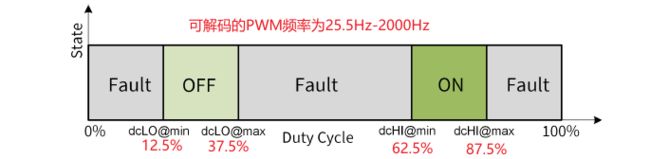

- GPIN0和GPIN1的High/Low状态,既可以是引脚上稳定的高电平或者低电平,也可以是固定范围的占空比值,如下图所示,ON的范围代表High状态,OFF的范围代表Low状态。

当作为模拟输入引脚时,可以用来测量外部器件(如NTC、PTC)的电压,测量的数值会保存在对应的VGPIN0和VPIN1寄存器中。

进行如上功能配置的相关OTP寄存器为OTP_CUST_CFG0,OTP_CUST_CFG5,OTP_CUST_CFG6,详情查看寄存器描述。

3.4 器件地址

器件地址没法通过外部引脚进行配置,只能通过将地址(1-31)写入对应的OTP寄存器(OTP_SLAVE_ID的高5位)进行配置。没有烧录过的TLD7002-16ES的地址默认为1。

在TLD7002-16ES的OTP烧录阶段,可以使用默认地址0x01或者广播地址0x00和芯片通讯从而进行烧录。

3.5 电流配置

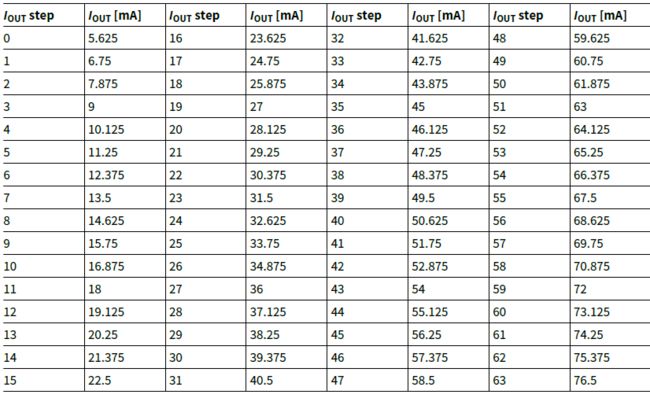

TLD7002-16ES的通道电流一共有64step(6-bit)可配,如下图所示:

用户可以通过对应的OTP寄存器(如OTP_CH_ISET_0等)写入每个通道对应的默认电流值,同时也是fail-safe状态下的电流值,用户可以后续通过对应的RAM寄存器(如LD_PWM_DAC_CFG0)进行电流值的修改。

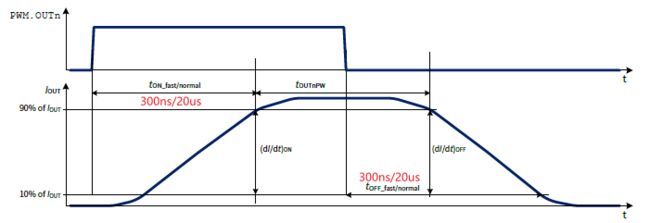

TLD7002-16ES有两种开关模式,分别为Normal switch mode 和Fast switching mode,两种模式下电流上升下降的速度不一样,如下图:

3.6 PWM配置

TLD7002-16ES内部有一个PWM发生器,可通过对应的OTP寄存器(OTP_CUST_CFG0的低4位)去配置PWM频率,范围从100Hz到2KHz,如下图所示:

配置完PWM的频率之后,就需要单独配置每个通道的PWM占空比,正常工作时通过对应的RAM寄存器(LD_PWM_DC_CFG)进行配置,分辨率为14-bit;fail-safe模式时的PWM占空比通过对应的OTP寄存器(如OTP_PWM_DC_GPIN1_0等)进行配置,分辨率为8-bit。

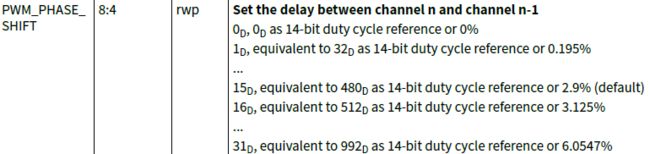

TLD7002-16ES还有PWM移相功能,通过对应的OTP寄存器(OTP_PWM_PHASE_EN,OTP_CUST_CFG0)进行配置。另外,PWM的移相参数OTP_CUST_CFG0[8:4]需要在14bit占空比数值LD_PWM_DC_CFG的bits[9:5]范围内,如下图寄存器所示:

3.7 并行输出&热降额&热过载保护

为了降低单一通道输出负载过高的情况,TLD7002-16ES也提供了Power shift和 paralle1 output两种通道方式并联的方式。Power shift需要在对应的OTP寄存器(OTP_CUST_CFG7,OTP_CUST_CFG8)进行配置。大概示意图和可进行Power shift并联方式的通道如下所示:

热降额功能可以配合内部的温度传感器或者GPIN0上面的电压进行工作,当达到设定的开始降额温度( T J s t a r t T_{Jstart} TJstart)或者电压( V D E R _ s t a r t V_{DER\_start} VDER_start)时,开始线性地降低电流,直到达到设定的停止降额温度( T J s t o p T_Jstop TJstop)或者电压( V D E R _ s t o p V_{DER\_stop} VDER_stop)。

热降额功能开启时,Power shift功能不可用。

热过载保护的功能可以设置发生热过载事件之后选择直接关闭输出通道或者当温度低于一定值之后打开输出通道。

TLD7002-16ES诊断功能

TLD7002-16ES具备的诊断功能有:

- 开路诊断

- VS和VLED两个供电引脚的短路检测

- 相邻输出通道的短路检测

- 单颗LED短路检测

- VS, GPINn, VLED, min(VOUTn) and VFWDn的数字式反馈

- ERRn错误引脚反馈(使能的情况下)

- 可配置的错误管理、包括错误发生之后的反馈方式、执行流程

接下来进行详细描述。

4.1 VFWD测量

VFWD可以是VLED-VOUT(诊断组1)或者VS-VOUT(诊断组0),具体看对应的OTP寄存器的配置(OTP_CUST_CFG4).如果VFWD用于测量LED负载的正向电压,OTP的配置需要和LED阳极的供电引脚(可以选择VLED或者VS)一致。

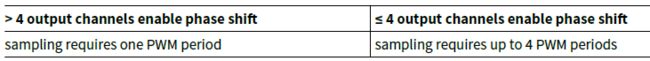

如上图所示,VFWD的测量需要在PWM处于高电平时进行。从PWM的上升沿开始,经过 t d i a g _ d l y t_{diag\_dly} tdiag_dly 的时间开始采样,再经过 t d i a g _ o n t_{diag\_on} tdiag_on 的时间可以获得采样结果。其它的注意事项如下:

- 如果相邻两个通道没有相位差,那么后面采样的通道不需要再增加 t d i a g _ d l y t_{diag\_dly} tdiag_dly

- 相邻两个通道的相位差 t p h s t_{phs} tphs 应该大于 t d i a g _ d l y t_{diag\_dly} tdiag_dly+2* t d i a g _ o n t_{diag\_on} tdiag_on

- 通道的PWM脉宽 t O U T n P W t_{OUTnPW} tOUTnPW 需要满足 t O U T n P W t_{OUTnPW} tOUTnPW> t d i a g _ d l y t_{diag\_dly} tdiag_dly+ t d i a g _ o n t_{diag\_on} tdiag_on(移相功能使能),或者 t O U T n P W t_{OUTnPW} tOUTnPW> t d i a g _ d l y t_{diag\_dly} tdiag_dly+N* t d i a g _ o n t_{diag\_on} tdiag_on(移相功能关闭,N为前面关闭移相功能的通道数)

- 每个PWM周期完成一次采样转换并持续更新转换结果

4.2 VGPIN、VLED、VS测量

VGPIN、VLED和VS的测量结果会保存在对应的RAM寄存器中,这几个通道的采样时间的需求一致,如下表:

4.3 VOUT最小值测量

TLD7002-16ES可以在每个PWM周期采样一次所有通道的输出电压最小值。OUT0和OUT15不做恒流源输出功能时,无法采集VOUT的最小值。

4.4 电压调节反馈

OUT0可以连接到外部DCDC的FB引脚,调节DCDC的输出电压。此功能的开启需要设置对应的OTP寄存器(OTP_CUST_CFG0的bit11)。

推荐的参考设计如下图:

4.4 开路检测

TLD7002-16ES能够检测到开路故障,需要同时满足以下调节:

- 输出通道处于ON的状态;

- VOUT不大于VOUT,OL_th的状态持续 n d e b o u n c e n_{debounce} ndebounce 个PWM周期;

- VS不小于 V D E N _ t h r e s h o l d V_{DEN\_threshold} VDEN_threshold(当VS作为LED阳极时);

- VLED不小于 V D E N _ t h r e s h o l d V_{DEN\_threshold} VDEN_threshold(当VELD作为LED阳极时)。

关于 V D E N _ t h r e s h o l d V_{DEN\_threshold} VDEN_threshold 和 n d e b o u n c e n_{debounce} ndebounce 的配置,后面章节会有说明。

4.5 单颗LED短路检测

单颗LED的短路检测依赖于VFWD测量结果,当以下条件成立时,认为TLD7002-16ES发生了短路故障。

- 0 ≤ \leq ≤ V F W D n V_{FWDn} VFWDn ≤ \leq ≤ V S L S t h _ m V_{SLSth\_m} VSLSth_m 持续 n d e b o u n c e n_{debounce} ndebounce 个PWM周期,其中m=0或1;

- 输出脉宽符合测量VFWD的要求;

- VS不小于 V D E N _ t h r e s h o l d V_{DEN\_threshold} VDEN_threshold(当VS作为LED阳极时);

- VLED不小于 V D E N _ t h r e s h o l d V_{DEN\_threshold} VDEN_threshold(当VELD作为LED阳极时)。

4.6 警告

警告VFWD_WRN基于VFWD的测量,可以通过对应的OTP寄存器设置阈值(OTP_CUST_CFG7)。当VFWD的结果低于阈值超过 n d e b o u n c e n_{debounce} ndebounce 个PWM周期,VFWD_WRN对应的标志就会置位。

警告OUT_SHORT_WRN对应的标志置位表示相邻的输出通道短路。该功能可以通过对应的OTP寄存器进行使能(OTP_CUST_CFG2)。因为这个警告是一个安全特性,所以更多的操作细节需要去翻阅芯片的安全手册。

警告CUR_WRN对应的标志置位表示通道实际输出的电流比OTP设置(OTP_CH_ISET)的电流值小15mA(最大值,实际在5.5mA到9mA)的时间超过 n d e b o u n c e n_{debounce} ndebounce 个PWM周期。为了避免报非预期的电流警告,推荐在OTP_CH_ISET烧录的电流值取实际用到的最小值。

警告DC_WRN对应的标志置位表示通道实际的PWM占空比值比OTP预设值的PWM占空比值高20%超过 n d e b o u n c e n_{debounce} ndebounce 个PWM周期。DC_WRN警告在使用8-bit的DC_UPDATE会误报,建议在使用14bit的DC_UPDATE命令时查询该状态位。

4.7 错误管理以及重复确认

当发生LED负载错误时(开路、单颗LED短路、热过载),或者ERR引脚的错误反馈,TLD7002-16ES可以通过对应的OTP寄存器(OTP_CUST_CFG7的DIAG_mgnt_SET位)配置芯片是否进入init mode。如果使能了该功能,芯片会关闭所有输出通道,并准备好进入重复确认的周期。

重复确认周期包含两部分,

- 第一部分是INIT phase,所有输出通道都是关闭状态

- 第二部分是ACTIVE phase,发生错误的输出通道可以打开

如上图所示,在HSLI控制情况下,

- 在INIT phase阶段,通过HSLI总线发送READ_OST命令获取详细的错误信息,然后发送DC_UPDATE命令清除错误。

- 经过 t r e c o n f t_{reconf} treconf 的时间,芯片会进入ACTIVE phase阶段,然后发送DC_SYNC命令,芯片只会打开错误的通道,持续时间为(2+ n d e b o u n c e n_{debounce} ndebounce)个PWM周期。

- 在错误通道打开的这段时间,如果检测到错误,就会继续进入INIT phase;如果未检测到错误,再过 n d e b o u n c e n_{debounce} ndebounce 个PWM周期,其它输出通道也会打开。

另外,也可以通过拉高GPIN引脚使芯片从INIT phase进入ACTIVE phase,然后芯片会自动打开错误通道进行错误检测。

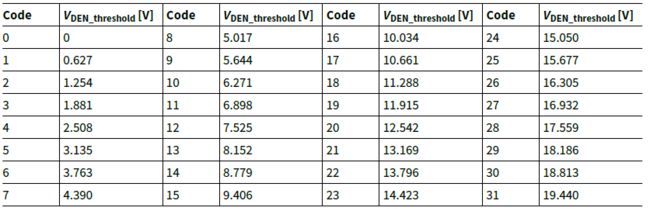

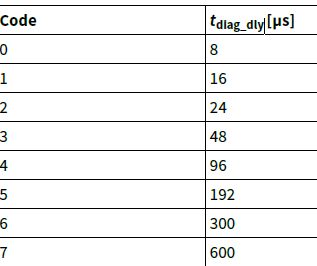

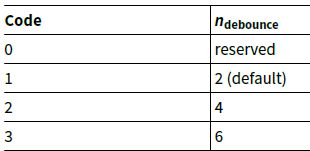

4.8 诊断的使能、采样延时、去抖动

TLD7002-16ES需要在VS或者VLED大于 V D E N _ t h r e s h o l d V_{DEN\_threshold} VDEN_threshold 时才会开启诊断功能,该阈值可以通过OTP对应的寄存器(OTP_CUST_CFG1)进行设置,阈值的所有选项如下图:

该芯片的采样延时 t d i a g _ d l y t_{diag\_dly} tdiag_dly 也可以通过对应的OTP寄存器(OTP_CUST_CFG1)进行配置,可选的延迟如下表:

诊断的去抖动时间也可以通过对应的OTP寄存器(OTP_CH_ISET_7_DEV_CFG)设置,可选的数字如下:

4.9 ERRN引脚

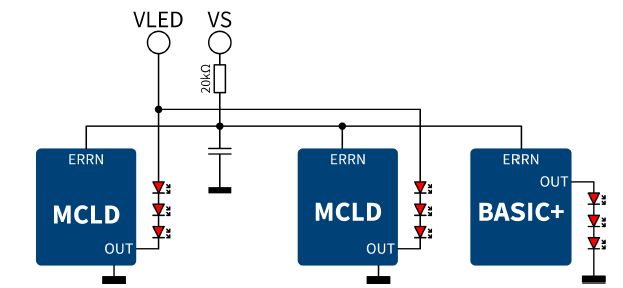

OUT15可以通过对应的OTP寄存器(OTP_CUST_CFG1)进行配置,用作错误反馈引脚,即ERRN引脚,推荐的使用电路如下图,当检测到错误时,ERR引脚会拉低(VERR电压低于2V)。

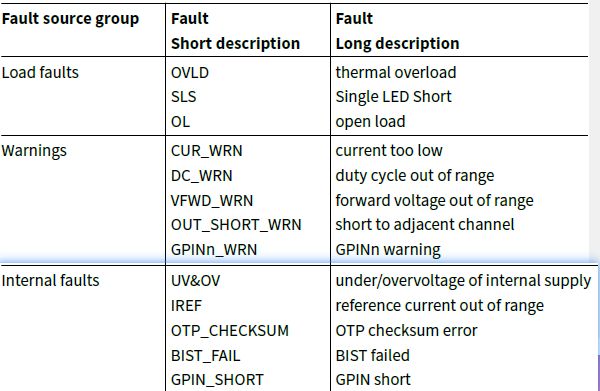

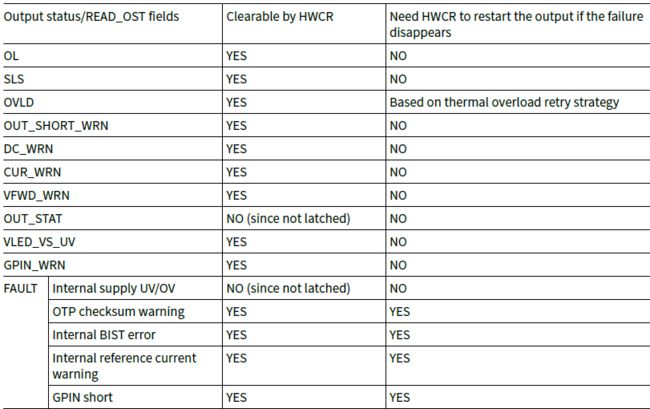

ERRN引脚可以反馈的错误如下:

4/10 错误标志的清除

当芯片诊断到错误并置位相应的标志位,建议通过HSLI总线命令清除标志位,从而可以检测到新的错误。

TLD7002-16ES通讯协议

TLD7002-16ES和MCU之间通信使用的接口称之为HSLI,即High-speed Lighting Interface。

下面从物理层、数据链路层、传输层分别介绍HSLI。

5.1 物理层

TLD7002-16ES内部集成了符合11898-2:2016标准的CAN FD收发器,支持的最高传输速率为2Mbit/s。

5.2 数据链路层

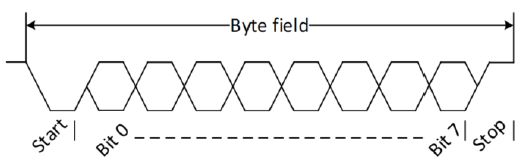

其数据链路层为标准的UART接口配置(如下图所示),即8bit数据位,无奇偶校验,1bit停止位。通信速率的范围为200Kbit/s到2Mbit/s(init模式下为100Kbit/s到500Kbit/s)。因为协议层有同步字段,所以通信速率不需要特定值,在指定范围即可。

5.3 传输层

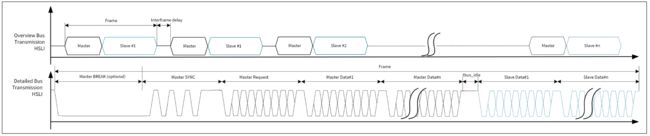

HSLI的时序如下图所示:

- 先是一个同步段(0x55)

- 然后是一个主机请求段加上N个主机发送的数据

- 最后是从机返回的数据

简化后的帧结构如下图:

另外,两帧直接的最小间隔时间(HSLI interframe delay)和最大间隔时间(HSLI watchdog timeout),分别可以通过OTP_CUST_CFG9的bit[6:4]和OTP_CUST_CFG7的bit[2:0]进行配置。

5.4 帧结构

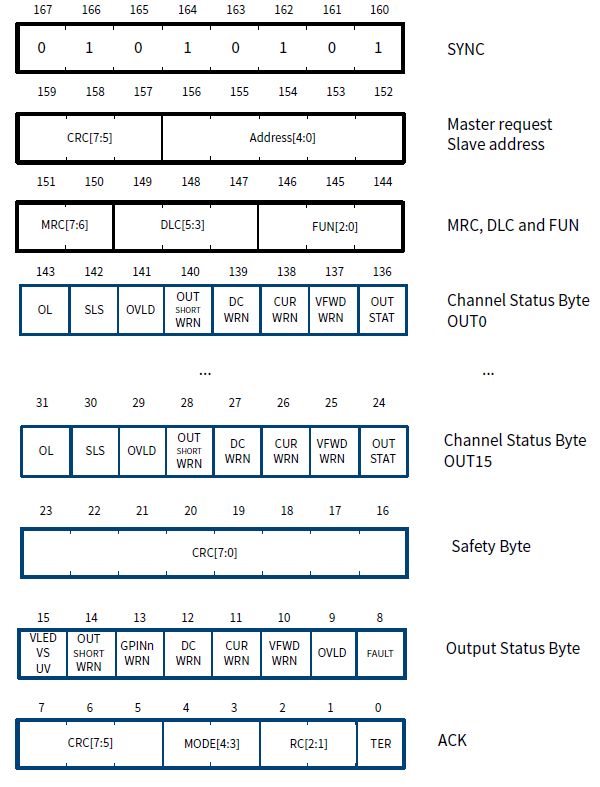

HSLI帧主要分两部分,一部分是MCU发送的,下文称为主机请求帧;一部分是TLD7002-16ES回复的,下文称为从机响应帧。

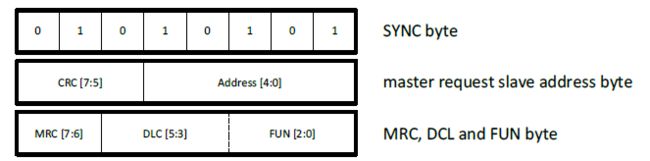

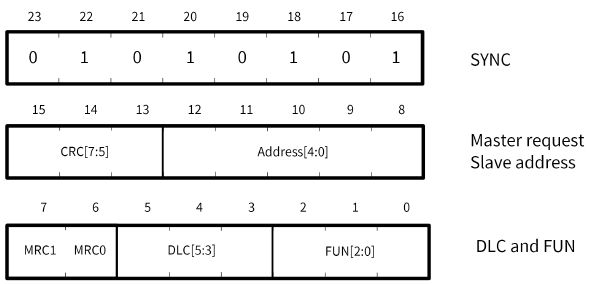

主机请求帧有帧头段和数据段组成,其中数据段并不是所有的主机请求帧都有。帧头段的组成如下图:

- 第一行的SYNC byte固定为0x55,用于波特率同步;

- 第二行的CRC[7:5]和Address[4:0]分别为CRC-3值和从机地址值(1-31,0用于广播);

- 第三行的MRC[7:6]和DLC[5:3]和FUN[2:0]分别为滚动计数码、数据长度以及功能定义段。

关于上述字节段的详细解释如下:

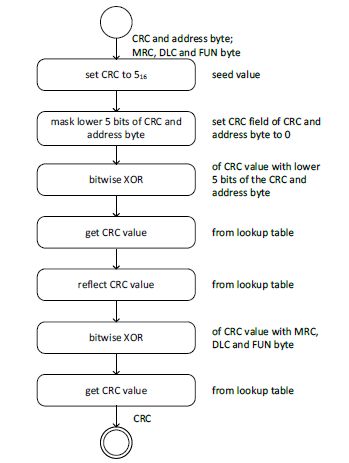

- CRC[7:5] 使用CRC-3算法,初始值为5,详细计算流程图如下:

Address[4:0] 包含5bit的从机地址,也即TLD7002-16ES的地址,所有没有烧录过的芯片的地址都为0x01,没有办法通过pin strapping功能进行地址配置,需要通过OTP编程方式烧录需要的地址。

MRC[7:6] 需要每次发数据时都增加,初始值为0x00。TLD7002-16ES每次收到主机发过来的MRC值,会和内部的保存MRC值进行比较。如果不同,会认为产生了MRC错误,同时,TLD7002的内部MRC值会更新为主机发送过来的MRC值。

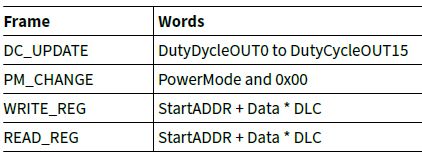

DLC[5:3] 的数值和数据段数据长度的对应关系如下:

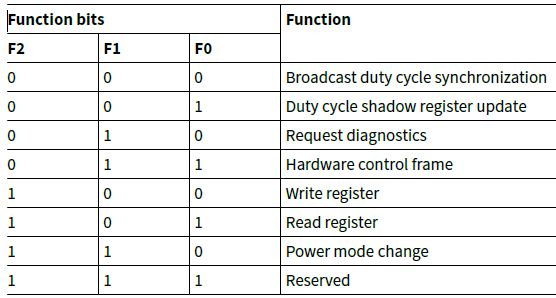

- FUN[2:0] 不同数值代表的功能如下表:

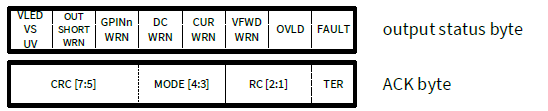

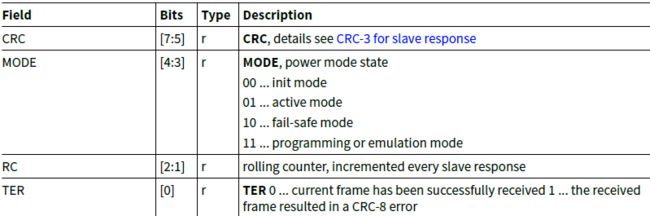

从机响应帧的终端段的组成如下图:

- 第一行主要是输出状态字节,包含各种警告和错误等,详细解释如下表;

- 第二行是响应字节,包含CRC[7:5]、芯片模式、滚动计数器和CRC错误指示,详细解释如下表。

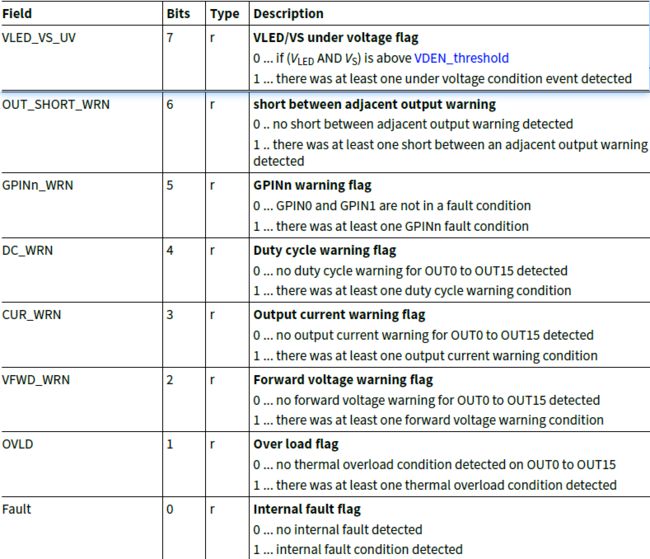

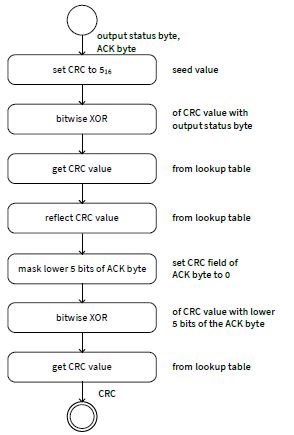

从机响应字节的CRC算法使用CRC-3算法,初始值为5,详细计算流程图如下:

不同类型的帧,数据段差别较大,代表的意义也不一样。主要有如下几种:

- DutyCycleOUTn byte,用于更改占空比的HSLI命令

- StartADDR byte,用于读写寄存器的HSLI命令中指定寄存器开始地址

- Data Word,为读写寄存器中的HSLI命令中寄存器的写入值或读出值

- Power Mode,用于更改芯片模式的HSLI命令

- Channel status Byte – OUTn,用于读取通道状态的HSLI命令

- RESET diagnostic words,用于清除错误标志的HSLI命令

5.5 帧类别

主机请求帧主要有如下几种类型:

- Broadcast duty cycle update synchronization - DC_SYNC

- Update duty cycle shadow register - DC_UPDATE

- Power mode change - PM_CHANGE

- Hardware control - HWCR

- Read diagnostics - READ_OST

- Write register content - WRITE_REG

- Read register content - READ_REG

- Sync break reset - SYNC_BREAK

5.5.1 DC_SYNC

DC_SYNC帧用于同步连接到同一个HSLI总线上的所有TLD7002-16ES的PWM占空比变化时间。

DC_SYNC帧如下三个字段的值是固定的:

- Address[4:0] = 0x00,代表广播,从机不会有响应

- DLC[5:3] = 0x0,没有数据段

- FUN[2:0] = 0x0,代表该帧的功能是同步占空比变化时间

DC_SYNC帧内容如下:

5.5.2 DC_UPDATE

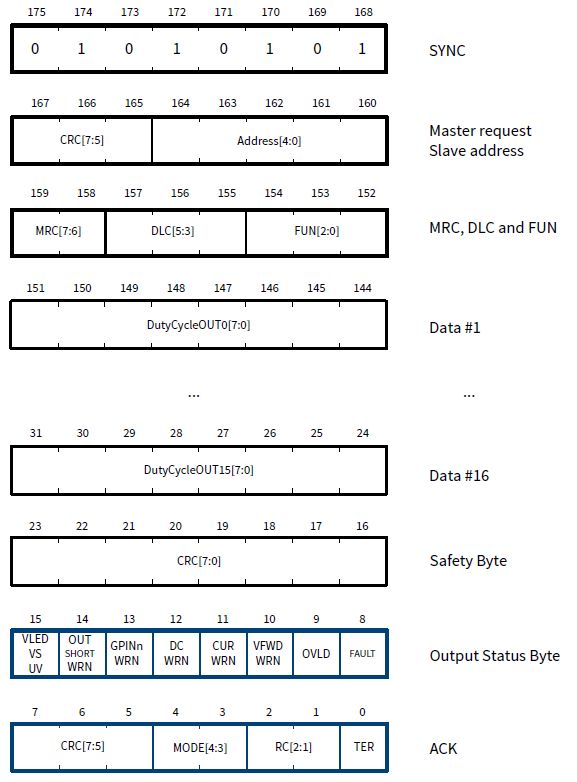

DC_UPDATE帧用于更新输出通道的占空比。

DC_UPDATE帧相关的字段设置如下:

- FUN[2:0] = 0x1,代表功能是更新占空比

- DLC[5:3] = 0x4,数据段16个字节,用于更新8-bit的占空比值

- DLC[5:3] = 0x6,数据段32个字节,用于更新14-bit的占空比值

- DLC[5:3] = 0x0,没有数据段,用于获取芯片回复的终端段

DC_UPDATE帧的内容如下:

因为更新的寄存器是14bit的,如果使用8bit的值更新,换算关系以及对应的实际占空比值如下图:

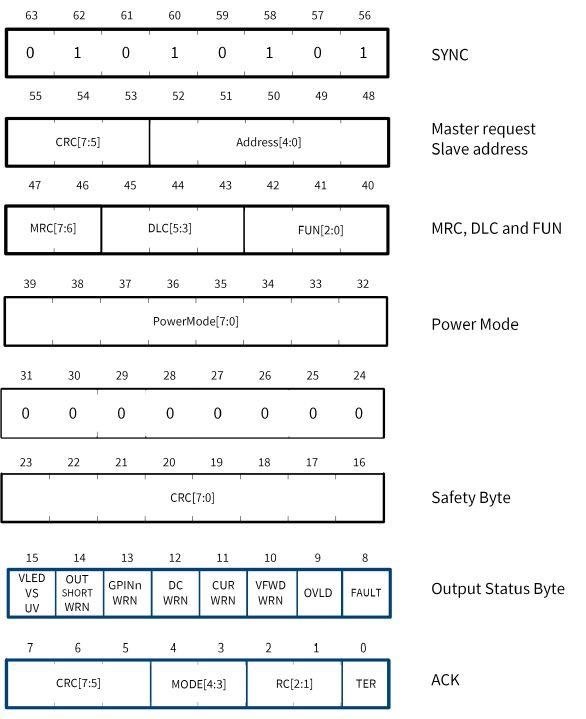

5.5.3 PM_CHANGE

PM_CHANGE帧用于切换芯片的模式。

PM_CHANGE帧如下两个字段的值是固定的:

- FUN[2:0] = 0x6,代表功能是切换芯片模式

- DLC[5:3] = 0x1,数据段是2个字节

PM_CHANGE帧的内容如下:

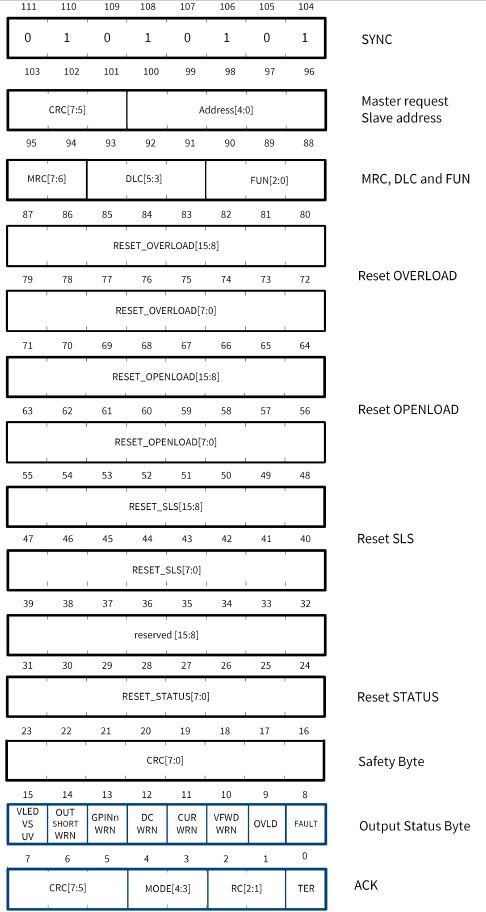

5.5.4 HWCR

HWCR帧用于清除诊断错误标志。

HWCR帧的如下两个字段的值是固定的:

- FUN[2:0] = 0x2,代表功能是清除诊断错误标志

- DLC[5:3] = 0x4,数据段是32个字节

HWCR帧的内容如下:

5.5.5 READ_OST

READ_OST帧用于读取16个通道状态。

READ_OST帧的如下两个字段的值是固定的:

- FUN[2:0] = 0x3,代表功能是读取通道状态

- DLC[5:3] = 0x3,数据段是16个字节

READ_OST帧的内容如下:

5.5.6 WRITE_REG

WRITE_REG帧用于向目标寄存器写值。

WRITE_REG帧相关的字段设置如下:

- FUN[2:0] = 0x4,代表功能是写寄存器

- DLC[5:3] = n > 0,数据段的范围是2-64个字节,看实际需求

WRITE_REG帧的内容如下(以DLC=0x01为例):

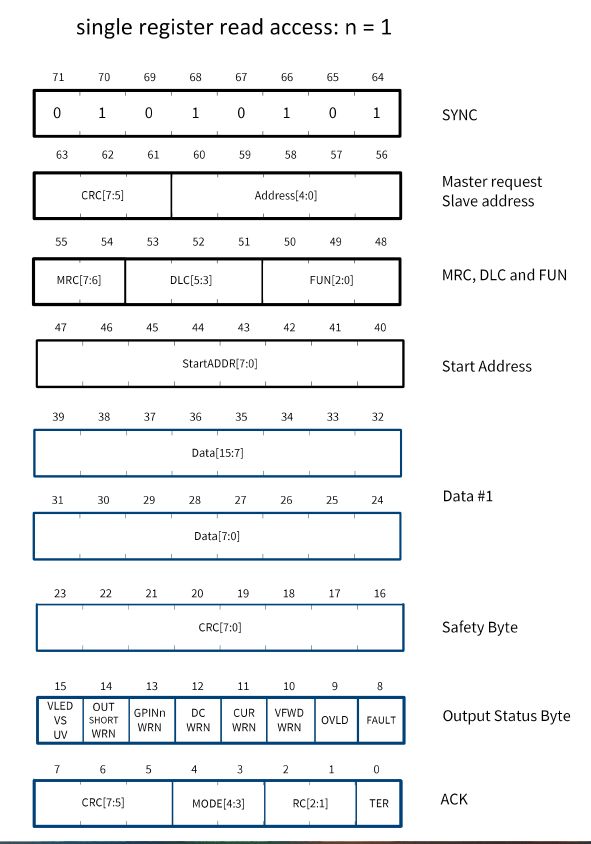

5.5.7 READ_REG

READ_REG帧用于向目标寄存器读值。

READ_REG帧相关的字段设置如下:

- FUN[2:0] = 0x4,代表功能是读寄存器

- DLC[5:3] = n > 0,数据段的范围是2-64个字节,看实际需求

READ_REG帧的内容如下(以DLC=0x01为例):

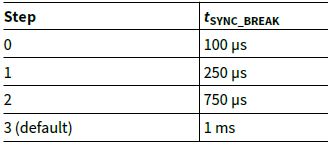

5.5.8 SYNC_BREAK

SYNC_BREAK帧用于重置HSLI的协议处理器,为一段时间的显性电平,然后再变成隐性电平,类似于LIN协议的同步间隔段。

显性电平的时间在对应的OTP寄存器(OTP_CUST_CFG9)进行配置,参数有如下几种选择。

当TLD7003-26ES检测到SYNC_BREAK,内部的协议处理器会初始化,从而:

- 主机和从机的滚动技术器会归0;

- 所有未完成的传输会被中断

- 如果SYNC_BREAK的计数器达到6,TLD7002-16ES会进行整个器件的复位并且经过 t I D L E 2 I N I T t_{IDLE2INIT} tIDLE2INIT 时间进入init模式

5.5.9 数据段的CRC算法

数据段的CRC-8算法依据CRC-8-AUTOSAR and SAE J1850,多项式为 x 8 + x 4 + x 3 + x 2 + 1 x^8+x^4+x^3+x^2+1 x8+x4+x3+x2+1,初始值为0xFF,包含的计算数据每个帧不一样,详细情况如下:

参考资料

-

TLD7002-16ES Data Sheet

-

User Manual: Infineon-TLD7002-16ES-UM-v01_20-EN

-

TLD7002-16ES software design and device driver