计算机硬件技术基础(太原理工大学):第四章

复习点

- 一、中央处理器

-

- 1、运算器

- 2、控制器

- 3、寄存器组

- 二、8086CPU

-

- 1.8086CPU总述

- 2.8086CPU的寄存器

-

- a.通用寄存器

- b.段寄存器

- c.控制寄存器

- 3.8086CPU的引脚信号及功能

-

- a.三个周期

- b.最小模式和最大模式

- c.引脚信号及功能(所有斜体的引脚都表示上面有一个横线非符号)

-

- 在最大模式和最小模式下功能相同的引脚

- 在最大模式和最小模式下功能不同的引脚

-

- 最小模式下

- 最大模式下

- 4.8086CPU对存储器的访问

-

- a.8086存储器结构

- b.存储器分段

- c.逻辑地址和物理地址

- 三、现代CPU采用的新技术

-

- 1.流水线计算机

-

- 指令流水线

- 流水线的一些计算

- 影响流水线性能的主要因素

- 2.超标量计算机

- 3.向量计算机

- 4.多核计算机

- 5.超长指令字计算机

一、中央处理器

- 组成:由运算器、控制器和寄存器组组成。

- 基本功能:处理指令、处理数据、控制时间、执行操作、暂存一定的数据、处理异常情况和响应I/O设备发出的请求。

1、运算器

- 运算器是计算机的数据处理中心。

- 构成:由算术逻辑单元ALU、通用寄存器组、多路选择器以及标志寄存器构成。

- 分类:分为定点运算器和浮点运算器,浮点运算器的结构要复杂很多。

- ALU是运算器的核心部件,完成所有的算数、逻辑运算,它完成哪一种运算由控制器发来的功能控制信号决定。

- 通用寄存器组由若干通用寄存器组成,暂存从主存中取出的数据和远算结果。使用寄存器操作可以减少访问主存的次数,提高CPU的运行速度。

- 每个多路选择器在任一时刻只允许选择一个寄存器参加运算。

- 标志寄存器用来记录一次运算后的一些重要特征。

2、控制器

- 控制器是CPU的指挥控制中心。

- 分类:

(1)组合逻辑控制器(硬布线控制器):由各种门电路构成,完全依靠硬件来产生控制信号。速度快,设计繁琐。

(2)微程序控制器:通过一段微程序产生控制信号,对应所有指令的微程序都存放在控制器的只读寄存器中。速度慢。设计简单。一条指令对应一段微程序。 - 功能:

(1)指令顺序控制:即实现指令的有序执行。

(2)操作控制:根据指令产生微命令序列。

(3)时间操作:产生计算机需要的时序信号,控制微命令发出的时刻和顺序。

(4)对异常情况和某些请求的处理 - 组成:

(1)程序计数器(PC):也叫指令指针寄存器,用来存放下一条要执行指令的存储器地址,按此地址从对应对应存储单元取出的内容就是要执行的指令。

(2)指令寄存器(IR):保存从存储器中读入的当前要执行的指令。指令分为操作码和地址码两部分。

(3)指令译码器(ID):对指令寄存器中的指令进行译码分析,指出指令的操作种类和寻址方式。指令译码器的输出作为微操作命令发生器的输入,是产生控制信号的主要依据。

(4)时序电路:决定每个微操作的开始时刻和操作的持续时间。

(5)微操作命令发生器:是控制器中最复杂的部件,可以产生所有微操作命令。微操作就是不能再分解的操作,微操作执行总是需要相应的控制信号。

3、寄存器组

- 是一组高速存储单元。

- 分类:

(1)通用寄存器:在CPU中数量最多,是调度数据的主要手段。

(2)专用寄存器:功能专一,都有特殊的用途。

二、8086CPU

1.8086CPU总述

- 有两个独立的工作单元组成,一个为执行单元(EU),另一个是总线接口单元(BIU)。EU和BIU并行工作。

- EU由ALU、16位数据暂存器、标志寄存器、8个16位通用寄存器和EU控制电路构成。数据暂存器协助ALU完成运算,暂存参加运算的数据。

- BIU由4个16位段寄存器、指令指针寄存器IP、6字节的指令队列、地址加法器、一个与EU通信的内部通信寄存器及总线控制逻辑组成。地址加法器用来将段寄存器保存的短地址和IP或EU部件提供的偏移地址相加形成20位物理地址。

- 指令的执行过程

2.8086CPU的寄存器

按照寄存器对程序员是否透明,寄存器可以分为程序可见的寄存器(在汇编语言程序设计中用到的寄存器)和程序不可见的寄存器(应用程序设计中不能使用而由系统专用的寄存器)两大类。

a.通用寄存器

(1)数据寄存器:每个寄存器可以以字的形式(16位)访问,也可以将寄存器分为两个8位的寄存器使用,如BX可以分为BH和BL两个8位寄存器。分别访问BX的高位字节和低位字节。

- AX(Accumulator):又称累加器,是算术运算的主要寄存器。在乘除指令中用来默认存放操作数和结果。此外,所有的I/O指令都是用这一寄存器与外部设备传送信息。

- BX(Base):又称基址寄存器,用来存放存储器单元的偏移地址。

- CX(Count):又称计数寄存器,常用来保存计数值,一般作为移位指令、循环或串操作等指令中的隐含计数器。

- DX(Data):又称数据寄存器,常用来存放双字数据的高16位(在乘、除法中)。就是将DX和AX组合在一起,DX用来存放高位字,AX用来存放低位字。

(2)指针和变址寄存器:

只能以字(16位)为单位使用

- SP:堆栈指针寄存器,用于存放当前堆栈段中栈顶单元的偏移地址,它可以与堆栈段寄存器SS联用指向堆栈栈顶单元。

- BP:基址指针寄存器,用于存放堆栈段中某一存储单元的偏移地址,它可以与堆栈段寄存器SS联用指向堆栈段中某一存储单元的地址。

- SI和DI:源变址寄存器和目的变址寄存器,一般与数据段寄存器DS联用,用来确定数据段中某一存储单元的地址。这两个编制寄存器具有自动增量和自动减量的功能。

b.段寄存器

8086CPU的地址线是20位的,2^20 = 1MB,8086的寄存器都是16位的,段寄存器用来存放段地址,以确定该段在主存中的起始地址。将段寄存器分为4段,分别称为代码段寄存器、数据段寄存器、堆栈段寄存器、附加数据段寄存器。

- CS:代码段寄存器,用来存储程序当前使用的代码段的段地址。

实际地址 = CS×10H + IP中的偏移地址 - DS:数据段寄存器,用来存放程序当前使用的数据段的段地址。

实际地址 = DS×10H + 指令中存储器寻址方式给出的偏移地址 - SS:堆栈段寄存器,用来存放程序当前所使用的堆栈段的段地址。采用“先进后出”的方式。

实际地址 = SS×10H + SP或BP中的偏移地址 - ES:附加数据段寄存器,用来存放程序当前使用的附加数据段的段地址。

实际地址 = ES×10H + DI中的偏移地址

c.控制寄存器

(1)指令指针寄存器(IP):用来存放下一条要读取的指令在代码段中的偏移地址,与代码段寄存器CS联用确定下一条指令的物理地址。

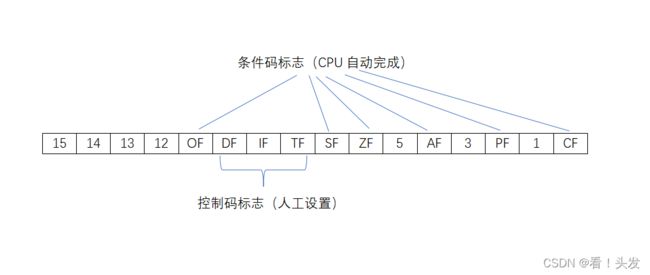

(2)FLAGS:标志寄存器,16位寄存器。9个标志位中有6个条件码标志(用来记录程序中运行结果的状态信息)和3个控制码标志。

- 进位标志CF:进行加减运算时,若运算结果的最高位发生进位或借位,CF为1,否则为0。通常用于判断无符号数运算结果是否超出了计算机所能表示的无符号数的范围;还用于双字长运算中高位字和低位字运算之间的关系。

- 辅助进位标志AF:当进行加减运算时,若运算结果的低字节的低4位向高4位(即D3位向D4位)有进位或借位,AF为1,否则为0。

- 符号标志SF:记录运算结果的符号为负时,SF为1,否则为0。

- 零标志ZF:运算结果为零时ZF为1,否则为0。

- 溢出标志OF:有符号数的运算结果产生溢出时OF为1,否则为0。字节的运算超过-128 ~ +127或字的运算超过-32798 ~ +32767时就说明溢出。

- 奇偶标志PF:用来检验数据传送是否出错。当结果的低8位中1的个数为偶数时,PF为1,否则为0。

控制码标志:

- 方向标志DF:在串处理指令中控制处理信息的方向。当DF为1时,每次操作后使编制寄存器SI和DI减小,这样就使串处理从高地址向低地址方向进行;当DF为0时,SI和DI增大,使串处理从低地址向高地址方向进行。

- 中断标志IF:用来控制是否允许中断,当IF为1时,允许CPU响应可屏蔽中断请求;当IF为0时,关闭中断,不允许CPU响应可屏蔽中断请求。

- 跟踪标志TF:用于调试时的单步方式操作。当TF为1时,每条指令执行完后产生中断,CPU处于单步运行方式;当TF为0时,CPU正常工作,程序连续执行。

3.8086CPU的引脚信号及功能

a.三个周期

(1)指令周期:CPU执行一条指令所用的时间称为指令周期。

(2)时钟周期:系统主时钟一个周期信号所持续的时间称为时钟周期。

(3)总线周期:CPU访问一次存储器或I/O端口成为一次总线操作,或执行一次总线周期。8086CPU总线周期至少由4个时钟周期组成,一个时钟周期称为一个T状态。

b.最小模式和最大模式

- 最小模式:系统总只有1个806CPU,即单处理器方式,所有的总线控制信号都由8086CPU直接产生。系统的总线控制电路被减到最少。

- 最大模式:一般用在较大规模的8086系统中,包含两个或多个微处理器,其中8086CPU是主处理器,其他的处理器称为协处理器。但是80286之后的CPU不再区分最大最小工作模式。

c.引脚信号及功能(所有斜体的引脚都表示上面有一个横线非符号)

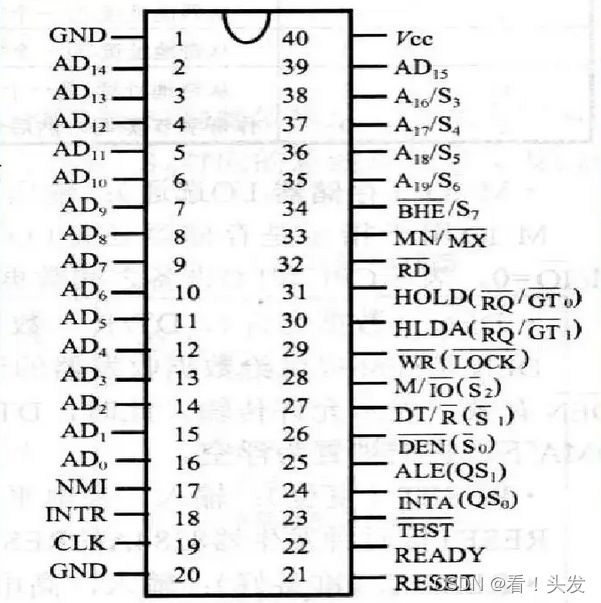

总述:8086CPU是具有40个引脚的集成电路芯片,采用双列直插式封装。8086的地址线和数据线是分时复用的,称为多路总线。8086CPU中有16个数据/地址复用引脚,有4个地址/状态复用引脚。

在最大模式和最小模式下功能相同的引脚

- 电源线和地线:地址线Vcc为第40引脚,输入,接入单一的+5V电源。地址线GND为1和20,输入,两条地线均接地。

- AD15 ~ AD0:地址/数据分时复用引脚,在T1中,给出低16位的内存单元或者I/0端口的地址。T2 ~ T4中作为数据总线D15 ~ D0使用。

- A19/S6 ~ A16/S3:这是地址/状态分时复用引脚,输出、三态总线。

T1状态下:作为地址线用。当访问存储器时,高四位地址A19 ~ A16与AD15 ~ AD0一起构成访问存储器的20位物理地址;CPU访问I/O端口时,A19 ~ AD16全部无效且输出低电平。

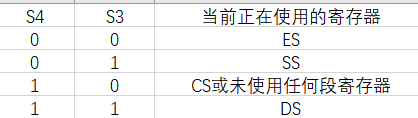

T2 ~ T4状态下:输出状态信息,此时S6为0,表示CPU当前与总线相连。S5表示中断允许标志位IF的当前位置,当IF为1时,S5为1,否则为0。S4和S3表示当前正在使用哪一个段寄存器。如下表:

- NMI:非屏蔽中断请求信号,输入,上升沿触发。此请求不收标志寄存器中中断标志位IF的状态的影响,只要此信号出现,就会在当前指令结束后立即进行中断处理。

- INTR:可屏蔽中断请求信号,输入,高电平有效。CPU在每个指令周期的最后一个时钟周期简则该信号是否有效,若此信号有效,表明有外设提出了中断请求,这个时候若IF为1,则执行完当前指令后立即响应中断,若IF为0,则该外设发出的中断请求将不被响应。程序员可通过指令STI和CLI将IF标志位置设置为0或清0。

- CLK:系统时钟。起CPU和总线控制电路提供时钟信号。

- RESET:复位信号,输入,高电平有效。8086CPU要求复位脉冲宽度不小于4个时钟周期。复位后,CPU马上结束现行操作,对内部寄存器进行初始化。8086CPU复位后CS = FFFFH、IP = 0000H,所以CPU从FFFF0H开始执行程序。

- READY:输入,实际上是所寻址的存储器或I/O端口发来的数据准备就绪信号,高电平有效。CPU在每个总线周期的T3状态对READY引脚采样,若为高电平没说明数据已准备好;若为低电平,说明数据还没准备好,CPU会在T3状态后自动插入一个或几个等待状态Tw,直到READY变为高电平,进入T4状态。

- TEST:等待测试信号,输入。当CPU执行WAIT指令时,每隔5个时钟周期最TEST引脚进行一次测试。若为高电平,表示CPU仍旧处于空闲状态进行等待;若为低电平,CPU等待状态结束,执行下一条指令,以使CPU与外部硬件同步。

- RD:读控制信号,输出。RD为0时,表示将要执行一个对存储器或I/O端口的读操作。至于从存储单元读还是从I/O读取决于M/IO信号。

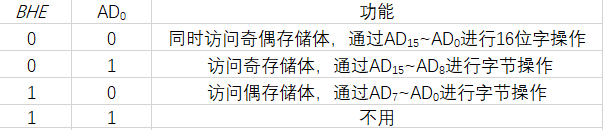

- BHE/S7:输出。8086存储器分为奇偶两个存储体,分别由奇地址和偶地址单元组成。

S7在T2 ~ T4状态下输出,S7在8086CPU中未被定义,暂时作为备用状态信号线。

BHE在总线周期的T1状态时输出,输出为低电平时,表示当前数据总线上高8位数据AD15 ~ AD8有效。BHE和A0组合的不同含义如下表:

- MN/MX:最大/最小模式控制信号,输入。接高电平时,8086CPU工作在最小模式;接低电平时,8086CPU工作在最大模式。

下面介绍

在最大模式和最小模式下功能不同的引脚

(在最上面的图中,括号内就是该引脚在最大模式下的名称)

最小模式下

- INTA:可屏蔽中断响应信号,输出。用于对外设的中断请求做出响应。INTA实际上是两个连续的负脉冲信号,第一个负脉冲通知外设接口发出的中断请求已被允许了外设接口接到第二个负脉冲后,往数据总线上放中断类型型号,以便CPU根据中断类型号到主存的中断向量表中找出对应中断的中断服务程序入口地址,从而转去执行中断服务程序。

- ALE:地址锁存允许信号,输出。在任何一个总线周期的T1状态,ALE均为高电平,表示当前数据地址/数据复用总线上输出的是地址信息,ALE信号的下降沿时则把地址装入地址锁存器中。

- DEN:数据允许信号,输出。当使用数据总线收发器时,该信号为收发器提供了一个控制信号,决定是否允许数据通过数据总线收发器。DEN为高电平时,收发器在收发两个方向上都不能传送数据;为低电平时,允许数据通过数据总线收发器。

- DT/R:数据发送/接受信号,输出。该信号用来控制数据的传送方向。DT/R为高电平时,8086CPU通过数据总线收发器进行数据传诵;为低电平时,进行数据接收。

- M/IO存储器I/O控制信号,输出。当该信号为高电平时,表示CPU正在喝存储器进行数据传诵;为低电平时,表示CPU正在喝输入/输出设备进行数据传送。

- WR:写信号,输出。WR = 0有效时,表示CPU当前正在进行存储器或I/O写操作,这个也是由信号M/IO决定是对存储器还是I/O端口执行写操作。

- HOLD:总线保持请求信号,输入。8086CPU之外的总线主设备要求占用总线时,通过该引脚向CPU发出一个高电平的总线保持请求信号。

- HLDA:总线保持响应信号,输出。当CPU接收到HOLD的信号后,若CPU允许让出总线,那么就会在当前总线周期完成时,在T4状态发出高电平有效的HLDA信号给予相应。

最大模式下

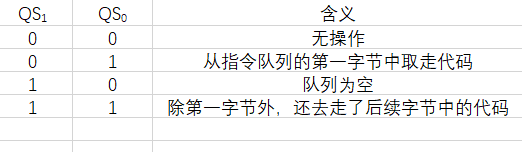

- QS1、QS0:指令队列状态信号,输出。他们两个的不同组合状态如下:

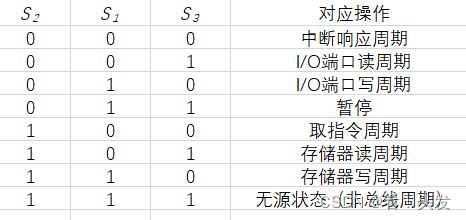

- S0、S1、S2:总线周期状态信号,输出。他们三个的组合表示含义如下:

- LOCK:总线封锁信号,输出。为低电平时,系统中其他总线主设备不能获得总线的控制权而占用总线。

- RO/GT1、RQ/GT0:总线请求信号/总线授权信号。后者比前者优先级高。这两个信号作用相同,可供CPU以外的两个总线主设备向CPU发出使用总线的请求信号和接受CPU对总线的请求的授权信号。

4.8086CPU对存储器的访问

a.8086存储器结构

- 因为8086CPU有20条地址线,所以能寻址1M个存储单元,每个存储单元中存放一个8位的二进制信息。

- 每个存储单元用唯一的一个地址码标识,地址码是一个无符号整数,用16进制表示,其范围为00000H ~ FFFFFH,这种将存储器空间按字节地址号顺序排列的方式成为按字节编址。

- 00001H单元的内容为8EH,记作(00001H)= 8EH。

- 若要存放字型数据(16位二进制数),就将字的低位字节存放在低地址单元,高位字节存放在高地址单元,且低地址作为字型数据的存储地址。如数据5FBCH,存放在00121H和00120H两个单元中,记作(00120H)= 5FBCH.

- 若存放双字型数据,就要占用4个存储单元。同样,低字节存放在低地址单元,高字节存放在高地址单元,低地址作为双字型数据的存储地址。

- 以上的存储方式成为小端存储

- 8086存储器允许字从任何地址开始存放。

- 当字的地址是偶地址时,称字的存储是对准的;当字的地址是奇地址时,称为字的存储是未对准的。

- 8086CPU数据总线16位。对于访问一个偶地址的字的指令,可一次访问成功,需要一个总线周期了对于访问一个奇地址字的指令,需要两个总线周期(CPU自动完成)。所以数据字存放在偶地址开始的存储单元中。

b.存储器分段

- 将1MB的存储器分为若干逻辑段,每个逻辑段的最大长度为64KB,每个逻辑段的起始地址默认是16的倍数。段的起始地址的低4位二进制数必须是0,高16位称为该段的段地址。

- 段内存储单元的地址可以用相对起始地址的16位偏移量来表示,这个偏移量就是偏移地址。(偏移地址本质上是段内某单元地址和段首地址的差,范围为0000H ~ FFFFH)

- 逻辑段之间可以相连,也可以不相连。

c.逻辑地址和物理地址

在这里举例说明:B027:EF7F

- 这是一个逻辑地址

- 其中B027表示段地址,EF7F表示其偏移地址

- 物理地址为B027H × 10H + EF7FH = B0270H + EF7H = BF1EFH

计算公式:物理地址 = 段地址 ×10H + 偏移地址

它在存储器中的结构如下图:

不同段的物理地址应使用不同的段寄存器,按约定进行。但允许有特例的情况,称为段超越前缀:不用约定段地址,而是用可修改的段地址和偏移地址来形成所需的物理地址。具体情况如下图:

三、现代CPU采用的新技术

1.流水线计算机

指令流水线

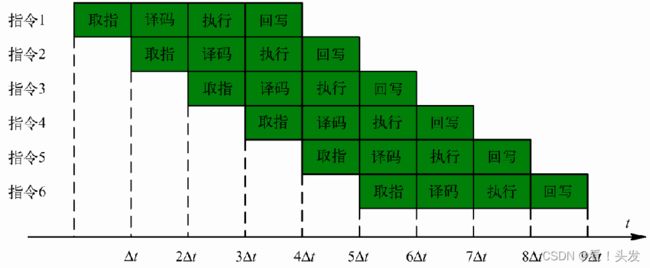

假设我们将一条指令的过程分解为4个阶段,且各阶段时间等长都为∆t。

那么正常情况下完成6条指令所需的时间为6 × 4∆t个时间。

但是采用指令的流水线技术后,我们可以将时间缩短成9∆t个时间,具体如下:

这一技术,让完成不同功能所涉及的硬件部分在逻辑上相互独立,让不同逻辑功能部件在时间上并行工作。提高了执行速度。

这一技术,让完成不同功能所涉及的硬件部分在逻辑上相互独立,让不同逻辑功能部件在时间上并行工作。提高了执行速度。

流水线的一些计算

- k条流水线执行n条指令所需要的的时间:Tk = k∆t + (n-1)∆t

- 流水线吞吐量:TP = n/TK

- 流水线加速比:S = Ts/Tk,其中Ts是串行方式执行所用时间。

- 流水线效率:E = n /(k + n - 1)

影响流水线性能的主要因素

(1)资源相关

(2)数据相关

(3)控制相关

2.超标量计算机

3.向量计算机

多用于需要对大量的数组进行高精度计算的工程中,如空气动力学、气象学、天体物理学、原子物理等。