10G以太网

概述

- 该文章得验证平台位xilinx KCU105开发板,实现了双通道10g eth收发,以及内外循环。

10g以太网系统框图

-

时钟

- PCS/PMA接收外部差分参考时钟(156.25MHz),经过内部锁相环输出coreclk(156.25MHz),从而驱动整个系统工作

-

数据

-

控制(监测)

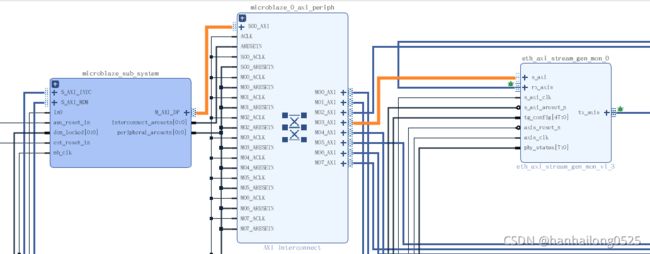

- MicroBlaze通过axi_lite接口控制User和MAC模块,MAC与PCS/PMA模块间通过MDIO总线走控制信号,后续内容有详细介绍。

一、 PCS/PMA内部时钟

二、 XGMII帧格式

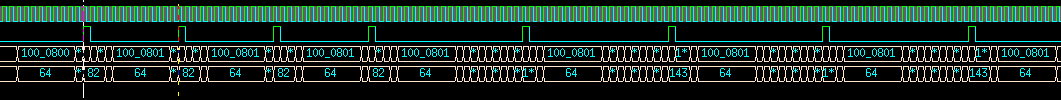

- 若payload_size = 64,源地址48’h1111_0000_0000,目标地址48’h2222_0000_0000,发送完3frame后payload_size = 125

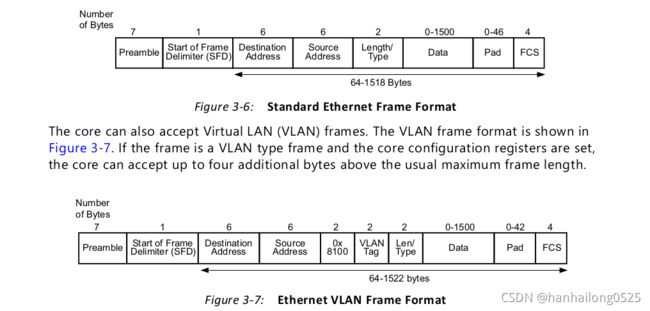

- 根据XGMII需求:帧间最小间隔(12+Byte) + 前导码(7Byte)+ 帧开始符(1Byte)+ ethernet_header(16Byte) + Payload2(62Byte)+ FCS(4Byte)

- ethernet_header(16Byte) = MAC目标地址(6Byte)+ MAC源地址(6Byte)+ 长度/类型(2Byte)+ Payload1(2Byte)

assign ethernet_header [47:0] = XIL_MAC_ID_OTHER; assign ethernet_header [95:48] = XIL_MAC_ID_THIS; assign ethernet_header [111:96] = {data_payload[7:0], data_payload[15:8]}; assign ethernet_header [127:112] = seq_no_g; - 实际XGMII格式为

frame0_1 : 0707_0707_0707_0707 frame0_2 : df55_5555_5555_55fb frame0_3 : 0000_2222_0000_0000 frame0_5 : 0000_4000_1111_0000 frame0_6 : 0000_0000_0000_0000 frame0_7 : 0000_0000_0000_0000 frame0_8 : 0000_0000_0000_0000 frame0_9 : 0000_0000_0000_0000 frame0_10: 0000_0000_0000_0000 frame0_11: 0904_0000_0000_0000 frame1_1 : 0707_0707_07fd_fd4a frame1_2 : 0707_0707_0707_0707 frame1_3 : df55_5555_5555_55fb frame1_4 : 0000_2222_0000_0000 frame1_5 : 0001_4000_1111_0000 frame1_6 : 0001_0001_0001_0001 frame1_7 : 0001_0001_0001_0001 frame1_8 : 0001_0001_0001_0001 frame1_9 : 0001_0001_0001_0001 frame1_10: 0001_0001_0001_0001 frame1_11: 0001_0001_0001_0001 frame1_12: 0001_0001_0001_0001 frame1_13: d864_0001_0001_0001 frame2_1 : 0707_0707_07fd_3991 frame2_2 : 0707_0707_0707_0707 frame2_3 : df55_5555_5555_55fb frame1_4 : 0000_2222_0000_0000 frame1_5 : 0002_4000_1111_0000 frame1_6 : 0002_0002_0002_0002 frame1_7 : 0002_0002_0002_0002 frame1_8 : 0002_0002_0002_0002 frame1_9 : 0002_0002_0002_0002 frame1_10: 0002_0002_0002_0002 frame1_11: 0002_0002_0002_0002 frame1_12: 0002_0002_0002_0002 frame1_13: ad85_0002_0002_0002 frame3_1 : 0707_0707_07fd_af8c frame3_2 : 0707_0707_0707_0707 frame3_3 : df55_5555_5555_55fb frame3_4 : 0000_2222_0000_0000 frame3_5 : 0003_4000_1111_0000 frame3_6 : 0003_0003_0003_0003 frame3_7 : 0003_0003_0003_0003 frame3_8 : 0003_0003_0003_0003 frame3_9 : 0003_0003_0003_0003 frame3_10: 0003_0003_0003_0003 frame3_11: 0003_0003_0003_0003 frame3_12: 0003_0003_0003_0003 frame3_13: 7ce5_0003_0003_0003 frame4_1 : 0707_0707_07fd_6b57 frame4_2 : 0707_0707_0707_0707 frame4_3 : df55_5555_5555_55fb frame4_4 : 0000_2222_0000_0000 frame4_5 : 0004_7d00_1111_0000 frame4_6 : 0004_0004_0004_0004 frame4_7 : 0004_0004_0004_0004 frame4_8 : 0004_0004_0004_0004 frame4_9 : 0004_0004_0004_0004 frame4_10: 0004_0004_0004_0004 frame4_11: 0004_0004_0004_0004 frame4_12: 0004_0004_0004_0004 frame4_13: 0004_0004_0004_0004 frame4_14: 0004_0004_0004_0004 frame4_15: 0004_0004_0004_0004 frame4_16: 0004_0004_0004_0004 frame4_17: 0004_0004_0004_0004 frame4_18: 0004_0004_0004_0004 frame4_19: 0004_0004_0004_0004 frame4_20: 0004_0004_0004_0004 frame4_21: 0004_0004_0004_0004 frame4_22: fda1_6eb5_a404_0004 frame5_1 : 0707_0707_0707_0707 frame5_2 : 5555_55fb_0707_0707 frame5_3 : 0000_0000_df55_5555 frame5_4 : 1111_0000_0000_2222 frame5_5 : 0005_0005_0005_7d00 frame5_6 : 0005_0005_0005_0005 frame5_7 : 0005_0005_0005_0005 frame5_8 : 0005_0005_0005_0005 frame5_9 : 0005_0005_0005_0005 frame5_10: 0005_0005_0005_0005 frame5_11: 0005_0005_0005_0005 frame5_12: 0005_0005_0005_0005 frame5_13: 0005_0005_0005_0005 frame5_14: 0005_0005_0005_0005 frame5_15: 0005_0005_0005_0005 frame5_16: 0005_0005_0005_0005 frame5_17: 0005_0005_0005_0005 frame5_18: 0005_0005_0005_0005 frame5_19: 0005_0005_0005_0005 frame5_20: 0005_0005_0005_0005 frame5_21: 0005_0005_0005_0005 frame5_22: ec05_6eb5_a405_0005 - 可以得出以下结论,1每帧间用"fd 07 07 07 …"填充最少12Byte,根据payload长度(自适应动态调整)07个数,最终把整帧凑成8的整数倍数

- 如payload =63,XGMII_frame = fd + 07*14 + df55_5555_5555_55fb + 长度/类型 + payload + FCS = 104 ,104/8 = 13;

- 如payload =64,XGMII_frame = fd + 07*13 + df55_5555_5555_55fb + 长度/类型 + payload + FCS = 104 ,104/8 = 13;

- 如payload =65,XGMII_frame = fd + 07*12 + df55_5555_5555_55fb + 长度/类型 + payload + FCS = 104 ,104/8 = 13;

- 如payload =66,XGMII_frame = fd + 07*11 + df55_5555_5555_55fb + 长度/类型 + payload + FCS = 104 ,104/8 = 13;

- 如payload =67,XGMII_frame = fd + 07*14 + df55_5555_5555_55fb + 长度/类型 + payload + FCS = 108 ,连发两次216可被8整除;

- 如payload =68,XGMII_frame = fd + 07*13 + df55_5555_5555_55fb + 长度/类型 + payload + FCS = 108 ,连发两次216可被8整除;

- 如payload =69,XGMII_frame = fd + 07*12 + df55_5555_5555_55fb + 长度/类型 + payload + FCS = 108 ,连发两次216可被8整除;

- 如payload =70,XGMII_frame = fd + 07*11 + df55_5555_5555_55fb + 长度/类型 + payload + FCS = 108 ,连发两次216可被8整除;

- 如payload =71,XGMII_frame = fd + 07*14 + df55_5555_5555_55fb + 长度/类型 + payload + FCS = 112,112/8 = 14;

- 如此反复循环

- 前导码(7Byte)+ 帧开始符(1Byte)为“”df55_5555_5555_55fb“

- FCS加在frame结尾(CRC)

- 数据流

- 进MAC层前,格式为目标地址+源地址+类型/长度+playload,通过axi_stream进入MAC层(不可被8整除时用Keep补齐)

- MAC做了以下工作

- 剔除axi_stream中的无效数据

- 根据XGMII协议补充间隔符、前导码、FCS

- 最终生成复合MGMII协议格式的数据

- 发送效率

三、PHY(PCS/PMA)

- 该层位于OSI模型的第一层即PHY层,PHY层与MAC(MAC时OSI模型第二层)层相连

- PHY(第一层)进一步划分为物理介质层(PMD),物理中间层(PMA)和物理编码子层(PCS),例如:光纤收发机属于PMD

-

- XGMII interface

- 传输路径,包括 64b/66b encoder, 加扰器, Gearbox

- 接收路行,包括包括块同步、解扰器、译码器和BER(Bit Error Rate)监视器

- 接收数据路径中的弹性缓冲区

- Test pattern generation and checking

- 光学串行接口

- Management registers (PCS/PMA) with optional MDIO interface

- 与 MAC 相连时 mdio_tri 不需要连接

-

- 相比于10GBASE_R,KR在传输和接收通道上增加了FEC(前向纠错), AN(自主协商)

四、MDIO

-

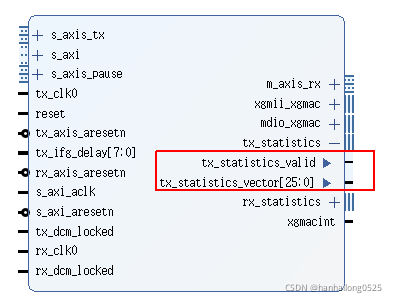

MDIO interface 为 MAC core 提供 PCS/PMA core 的控制通道,MAC core 框图如下:

-

PCS/PMA core MDIO 接口如下表所示

-

Signal Name Direction Description mdc I Management clock mdio_in I MDIO Input mdio_out O MDIO Output mdio_tri O MDIO 3-state control.1 disconnects the output driver from the MDIO bus. prtad[4:0] I MDIO port address. When multiple MDIO-managed ports appear on the same bus, this input can be used to set the address of each port. -

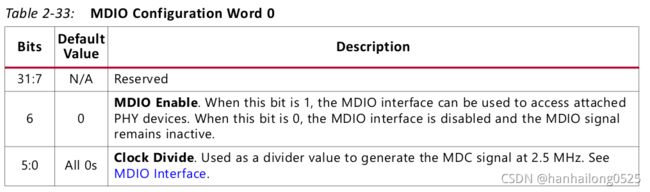

- 其中 fHOST_CLK = 156.25MHz

- fMDC 频率不可超过2.5MHz

- 例如:Clock Divide[5:0] = 39,通过上式计算fMDC约为1.95MHz

-

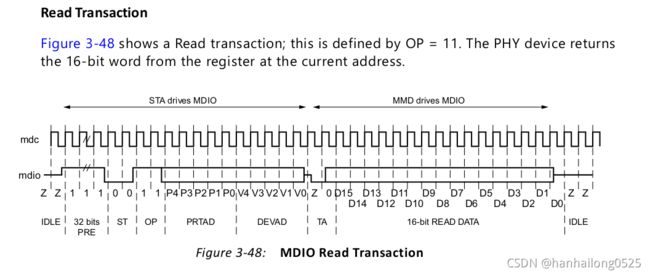

* 上图中的PRTAD、 DEVAD由 MAC core reg “MDIO configuration Word1”根据实际情况下发的。

* parad[4:0],由 PCS/PMA core 引用出可由逻辑层配置

* DEVAD(device address),当操作PMA时该值为5‘b0_0001,当操作PCS时该值为5‘b0_0011。此地址对应PCS/PMA MDIO Registers Address X.YYYYY中的X,例如 “MDIO Register 1.0: PMA/PMD Control 1” 的Registers Address的地址为1.0,则DEVAD的值为5‘b0_0001。

* 上图中的OP也是由MAC core reg “MDIO configuration Word1”根据实际情况下发的。

* 配置地址时OP=2‘b00;

* 写时OP=2‘b01;

* 读时OP=2‘b11;

* 上图中的ST表示START,值为2‘b00

- 例1,MAC core 通过MDIO 向 PCS/PMA写数据

-

1).通过使能 MAC core 的 “MDIO Configuration Word 0”寄存器 “MDIO Enable”和“CLK Divide”

-

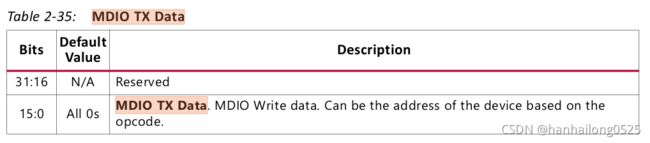

- 向 MDIO TX Date寄存器写入欲操作的PCS/PMA core寄存器的地址

- 注意这里的地址为PCS/PMA core reg addr 中的 X.YYYYY,中的Y

- 配置“MDIO Configuration Word 1”中的 DEVAD,PRTAD,OP(00)

- 等待(读取)“MDIO Configuration Word 1”的bit7变为0

- 将 欲写入 PCS/PMA core寄存器 的数据写入 MAC core的寄存器MDIO TX Date。

- 配置“MDIO Configuration Word 1”中的 DEVAD,PRTAD,OP(01)

- 等待(读取)“MDIO Configuration Word 1”的bit7变为0

- 向 MDIO TX Date寄存器写入欲操作的PCS/PMA core寄存器的地址

-

- 例2,MAC core 通过MDIO 从 PCS/PMA读数据

五、各种长度专题

- payload_size

-

pkg_length

-

packet_count

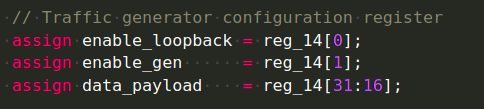

- 由Microblaze通过axi_lite配置eth_axi_stream_gen_mon的reg_1C实现

- 仿真时没有用到,实际跑时可以关注下

-

frame_length

-

frame_count