ICC学习——LAB2

ICC学习——LAB2设计规划

学习目标:

1.定义核心和放置的行结构

2.定义信号,PG,corner pad的位置

3.插入filler pad cell

4.手动放置macro

5.应用宏放置约束

6.使用虚拟平面放置(VF)放置宏和标准单元

7.分析拥塞

8.在macro周围创建PG ring

9.使用PNS(power network synthesis)完成P/G ring和straps

10.使用PNA(power network Analysis)分析IR drop

11.分析时序

导入:本实验的目的是让你对ICC的设计规划功能更加熟悉。对于这个实验,将使用一个稍大一点的ORCA版本,他是处于芯片级,包括IO pad以及更加宏单元。这使得设计阶段阶段更加有趣。

答案和解决方案:

本实验后有一个“答案/解决方案”部分。鼓励经常参阅此部分,验证答案,或在执行某些步骤时获得帮助。

相关文件和目录:

此实验的所有文件位于目录下的lab2_dp目录中

lab2/dp

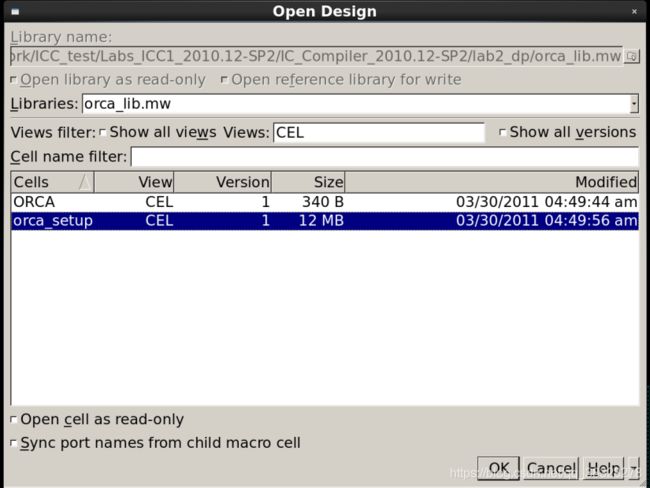

orca_lib.mw/CEL

orca_setup:数据设置后的ORCA设计,并以MIlkyWay的格式保存。

design_data/ 包含ORCA设计输入数据

ORCA_2.v 第二次通过verilog网表

ORCA_2.sdc 第二次通过sdc时序约束

scripts/ 包含各种各样的布图规划脚本

zns_pass_setup.tcl 执行第二遍数据设置脚本

connect_pg.tcl 以逻辑方式将所有pg pin连接到网络

insert_pad_filler.tcl 插入pad填充单元

keepout.tcl 禁止放置所有的宏

macro_place_cons.tcl 宏放置约束

macro_pg_ring.tcl 宏组周围创建pg ring

opt_ctrl.tcl 时序和优化控制

pad_cell_cons.tcl 定义pad单元位置

pns.tcl 电源网络约束/综合

prepare_macros.tcl 将三个宏连接到IO pad

如果遇到问题或者卡住了,可以使用完整的命令脚本去恢复

.solution/run.tcl

Task1 载入设计

1.切换到lab2_dp目录,启用ICC GUI模式

cd lab2_dp

icc_shell -gui

2.打开orca_lib.mw设计库中的orca_setup单元

Note:这个单元已经通过“data_setup”

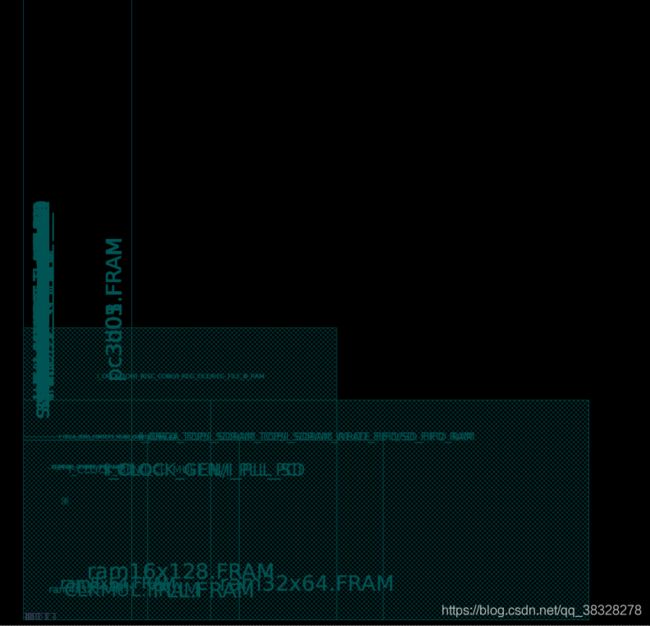

3.查看layout 窗口,大的蓝绿色矩形是宏和IO pad单元,左小角的小紫色矩形是标准单元(先看的更清楚可以放大)。所有的这些单元都是网表中实例单元。堆叠在原点(0,0)。

4.应用在./scripts/opt_ctrl.tcl的时序和优化控制

Note:大多数设置都在单元1附录被讨论,有些在后面单元被讨论。不需要花时间理解。

source scripts/opt_ctrl.tcl

5.通过选择以下选项切换到layout窗口中“Design Planning”任务菜单

File —> Task —> Design Planning

Task2 初始布局规划

1.来自综合的网表不包含物理单元,例如电源和地的pad cell或者corner pad cell。因此必须先创建这些额外的单元,然后才能将他们实际位置放在芯片外围区域。

创建corner cell和pg cell,并且使用一个提供的脚本定义所有pad cell的位置:

提示:键入时,使用[Tab]键完成命令/选项/文件

source -echo scripts/pad_cell_cons.tcl

查看日志(log文件)输出,以验证这些单元是否已创建并受到约束。没有任何错误或者警告信息。

在一个单独的UNIX窗口中,查看上面的脚本回答以下问题。

问题1:使用参考单元pvdi创建一个名为VDD_TEST的pad cell

回答:

问题2:哪个边用于定义右上角corner cell的位置

回答:

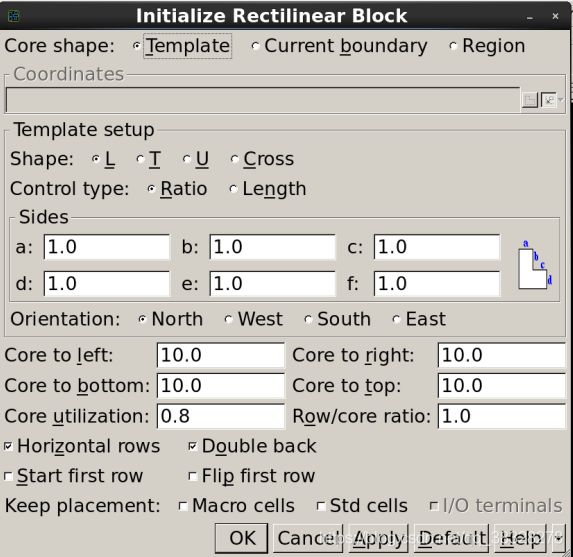

2.初始化布局规划

菜单选择 Floorplan —> Initialize Floorplan

将核心利用率改为0.8(80%)

将核到左,右,底,上距离设置成30

点击OK

3.在layout窗口按压[F],查看芯片核心和外围区域。芯片外延上边缘的蓝色散列标记矩形是未放置的宏单元。右边的紫色对象是标准单元。

Note:角单元很容易看到,占据整个layout的蓝色大正方形(label为pfrelr),每次有四组四个PG pad。

4.放大芯片外围区域,注意所有pad之间距离大致相等。

问题3:pad的间距总是相等的吗?请解释

不是。如果tdf文件中定义的某些pad包含“偏移”值,则在剩余焊盘在剩余空间中均匀分布之前,首先满足偏移(相对于底部或左芯边缘)。如果不使用偏移量,则所有pad将尽可能靠近相等的位置展开。

5.插入pad filler以填充pad之间的间隙。

取决于所使用工艺和库,这可能是NP阱或PG pad ring连续性所需的。

若将所需的pad filler数量保持最小,请在列表中首先指定较大的填充单元。否则一个1000微米的空间将被200个5um宽的单元填充,而不是一个l000微米宽的单元。source提供的脚本:

source scripts/insert_pad_filler.tcl

![]()

6.放大两个pad单元之间的区域,观察插入的filler cell

7.通过执行以下的脚本,在PG信号和IO pad,宏,标准单元的PG pin之间建立逻辑连接(无物理布线)

source -echo scripts/connect_pg.tcl

8.构建pad区域电源环

create_pad_rings

放大pad之间的区域,可以看到在filler cell上方添加了金属线,连接每个pad cell内的电源线,从而形成连续的PG pad ring。

9.将设计另存为“floorplan_init”:

save_mw_cel -as floorplab_init

Task3 预置连接到IO pad的宏

在此任务中,将要识别连接到IO pad 单元的宏,并手动地将他们放置在核区域,以便他们与IO pad地连接尽可能短。

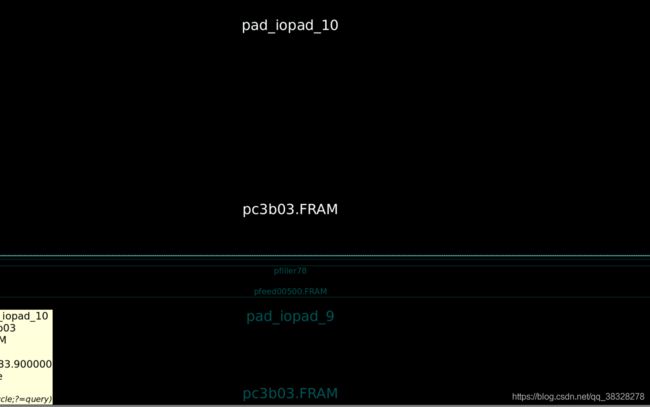

1.放大查看如图1顶部外围区域

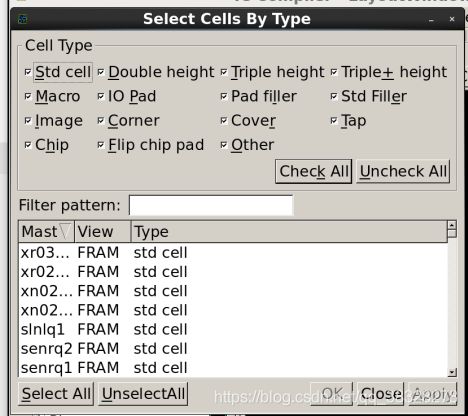

2.识别连接到IO pad的宏,如下所示:

选择 Select —> Cells —> By Types

点击对话框顶部(单元类型)区域中的“Uncheck All”按钮

点击OK

注意到所有的宏都被选择——白色高亮

从layout窗口顶部选择“Flyline”按钮

在窗口右侧出现“show flylines面板中,点击下拉擦弹并选择“Selected to IO”和“应用”将亮度降低到50%或更低。以便可以更好地看到三条飞线(flyline)。左下方的三个宏显示了与顶部IO相连

3.保持“show flylines”面板打开。如果需要调整查看区域(平移或缩放)以查看下面的图片。如果不小心取消选择宏,飞线消失,使用[Ctrl]键重新选择此外显示的三个带有圆圈的宏,飞线重新出现。

4.与IO pad直接相连的三个宏的名字为

I_CLOCK_GEN/I_PLL_PCI

I_CLOCK_GEN/I_PLL_SD

I_CLOCK_GEN/I_CLKMUL

将鼠标悬停在单元上,可以左下角查看信息,此设计有两个PLL应朝向芯片的左上角和右上角放置,以便各自靠近各自的时钟PAD

问题4:这些PLLs连接到那几个IO pad?

回答

5.现在手动2将I_PLL_PCI宏(连接到左边的pad)移动到核心区域。请注意你可以使用撤销按钮来回溯操作。

a.使用选择工具,只选择I_PLL_PCI

b.选择移动调整工具,(在窗口左侧),开始移动操作。

将I_PLL_PCI宏单元拖到核心区域的左上角。给核心边缘留一点位置。

c.在PLL仍被选择的情况下,使用对齐功能将PLL与核的上边缘左边缘对齐。

点击“Align Objects to Left”按钮。Align Objects:对齐对象。将其与核的左边缘对齐。

从下拉菜单中选择"Align Objects to Top",将它与核的上边缘对齐

现在PLL与核边缘对其了

d为了确保单元不会因为虚拟平台布局而移动,清单击“pad lock”按钮将其锁住。你应该看到一个x穿过单元。这可以通过下列的脚本替代:

set_dont_touch_placement

6.尝试移动固定的I_PLL_PCI宏。你应该无法做到。如果你可以移动它,请使用“Undo”(撤销)按钮将其放回原处,并固定他。如果你犯错了,请不要担心,因为后面的步骤将提供一个脚本,可以用来将这些宏放置在预期的坐标处。根据需要使用[ESC]键将光标返回到选择模式。

7.在接下来的步骤里,您将重复以上步骤,将其它的两个宏移动到核区域,并靠近各自的IO pad单元。不要花费太多时间进行完美放置,下一步的脚本将确保正确放置。

点击“I_PLL_SD”选中它

选择移动调整工具,并将他拖到核区域的右上角,将其与上边缘,右边缘对齐。

旋转180°,以减少线长。

选中并拖动I_CLKMUL到I_PLL_SD的左边,将其与上边缘对齐。

对旋转菜单中选择Y轴(Y-axis)沿y轴方向镜像(沿y轴翻转),以减少导线长度。

要将I_CLKMUL和I_PLL_SD隔开10微米:

按住[Ctrl]键,同时选中I_CLKMUL和I_PLL_SD。指定一个分布偏移(distribution offset)为10,选中“distribution objects to right”

锁定I_CLKMUL宏

单击小“x”关闭飞线面板。

当三个宏被选中时,您应该看到每个宏有一个“x”,剩余的宏将在稍后的eVF放置过程中与标准单元同时放置。

8.要确保标准单元按照预期放置,可以source以下脚本

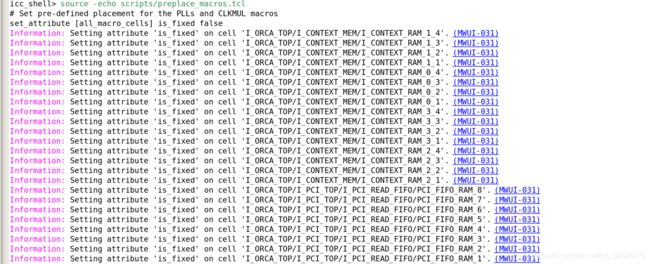

source -echo scripts/preplace_macros.tcl

Task4 进行虚拟平面布局

通常在执行虚拟平面布局之前,应定义任何已知的宏布局约束和硬/软布局blockage。我们最初将跳过这些步骤,以便观察“默认”VF布局行为。第一次布局后,应用以上约束,并再次进行VF(virtual flat)放置。你会注意到明显的不同。

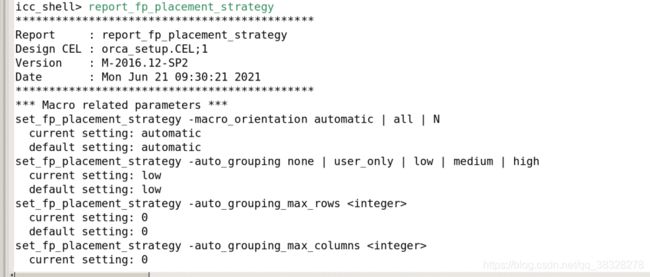

1.验证当前VF布局策略选项有默认设置

report_fp_placement_strategy

2.为防止标准单元被放置在宏之间的窄通道(<10um)中,将sliver size设置成10

set_fp_placement_strategy -sliver_size 10

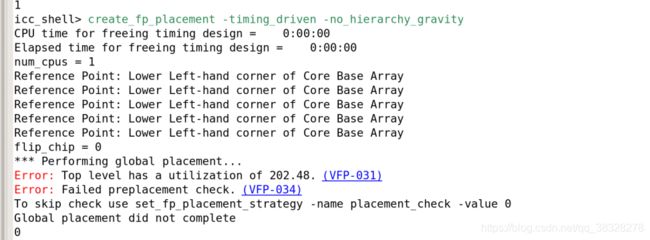

3.使用“no hierarchy gravity”执行时序驱动的VF布局i。

(以确保“逻辑层次”不会影响此非层次或平面布局的位置)

create_fp_placement -timing_driven -no_hierarchy_gravity

4.检查全局布线拥塞图(global route congestion map)

点击“Global route congestion map”按钮

点击弹出面板的“Reload”按钮

一个对话框出现,其中主要包含拥塞执行分析的命令

report_congestion -grc_based -by_layer -routing_stage global

如果在日志中向上滚动到拥塞分析输出的开头,将收到一条关于“未固定”宏的错误信息(PSYN-348).你完全可以忽略这一点。你可以在拥塞分析前固定所有宏位置,以避免PSYN-348的错误。但是,您将再运行create_fp_placement,再次调整宏布局,所以你不用固定宏位置。

你不应该有拥塞问题。有溢出的GRC,但它们分散在核心区域。

6.点击右上角的小“x”,关闭右侧的“global route congestion”面板

7.如果我们将宏转换成数组,那么设计的电源/地straps布线和宏ring变得更容易。source以下的脚本以应用宏放置约束来实现以下目标。

①将芯片尽可能放置在芯片边缘位置

②将宏尽可能组合起来

③打开虚拟IPO以模拟时序优化(并防止不必要的布局优化)

④限制某些RAM的合法布局方向

source -echo scripts/macro_place_cons.tcl

8.仔细检查你的设置。建议:使用ICCshell窗口中的向上箭头

仔细查找并重新执行“strategy”命令

report_fp_placement_strategy

report_fp_macro_options

9.source以下脚本在所有宏周围设置10um的硬禁止边距,这将更容易在宏周围创建PG ring,并避免拥塞和宏周围的布线DRC:

source -echo scripts/keepout.tcl

10.再次运行VF placer之前,最后看看宏设置

create_fp_placement -timing_driven -no_hierarchy -gravity

注意:请注意宏位置是非常不同的,许多类似的宏“分组”,除了手动放置的,这是固定到位的。

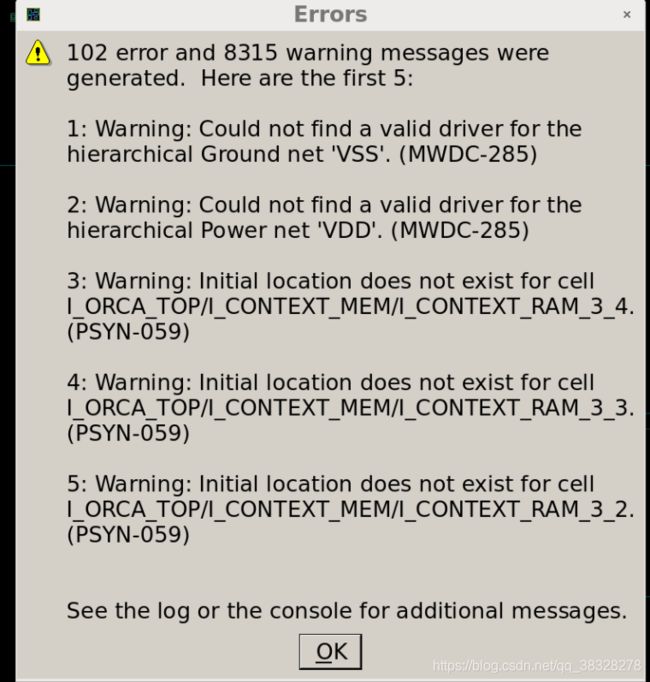

11.再次分析全局布线拥塞图,点击“Reload—>OK”以更新拥塞图。GUI会出现一个“ERRORS”框,单击确定。(类似于步骤5)

不应该有任何拥塞问题

点击小“x”关闭右侧的分析面板

12.锁定所有宏

set_dont_touch_placement [all_macro_cells]

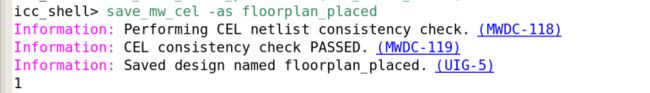

save_mw_cel -as floorplan_placed

Task5 在宏周围创建PG ring

在接下来的任务里,将使用电源网络综合(PNS)自动创建PG核和单个宏环,以及垂直和水平straps。如果你想在宏组周围创建环,这是在PNS之前做的,这就是此任务要完成的。

1.我们1已经创建了一个脚本来围绕六祖宏创建PG ring。查看位于./scripts/macro_pg_rings.tcl的文件。创建PG环的方法是:

①定义包含一组宏的粗糙区域

②定义块环层,宽度和偏移

③创建金属布线

2.执行脚本

source ./scripts/macro_pg_rings.tcl

3.查看已经创建的ring

请注意左上角“PLL”宏是唯一一个周围没有PG环的宏,这将由PNS完成。

还要注意的是,除了宏周围的环意外,宏之间还要有垂直和水平的strap。这是create_fg_group_block_ring命令的一个很好的特征(意味着这个命令可以生成strap)。如果愿意的话,使用-skip_strap选项禁用它。

Task6 PNS(Power Network Synthesis)

电源“grid”需要完成。你可以创建PGstrap,为核中心,核环核单个宏周围ring手动。(类似于上个任务中创建宏组环的方式,但这样做需要估计strap的数量核宽度,以及核心环的宽度,以达到可接受的低IR drop),相反,你可以使用ICC自带的PNS功能,根据目标IR drop自动确定strap数量和宽度,以及核ring宽度。您可以尝试不同目标,当达到可接受结果时,就可以提交或实际实现power grid。

如果你的时间不够,可以source scripts/pns.tcl执行步骤1—5,如果使用此脚本跳过步骤6-7。

~~跳过

8.单击commit按钮,或键入以下命令,生成建议的电源plan

commit_fp_rail

如果对话框仍打开,取笑它。

9.放大芯片,查看所有的PG strap和ring如何创建的。

请注意宏和周围的power ring无连接

还要注意,标准单元放置行上没有PG rail

10.为了完成电源规划,我们需要连接所有宏上的电源管脚(pin),并创建标准单元电源rail。执行以下命令完成此操作:

preroute_instances

preroute_standard_cells -fill_empty_rows -remove_floating_pieces

注意:因为我们使用“-remove_floating_pieces”选项,因此预期会出现“floating rail segments removed“的警告

11.放大并观察METAL1上的宏,引脚连接和蓝色PG rail

12.使用Preroute—>Analyze power Network分析已经完成的电源规划

为电源接地网络(VDD,VSS),电源预算(budget)(350mW),电源电压(1.32V)和指定的pad master(pvoi pvdi)输入以前用于PSN的相同值,然后按OK

你将看到另一个热图(heat map)

问题8:最终报告的VDD/VSS IR最大下降两是多少?

回答:

问题9:你可以解释为什么最终的IR drop更小?

回答:

13.点击右边的小”x“关闭PNA电压降。

14.保存cell

save_mw_cel -as floorplan_pns

Task7 检查时序

现在电源规划已经完成。您需要执行更多步骤来完成布局并验证最大延迟时序。(建立时间时序)

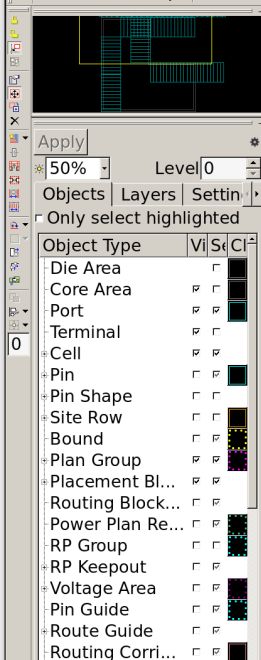

1.如果在layout窗口看不到标准单元,请转到layout窗口左侧”可见性面板“,通过选择”+“展开”cell“列表,并确保选中标准。

2.PNS在METAL4和METAL5上创建了许多strap。这些strap被放置在标准单元上,它可以有利于防止标准单元放置在strap下,这降低了沿带(strap)拥塞的可能性,并减少了电源网络的串扰影响。在strap上应用一个”完成“的电源网络阻塞,然后再次余小宁虚拟平面布局以考虑pnet的设置。

set_pnet_options -complete "METAL4 METAL5"

create_fp_placement -timing_driven -no_hierarcgy_gravity

验证strap下不再有任何标准单元。

3.因为要检查时序,通过执行以下命令全局布线。

route_zrt_global

4.打开global route congestion map(无需重新加载)

不应该有任何拥塞问题。并关闭面板(点击小”x“)

5.使用view程序生成一个最大延迟时序报告(建立时间)。

v report_timing

使用搜索机制,或者标记单词slack:RE search —>type in (键入)”slack“ —> Tag.向上向下滚动。

在8个时钟组路径中的每个路径末尾,您应该可以看到单词slack(MET)后跟一个正数。这种设计满足建立时间,点击Close search,然后关闭窗口。

问题10:你可以在不执行全局布线的情况下分析时序吗?如果可以,你应该吗?

回答:

6.为了修复一些时序违规(timing violation)(和设计规则冲突),如果有,您将调用以下命令并重复全局布线。如果您有时间,请随时那么做,否则条道”保存单元步骤“

optimize_fp_timing -fix_design_rule

最后一次重复全局布线,拥塞分析和时序分析,设计不应有任何阻塞问题或时序问题。

7.将cell保存为floorplan_complete

Task8 写出DEF floorplan文件

1.删除所有放置的标准单元,然后以DEF格式写出Floorplan文件。DEF floorplan文件将被Design Complier Toporgraphical,用于使用你刚设计的floorplan重新综合设计,并且在读取重新综合网表时,ICC将再次使用DEF floorplan文件,重新创建floorplan(下个任务)

2.验证DEF文件已被创建在design_data目录

3.关闭设计库,而不将设计保存在内存里。

File —> Close Library —>Discard All

Task9 创建第二次通过设计以备布局

我们现在假设这个设计是使用DC Toporgraphical mode从RTL代码重新综合的。以及在上一个任务中生成的DEF文件中捕获的floorplan买哦书。你已经获得了第二次通过的网表ORCA_2.v以及更新的约束文件ORCA_2.sdc

1.使用新的ORCA网表和约束进行数据设置

source scripts/2nd_pass_setup.tcl

使用此脚本执行以下标准数据设置步骤

2.读入之前任务中写出的DEF文件

read_def design_data/ORCA.def

Note:现在,你将要看到的与之前任务中设计相同floorplan

3.重新应用在任务6,step1中的DNS后的pnet选项。DEF文件未捕获这些设置。

set_pnet_options -complete "METAL4 METAL5"

4.保存cell作为ready_for_placement

5.退出ICC

至此已经完成Design Planning实验。