XDMA IP学习2——细节补充+问题记录

上一篇XDMA学习的blog:粗略介绍了XDMA IP

XDMA IP学习![]() http://t.csdn.cn/XAfqV这篇补充一些细节和问题记录。先占个坑,持续更新中。。。

http://t.csdn.cn/XAfqV这篇补充一些细节和问题记录。先占个坑,持续更新中。。。

1.XDMA的DMA流程

下图是XDMA的一个典型的应用,XDMA采集卡作为Endpoint,通过PCIe与上位机通信。FPGA利用DDR等存储资源做数据缓存,XDMA的DMA controller 将数据在上位机内存与FPGA内搬运。

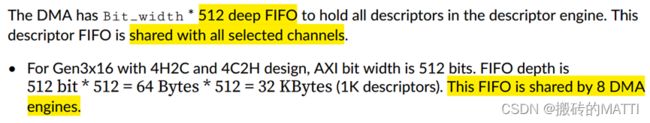

如下图的流程图所示:每次传输上位机需要先在内存中申请好数据存放的Buffers,接着根据Buffer生成Descriptors,Descriptors内包含Buffers的地址长度等信息,接着将第一个Descriptor的内存地址以及next adjacent descriptor count写入XDMA的配置寄存器中,最后控制XDMA配置寄存器,启动XDMA中的DMA引擎进行数据搬运。

在逻辑中,XDMA的DMA引擎先通过第一个Descriptor的地址和next adjacent descriptor count从内存中获取Descriptors,获取的descriptors上有后续descriptors的地址和数量信息。当获取到最后一个Descriptor后停止获取。在获取Descriptors的同时,DMA会解析Descriptors上的buffer地址的信息,将数据从FPGA与内存buffer之间搬运。

2.Descriptors

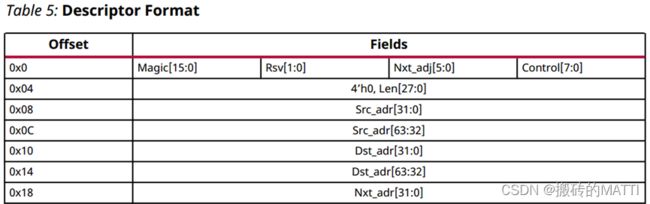

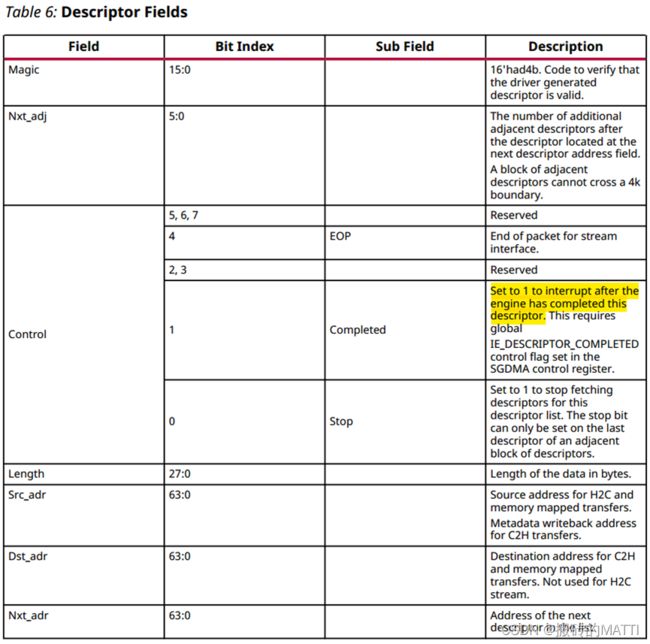

Descriptor上定义了PCIe传输的源地址,目的地址以及DMA长度。Descriptors由驱动产生并存放于上位机内存中。每一个H2C/C2H channal都有自己的descriptor list,descriptor上描述了下一个descriptor的地址,DMA engine 会一直获取直到最后一个descriptor,descriptor存放的时候必须满足32字节对齐。

注:

Nxt_adj代表当前descriptor的下一个descriptor所在的descriptor group还剩的descriptors的数量。

EOP:descriptor里面的EOP位为H2C时,用于表征当前descriptor所代表的数据为end of packet;C2H时,EOP由用户侧stream通道的tlast来决定,tlast会在writeback寄存器上写下eop标志供Host查询。

Completed: 置位之后,XDMA会在完成当前descriptor数据的搬运之后会产生DMA中断给到HOST。

3.Poll Mode

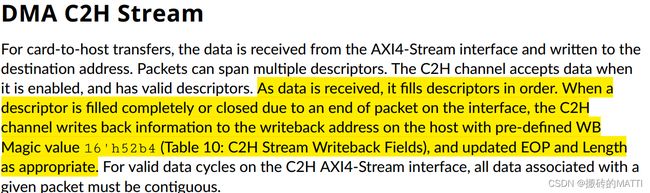

DMA C2H每次传输完一个complete bit置位后的descriptor之后会更新wirte back寄存器信息(每个descriptor实际传输的长度),传统模式下, 当中断或者是因为EOP结束descriptor,驱动可以去查询write back寄存器内各个descriptor length,eop等信息。

当Poll Mode开启后,会新增一个write back信息,如下:

当一个complete bit置位的descriptor完成后,DMA会write back当前已经完成的descriptors的数量,这样驱动可以不用采用中断的方式,而是采用轮询的方式,polling该write back信息。

4.EOP

EOP表征一个数据包的结束,与XDMA的用户接口AXI-MM和AXI-ST的tlast对应。

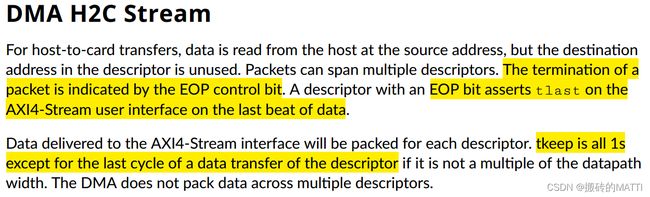

对于H2C,通过在descriptor上的eop位置1后,当DMA传输完成后改descriptor所代表的数据后,将tlast置位。

对于C2H,Tlast信号会触发eop标志,同时会结束当前descriptor(若该descriptor数据传输完成了一部分,下个packet数据开始传输是从下一个descriptor开始)

5.Stream通道4032 BUG

使用过程中发生过上位机查询到writeback信息里面有的descriptor收到的数据为4032B(实际descriptor为4KB),显示接收数据长度有问题,但实际观察接收到的数据不一定丢失。

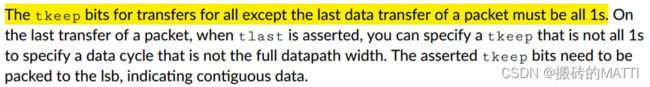

问题原因:XDMA用户侧的Stream数据中的tkeep信号只有在tlast为1的时候才可能不全为1,其他tvalid有效的时间内必须全为1。

当时使用的时候由于考虑到tlast会提前结束当前descriptor的特性,所以把tlast未连接,导致在正常一个packet结束的时候tkeep出现了不全为1的情况,导致XDMA IP内部传输或writeback信息出错。

6.地址映射

XDMA用户侧的AXI地址如何对应到上位机中的地址?

Xilinx_Answer_65062_AXI_PCIe_Address_Mapping:

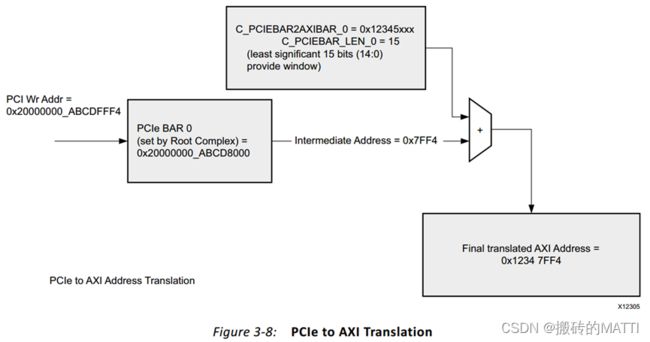

AXI to PCIe以及PCIe to AXI地址转化如下图,AXIBAR地址经过C_AXIBAR2PCIEBAR的偏移转换为PCIe Address,再经过bar空间路由到对应的设备;反过来,PCIe地址通过BAR得到对应设备的PCIe地址的偏移(intermediate addr),该偏移地址经过C_PCIEBAR2AXIBAR转化为实际的AXI地址。

下图中的PCIeBAR2AXIBAR地址写错了。

Descriptor里面的Src_adr以及Dst_adr描述的只用提供上位机的地址,XDMA设备的PCIe源地址不明,可能是IP内固定的,或者是PCIe设备地址分配的时候分配好了,这块暂时未找到相关资料。