ZYNQ-7000概述

摘要

Xilinx推出的ZYNQ-7000被称为全可编程片上系统(SOC),它由FPGA与ARM组合构成,硬件可编程,软件也可编程,在众多应用场合有一定优势。本文根据Xilinx官网的介绍并结合ZYNQ-7000的多份数据手册总结了此产品的一些基本信息,包括产品简介、资源概览、速度等级、温度等级、命名规则、架构概览等,为大家入门ZYNQ提供帮助。

关键词:ZYNQ;SOC;PL;PS;片上系统

一. SOC简介

参考:Xilinx自适应SOC简介

SOC:System On Chip,也称为All Programmable SOC,称为全可编程片上系统.。.

Xilinx的SOC有4个系列:

- ZYNQ-7000,此系列是Xilinx于2015年发布的第一代SOC架构的芯片,也是世界上首个SOC芯片系列

- ZYNQ UltraScale+ MPSoC,性能强劲

- ZYNQ UltraScale+ RDSoC,性能强劲

- Versal ACAP,Xilinx最新发布的芯片,性能也最强

SOC内部集成了单/多个ARM处理器核心与1个FPGA,将软件可编程的硬核处理器与硬件可编程的FPGA集成在一个芯片中。软硬件均可编程也是SOC被称为全可编程片上系统的原因。

SOC中的ARM处理器被称为PS(Processing System,处理系统),而FPGA被称为PL(Progarmmable Logic,可编程逻辑)。SOC = PS + PL,其中,PS为主,与单独的ARM芯片(如ST公司的STM32系列)一样,PS配备了多个外设,如串口,CAN口,GPIO等,PL部分可以看做是PS的一个"可编程外设"。

有人也许有疑问,既然SOC = PS + PL,那么用一个ARM芯片和一个FPGA组合的方式,不考虑面积成本等问题,在性能方面是不是就和SOC一样了呢?答案是不行,因为在同一芯片中,ZYNQ中PS与PL可进行低延时高速片内通信,而两个芯片间的片间通信就难以实现低延时和高速,这是SOC的主要优势之一。

SOC的优点:1.灵活,2.成本低(一个芯片比两个芯片便宜)

SOC的缺点:1.开发难度大,开发人员最好同时会FPGA和ARM

二. ZYNQ-7000系列产品简介

参考:Xilinx ZYNQ-7000产品简介与技术文档

2.1 7000S与7000的区别

ZYNQ-7000 SOC分为ZYNQ-7000S 与 ZYNQ-7000两类产品,7000S中的S是Single(单个)的缩写,指的是7000S芯片中只集成了一个A9核,而7000是两个。

2.2 资源概览

参考:ZYNQ-7000产品选型手册.pdf

可见7000系列芯片不同型号间的主要区别在于:1.处理器核心数,2.处理器主频,3.PL资源,而外设没区别。

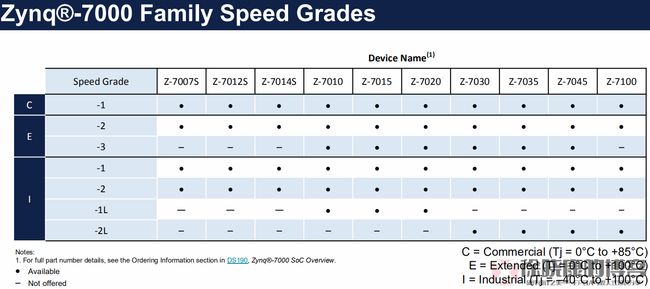

2.3 速度等级与温度等级

可见,速度等级共分3级,-1最慢,-2中等,-3最快。带L表示Low Power(低功耗)

温度等级共分3级:

-

C,Commerical,商业级,0~85℃

-

E,Extended,扩展级,0~100℃

-

I,Industrial,工业级,-40~+100℃

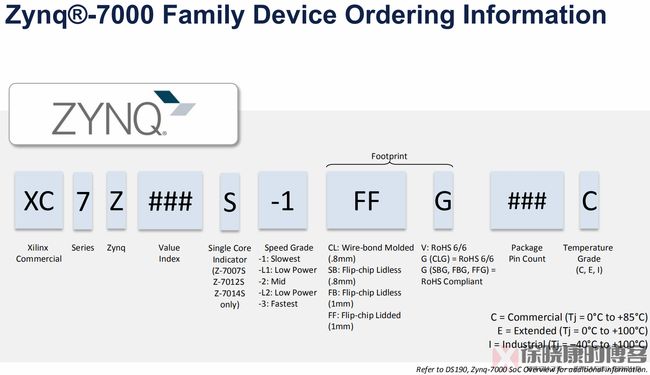

2.4 芯片命名规则

如 XC7Z020-2CLG484I,表示芯片是ZYNQ-7020,速度等级-2,封装CLG484的工业级芯片。

三. ZYNQ-7000数据手册:概览

参考:ds190 ZYNQ-7000-概览.pdf

3.1 ZYNQ-7000描述

Zynq-7000系列基于Xilinx的第一代SoC架构。这些产品在单个设备中集成了功能丰富的基于双核或单核ARM Cortex-A9的处理系统(PS)和28nm Xilinx可编程逻辑(PL)。ARM Cortex-A9 CPU是PS的核心,此外还包括片上存储器,外部存储器接口以及丰富的外围接口。

Zynq-7000系列提供了FPGA的灵活性和可扩展性,同时提供了与通常使用的ASIC(Application Specific Integrated Circuit,专用集成电路)和ASSP(Application Specific Standard Parts,专用标准产品)同等的性能,功率和易用性。同时, Zynq-7000系列提供了行业标准设计工具(Vivado,SDK,Vitis等),使设计人员可以使用单一平台开发成本敏感以及高性能的应用程序。 Zynq-7000系列中的每个设备都包含相同的PS,但是PL和IO资源在设备之间会有所不同。因此,Zynq-7000和Zynq-7000S SoC能够满足多种应用场景.

Zynq-7000集成了PS与PL,在PL中实现自定义逻辑,在PS中实现自定义软件,两者组合实现多种功能。两芯片的解决方案(FPGA + ASSP)因为I / O带宽,延迟和功耗的原因,无法达到同等性能水平。

Xilinx为Zynq-7000系列提供了大量的软IP。 基于ARM的PS还结合了Xilinx现有的PL生态系统,带来了广泛的第三方工具和IP提供商。

PS和PL可独立工作,也可以在PS上跑操作系统,例如Linux。Xilinx也提供其它标准操作系统。

PS和PL位于单独的电源域上,当不使用PL时可关闭PL电源。 PS中的处理器始终首先启动,从而允许以软件为中心的方法对PL进行配置。 对PL的配置由CPU上运行的软件管理,因此ZYNQ的启动类似于ASSP。

3.2 ZYNQ-7000架构概览

如上图所示,PS包含四大块:

- Application processor unit (APU),应用处理器单元

- Memory interfaces,存储器接口

- I/O peripherals (IOP),输入/输出外设

- Interconnect,内部互联

注意:ZYNQ-7000系列芯片的PS架构均相同。

四. PS侧架构解析

4.1 APU(应用处理器单元)

APU包括:

- 单/两个A9核,7000S的APU只有单核,缺少上图右上角虚线框部分

- SWDT(System Watch Dog Timer,系统看门狗定时器)

- TTC(Triple Timer/Counter,3重定时器/计数器)

- System-Level Control Regs(系统级控制寄存器)

- DMA 8 Channel(Direct Memory Access,8通道直接内存存储)

- GIC( General interrupt controller,一般中断控制器)

- Snoop Controller(窥探控制),AWDT(ARM Watch Dog Timer,ARM看门狗定时器),Timer(定时器)

- 512KB L2 Cache & Controller (Level 2 Cache,2级缓存与控制器)

- OCM Interconnect 256K SRAM(On-Chip Memory,256KB片上静态随机存储器)

每个A9核包括:

- FPU and NEON Engine(Float Point Unit,浮点运算单元 与 NEON?不知道是什么缩写,待查)

- MMU(Memory Management Unit,内存管理单元)

- A9 CPU(central processing unit,中央处理器)

- 32KB I-Cache(Instruction Cache,指令缓存)

- 32KB D-Cache(Date Cache,数据缓存)

4.2 Memory interfaces(存储器接口)

从上图可看到有两处存储器接口,左侧下边与右侧中部

左侧三种接口:

-

SRAM/NOR,SRAM接口

-

ONFI 1.0 NAND(Open Nand Flash Interface,开放与非闪存接口)

-

Q-SPI CTRL(Qual SPI控制,四通道SPI的FLASH接口)

这三种都是接FLASH等非易失存储器的。

右侧接易失存储器的DDR接口,支持DDR2/3,DDR3L,LPDDR2,

4.3 IOP(输入/输出外设)

Input/output peripherals,输入/输出外设,位于上图左侧,从上到下的外设分别是:

- 2路USB

- 2路GigE(Gigabit Ethernet,千兆以太网)

- 2路SD SDIO(SD卡接口SDIO,Secure Digital Input and Output,安全数字输入输出)

- GPIO(General Purpose Input Output,通用输入输出)

- 2路UART(Universal Asynchronous Receiver/Transmitter,通用异步收发器,简称串口)

- 2路CAN(Controller Area Network,控制器局域网)

- 2路I2C(Inter-Integrated Circuit Bus,Bus省略了,称为集成电路总线)

- 2路SPI(Serial Peripheral Interface,串行外设接口)

4.4 Interconnect(内部互联)

将处理器,存储器接口,外设等连起来。

五. PS与PL的接口

PS与PL间的通讯通过一些接口来进行,如下:

- AXI接口(见本人其它博客),PS与PL的高速通信口

- DMA中断

- EMIO(见本人其它博客)

- 时钟与复位,PS可以给PL提供时钟和复位信号

- Processor configuration access port (PCAP) ,处理器配置端口,PS可通过此端口配置PL

- XADC接口,Xilinx芯片上带的ADC

- JTAG,烧写程序与在线调试

六. 总结

本博文为ZYNQ的一些基础知识梳理,基本是参照Xilinx官网和芯片数据手册再加上自己的一些理解总结而来,如有疏漏,欢迎评论指出。

徐晓康的博客持续分享高质量硬件、FPGA与嵌入式知识,软件,工具等内容,欢迎大家关注。