Verilog中parameter使用

- 概述

- 模块定义

- 模块调用

- Questasim仿真

1.概述

Verilog中通过使用parameter可以在调用模块时修改模块里面的常数参数,提高模块的复用性,类似C语言中函数的形参,在模块调用时将参数传入模块。

2.模块定义

以简单的2选一电路为例,通过parameter配置输入参数的位宽进行说明:

2.1模块内定义

通过parameter配置输入位宽,默认为2bit:

module Mux2_1(in1,in2,sel,out);

parameter WIDTH=2;

input[WIDTH:1] in1;

input[WIDTH:1] in2;

input sel;

output[WIDTH:1] out;

assign out=sel?in1:in2;

endmodule

2.2模块外定义

module Mux2_1

#(parameter WIDTH=2)

(in1,in2,sel,out);

//parameter WIDTH=2;

input[WIDTH:1] in1;

input[WIDTH:1] in2;

input sel;

output[WIDTH:1] out;

assign out=sel?in1:in2;

endmodule

3.模块调用

3.1顶层模块调用修改参数

module ParaDemo(in1,in2,sel,out);

parameter WIDTH=4;

input[WIDTH:1] in1;

input[WIDTH:1] in2;

input sel;

output [WIDTH:1] out;

Mux2_1 #(WIDTH) mux2_1(.in1(in1),.in2(in2),.sel(sel),.out(out));

endmodule

3.2 defparam修改参数后调用

module Ex(normal,fuse,sel,out);

input[4:1] normal;

input[4:1] fuse;

input sel;

output[4:1] out;

defparam mux2_1.WIDTH=4;

Mux2_1 mux2_1(.in1(fuse),.in2(normal),.sel(sel),.out(out));

endmodule

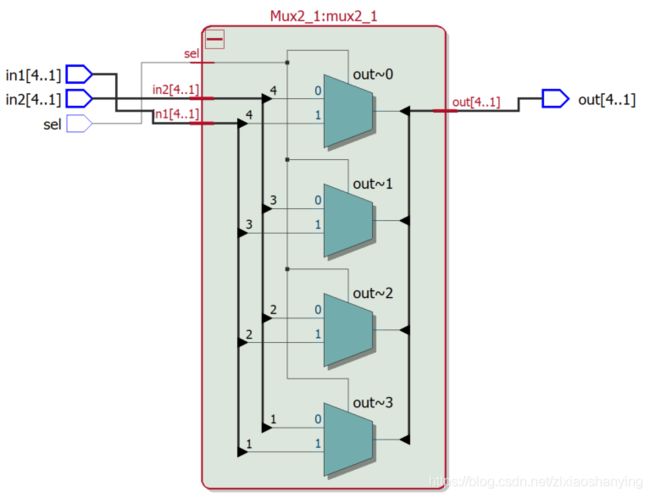

RTL视图:

3.Questasim仿真

testbench文件:

`timescale 1ns/100ps

module Top_tb(output[4:1] out);

reg[4:1] in1;

reg[4:1] in2;

reg sel;

task init;

input reg[4:1] v1;

input reg[4:1] v2;

input reg s;

begin

in1=v1;

in2=v2;

sel=s;

end

endtask

initial

begin

#5;init(0,8,0);

#5;init(1,4,0);

#5;init(2,2,0);

#5;init(4,1,0);

#5;init(8,0,0);

#5;init(0,8,1);

#5;init(1,4,1);

#5;init(2,2,1);

#5;init(4,1,1);

#5;init(8,0,1);

end

Ex ex(.fuse(in1),.normal(in2),.sel(sel),.out(out));

endmodule