error: #5: cannot open source input file “core_cmInstr.h“

GD32F103VET6和STM32F103VET6引脚兼容。

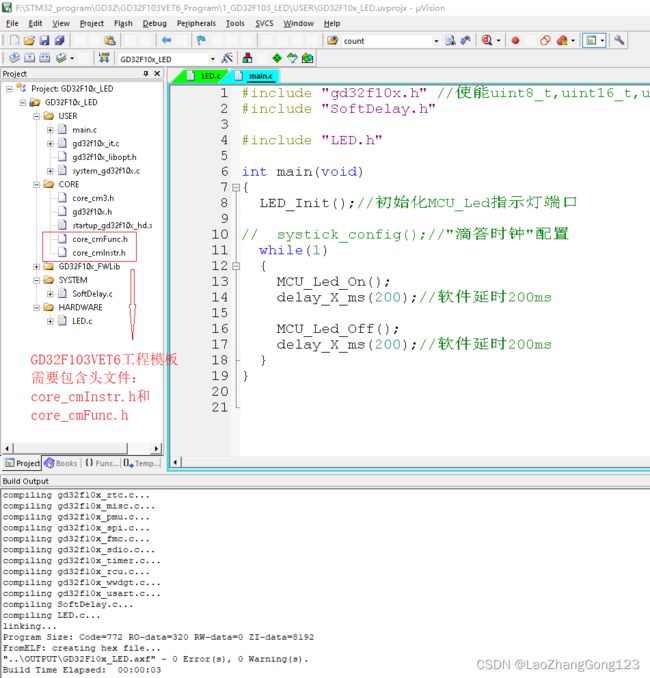

GD32F103VET6工程模板需要包含头文件:core_cmInstr.h和core_cmFunc.h,这个和STM32F103还是有区别的,否则会报错,如下:

error: #5: cannot open source input file "core_cmInstr.h": No such file or directory

贴出来,以便大家去下载,还要积分,找得还辛苦。

/**************************************************************************//**

* @file core_cmFunc.h

* @brief CMSIS Cortex-M Core Function Access Header File

* @version V3.02

* @date 24. May 2012

*

* @note

* Copyright (C) 2009-2012 ARM Limited. All rights reserved.

*

* @par

* ARM Limited (ARM) is supplying this software for use with Cortex-M

* processor based microcontrollers. This file can be freely distributed

* within development tools that are supporting such ARM based processors.

*

* @par

* THIS SOFTWARE IS PROVIDED "AS IS". NO WARRANTIES, WHETHER EXPRESS, IMPLIED

* OR STATUTORY, INCLUDING, BUT NOT LIMITED TO, IMPLIED WARRANTIES OF

* MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE APPLY TO THIS SOFTWARE.

* ARM SHALL NOT, IN ANY CIRCUMSTANCES, BE LIABLE FOR SPECIAL, INCIDENTAL, OR

* CONSEQUENTIAL DAMAGES, FOR ANY REASON WHATSOEVER.

*

******************************************************************************/

#ifndef __CORE_CMFUNC_H

#define __CORE_CMFUNC_H

/* ########################### Core Function Access ########################### */

/** \ingroup CMSIS_Core_FunctionInterface

\defgroup CMSIS_Core_RegAccFunctions CMSIS Core Register Access Functions

@{

*/

#if defined ( __CC_ARM ) /*------------------RealView Compiler -----------------*/

/* ARM armcc specific functions */

#if (__ARMCC_VERSION < 400677)

#error "Please use ARM Compiler Toolchain V4.0.677 or later!"

#endif

/* intrinsic void __enable_irq(); */

/* intrinsic void __disable_irq(); */

/** \brief Get Control Register

This function returns the content of the Control Register.

\return Control Register value

*/

__STATIC_INLINE uint32_t __get_CONTROL(void)

{

register uint32_t __regControl __ASM("control");

return(__regControl);

}

/** \brief Set Control Register

This function writes the given value to the Control Register.

\param [in] control Control Register value to set

*/

__STATIC_INLINE void __set_CONTROL(uint32_t control)

{

register uint32_t __regControl __ASM("control");

__regControl = control;

}

/** \brief Get IPSR Register

This function returns the content of the IPSR Register.

\return IPSR Register value

*/

__STATIC_INLINE uint32_t __get_IPSR(void)

{

register uint32_t __regIPSR __ASM("ipsr");

return(__regIPSR);

}

/** \brief Get APSR Register

This function returns the content of the APSR Register.

\return APSR Register value

*/

__STATIC_INLINE uint32_t __get_APSR(void)

{

register uint32_t __regAPSR __ASM("apsr");

return(__regAPSR);

}

/** \brief Get xPSR Register

This function returns the content of the xPSR Register.

\return xPSR Register value

*/

__STATIC_INLINE uint32_t __get_xPSR(void)

{

register uint32_t __regXPSR __ASM("xpsr");

return(__regXPSR);

}

/** \brief Get Process Stack Pointer

This function returns the current value of the Process Stack Pointer (PSP).

\return PSP Register value

*/

__STATIC_INLINE uint32_t __get_PSP(void)

{

register uint32_t __regProcessStackPointer __ASM("psp");

return(__regProcessStackPointer);

}

/** \brief Set Process Stack Pointer

This function assigns the given value to the Process Stack Pointer (PSP).

\param [in] topOfProcStack Process Stack Pointer value to set

*/

__STATIC_INLINE void __set_PSP(uint32_t topOfProcStack)

{

register uint32_t __regProcessStackPointer __ASM("psp");

__regProcessStackPointer = topOfProcStack;

}

/** \brief Get Main Stack Pointer

This function returns the current value of the Main Stack Pointer (MSP).

\return MSP Register value

*/

__STATIC_INLINE uint32_t __get_MSP(void)

{

register uint32_t __regMainStackPointer __ASM("msp");

return(__regMainStackPointer);

}

/** \brief Set Main Stack Pointer

This function assigns the given value to the Main Stack Pointer (MSP).

\param [in] topOfMainStack Main Stack Pointer value to set

*/

__STATIC_INLINE void __set_MSP(uint32_t topOfMainStack)

{

register uint32_t __regMainStackPointer __ASM("msp");

__regMainStackPointer = topOfMainStack;

}

/** \brief Get Priority Mask

This function returns the current state of the priority mask bit from the Priority Mask Register.

\return Priority Mask value

*/

__STATIC_INLINE uint32_t __get_PRIMASK(void)

{

register uint32_t __regPriMask __ASM("primask");

return(__regPriMask);

}

/** \brief Set Priority Mask

This function assigns the given value to the Priority Mask Register.

\param [in] priMask Priority Mask

*/

__STATIC_INLINE void __set_PRIMASK(uint32_t priMask)

{

register uint32_t __regPriMask __ASM("primask");

__regPriMask = (priMask);

}

#if (__CORTEX_M >= 0x03)

/** \brief Enable FIQ

This function enables FIQ interrupts by clearing the F-bit in the CPSR.

Can only be executed in Privileged modes.

*/

#define __enable_fault_irq __enable_fiq

/** \brief Disable FIQ

This function disables FIQ interrupts by setting the F-bit in the CPSR.

Can only be executed in Privileged modes.

*/

#define __disable_fault_irq __disable_fiq

/** \brief Get Base Priority

This function returns the current value of the Base Priority register.

\return Base Priority register value

*/

__STATIC_INLINE uint32_t __get_BASEPRI(void)

{

register uint32_t __regBasePri __ASM("basepri");

return(__regBasePri);

}

/** \brief Set Base Priority

This function assigns the given value to the Base Priority register.

\param [in] basePri Base Priority value to set

*/

__STATIC_INLINE void __set_BASEPRI(uint32_t basePri)

{

register uint32_t __regBasePri __ASM("basepri");

__regBasePri = (basePri & 0xff);

}

/** \brief Get Fault Mask

This function returns the current value of the Fault Mask register.

\return Fault Mask register value

*/

__STATIC_INLINE uint32_t __get_FAULTMASK(void)

{

register uint32_t __regFaultMask __ASM("faultmask");

return(__regFaultMask);

}

/** \brief Set Fault Mask

This function assigns the given value to the Fault Mask register.

\param [in] faultMask Fault Mask value to set

*/

__STATIC_INLINE void __set_FAULTMASK(uint32_t faultMask)

{

register uint32_t __regFaultMask __ASM("faultmask");

__regFaultMask = (faultMask & (uint32_t)1);

}

#endif /* (__CORTEX_M >= 0x03) */

#if (__CORTEX_M == 0x04)

/** \brief Get FPSCR

This function returns the current value of the Floating Point Status/Control register.

\return Floating Point Status/Control register value

*/

__STATIC_INLINE uint32_t __get_FPSCR(void)

{

#if (__FPU_PRESENT == 1) && (__FPU_USED == 1)

register uint32_t __regfpscr __ASM("fpscr");

return(__regfpscr);

#else

return(0);

#endif

}

/** \brief Set FPSCR

This function assigns the given value to the Floating Point Status/Control register.

\param [in] fpscr Floating Point Status/Control value to set

*/

__STATIC_INLINE void __set_FPSCR(uint32_t fpscr)

{

#if (__FPU_PRESENT == 1) && (__FPU_USED == 1)

register uint32_t __regfpscr __ASM("fpscr");

__regfpscr = (fpscr);

#endif

}

#endif /* (__CORTEX_M == 0x04) */

#elif defined ( __ICCARM__ ) /*------------------ ICC Compiler -------------------*/

/* IAR iccarm specific functions */

#include

#elif defined ( __TMS470__ ) /*---------------- TI CCS Compiler ------------------*/

/* TI CCS specific functions */

#include

#elif defined ( __GNUC__ ) /*------------------ GNU Compiler ---------------------*/

/* GNU gcc specific functions */

/** \brief Enable IRQ Interrupts

This function enables IRQ interrupts by clearing the I-bit in the CPSR.

Can only be executed in Privileged modes.

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __enable_irq(void)

{

__ASM volatile ("cpsie i" : : : "memory");

}

/** \brief Disable IRQ Interrupts

This function disables IRQ interrupts by setting the I-bit in the CPSR.

Can only be executed in Privileged modes.

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __disable_irq(void)

{

__ASM volatile ("cpsid i" : : : "memory");

}

/** \brief Get Control Register

This function returns the content of the Control Register.

\return Control Register value

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __get_CONTROL(void)

{

uint32_t result;

__ASM volatile ("MRS %0, control" : "=r" (result) );

return(result);

}

/** \brief Set Control Register

This function writes the given value to the Control Register.

\param [in] control Control Register value to set

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __set_CONTROL(uint32_t control)

{

__ASM volatile ("MSR control, %0" : : "r" (control) );

}

/** \brief Get IPSR Register

This function returns the content of the IPSR Register.

\return IPSR Register value

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __get_IPSR(void)

{

uint32_t result;

__ASM volatile ("MRS %0, ipsr" : "=r" (result) );

return(result);

}

/** \brief Get APSR Register

This function returns the content of the APSR Register.

\return APSR Register value

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __get_APSR(void)

{

uint32_t result;

__ASM volatile ("MRS %0, apsr" : "=r" (result) );

return(result);

}

/** \brief Get xPSR Register

This function returns the content of the xPSR Register.

\return xPSR Register value

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __get_xPSR(void)

{

uint32_t result;

__ASM volatile ("MRS %0, xpsr" : "=r" (result) );

return(result);

}

/** \brief Get Process Stack Pointer

This function returns the current value of the Process Stack Pointer (PSP).

\return PSP Register value

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __get_PSP(void)

{

register uint32_t result;

__ASM volatile ("MRS %0, psp\n" : "=r" (result) );

return(result);

}

/** \brief Set Process Stack Pointer

This function assigns the given value to the Process Stack Pointer (PSP).

\param [in] topOfProcStack Process Stack Pointer value to set

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __set_PSP(uint32_t topOfProcStack)

{

__ASM volatile ("MSR psp, %0\n" : : "r" (topOfProcStack) );

}

/** \brief Get Main Stack Pointer

This function returns the current value of the Main Stack Pointer (MSP).

\return MSP Register value

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __get_MSP(void)

{

register uint32_t result;

__ASM volatile ("MRS %0, msp\n" : "=r" (result) );

return(result);

}

/** \brief Set Main Stack Pointer

This function assigns the given value to the Main Stack Pointer (MSP).

\param [in] topOfMainStack Main Stack Pointer value to set

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __set_MSP(uint32_t topOfMainStack)

{

__ASM volatile ("MSR msp, %0\n" : : "r" (topOfMainStack) );

}

/** \brief Get Priority Mask

This function returns the current state of the priority mask bit from the Priority Mask Register.

\return Priority Mask value

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __get_PRIMASK(void)

{

uint32_t result;

__ASM volatile ("MRS %0, primask" : "=r" (result) );

return(result);

}

/** \brief Set Priority Mask

This function assigns the given value to the Priority Mask Register.

\param [in] priMask Priority Mask

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __set_PRIMASK(uint32_t priMask)

{

__ASM volatile ("MSR primask, %0" : : "r" (priMask) );

}

#if (__CORTEX_M >= 0x03)

/** \brief Enable FIQ

This function enables FIQ interrupts by clearing the F-bit in the CPSR.

Can only be executed in Privileged modes.

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __enable_fault_irq(void)

{

__ASM volatile ("cpsie f" : : : "memory");

}

/** \brief Disable FIQ

This function disables FIQ interrupts by setting the F-bit in the CPSR.

Can only be executed in Privileged modes.

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __disable_fault_irq(void)

{

__ASM volatile ("cpsid f" : : : "memory");

}

/** \brief Get Base Priority

This function returns the current value of the Base Priority register.

\return Base Priority register value

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __get_BASEPRI(void)

{

uint32_t result;

__ASM volatile ("MRS %0, basepri_max" : "=r" (result) );

return(result);

}

/** \brief Set Base Priority

This function assigns the given value to the Base Priority register.

\param [in] basePri Base Priority value to set

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __set_BASEPRI(uint32_t value)

{

__ASM volatile ("MSR basepri, %0" : : "r" (value) );

}

/** \brief Get Fault Mask

This function returns the current value of the Fault Mask register.

\return Fault Mask register value

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __get_FAULTMASK(void)

{

uint32_t result;

__ASM volatile ("MRS %0, faultmask" : "=r" (result) );

return(result);

}

/** \brief Set Fault Mask

This function assigns the given value to the Fault Mask register.

\param [in] faultMask Fault Mask value to set

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __set_FAULTMASK(uint32_t faultMask)

{

__ASM volatile ("MSR faultmask, %0" : : "r" (faultMask) );

}

#endif /* (__CORTEX_M >= 0x03) */

#if (__CORTEX_M == 0x04)

/** \brief Get FPSCR

This function returns the current value of the Floating Point Status/Control register.

\return Floating Point Status/Control register value

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __get_FPSCR(void)

{

#if (__FPU_PRESENT == 1) && (__FPU_USED == 1)

uint32_t result;

__ASM volatile ("VMRS %0, fpscr" : "=r" (result) );

return(result);

#else

return(0);

#endif

}

/** \brief Set FPSCR

This function assigns the given value to the Floating Point Status/Control register.

\param [in] fpscr Floating Point Status/Control value to set

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __set_FPSCR(uint32_t fpscr)

{

#if (__FPU_PRESENT == 1) && (__FPU_USED == 1)

__ASM volatile ("VMSR fpscr, %0" : : "r" (fpscr) );

#endif

}

#endif /* (__CORTEX_M == 0x04) */

#elif defined ( __TASKING__ ) /*------------------ TASKING Compiler --------------*/

/* TASKING carm specific functions */

/*

* The CMSIS functions have been implemented as intrinsics in the compiler.

* Please use "carm -?i" to get an up to date list of all instrinsics,

* Including the CMSIS ones.

*/

#endif

/*@} end of CMSIS_Core_RegAccFunctions */

#endif /* __CORE_CMFUNC_H */ /**************************************************************************//**

* @file core_cmInstr.h

* @brief CMSIS Cortex-M Core Instruction Access Header File

* @version V3.02

* @date 08. May 2012

*

* @note

* Copyright (C) 2009-2012 ARM Limited. All rights reserved.

*

* @par

* ARM Limited (ARM) is supplying this software for use with Cortex-M

* processor based microcontrollers. This file can be freely distributed

* within development tools that are supporting such ARM based processors.

*

* @par

* THIS SOFTWARE IS PROVIDED "AS IS". NO WARRANTIES, WHETHER EXPRESS, IMPLIED

* OR STATUTORY, INCLUDING, BUT NOT LIMITED TO, IMPLIED WARRANTIES OF

* MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE APPLY TO THIS SOFTWARE.

* ARM SHALL NOT, IN ANY CIRCUMSTANCES, BE LIABLE FOR SPECIAL, INCIDENTAL, OR

* CONSEQUENTIAL DAMAGES, FOR ANY REASON WHATSOEVER.

*

******************************************************************************/

#ifndef __CORE_CMINSTR_H

#define __CORE_CMINSTR_H

/* ########################## Core Instruction Access ######################### */

/** \defgroup CMSIS_Core_InstructionInterface CMSIS Core Instruction Interface

Access to dedicated instructions

@{

*/

#if defined ( __CC_ARM ) /*------------------RealView Compiler -----------------*/

/* ARM armcc specific functions */

#if (__ARMCC_VERSION < 400677)

#error "Please use ARM Compiler Toolchain V4.0.677 or later!"

#endif

/** \brief No Operation

No Operation does nothing. This instruction can be used for code alignment purposes.

*/

#define __NOP __nop

/** \brief Wait For Interrupt

Wait For Interrupt is a hint instruction that suspends execution

until one of a number of events occurs.

*/

#define __WFI __wfi

/** \brief Wait For Event

Wait For Event is a hint instruction that permits the processor to enter

a low-power state until one of a number of events occurs.

*/

#define __WFE __wfe

/** \brief Send Event

Send Event is a hint instruction. It causes an event to be signaled to the CPU.

*/

#define __SEV __sev

/** \brief Instruction Synchronization Barrier

Instruction Synchronization Barrier flushes the pipeline in the processor,

so that all instructions following the ISB are fetched from cache or

memory, after the instruction has been completed.

*/

#define __ISB() __isb(0xF)

/** \brief Data Synchronization Barrier

This function acts as a special kind of Data Memory Barrier.

It completes when all explicit memory accesses before this instruction complete.

*/

#define __DSB() __dsb(0xF)

/** \brief Data Memory Barrier

This function ensures the apparent order of the explicit memory operations before

and after the instruction, without ensuring their completion.

*/

#define __DMB() __dmb(0xF)

/** \brief Reverse byte order (32 bit)

This function reverses the byte order in integer value.

\param [in] value Value to reverse

\return Reversed value

*/

#define __REV __rev

/** \brief Reverse byte order (16 bit)

This function reverses the byte order in two unsigned short values.

\param [in] value Value to reverse

\return Reversed value

*/

#ifndef __NO_EMBEDDED_ASM

__attribute__((section(".rev16_text"))) __STATIC_INLINE __ASM uint32_t __REV16(uint32_t value)

{

rev16 r0, r0

bx lr

}

#endif

/** \brief Reverse byte order in signed short value

This function reverses the byte order in a signed short value with sign extension to integer.

\param [in] value Value to reverse

\return Reversed value

*/

#ifndef __NO_EMBEDDED_ASM

__attribute__((section(".revsh_text"))) __STATIC_INLINE __ASM int32_t __REVSH(int32_t value)

{

revsh r0, r0

bx lr

}

#endif

/** \brief Rotate Right in unsigned value (32 bit)

This function Rotate Right (immediate) provides the value of the contents of a register rotated by a variable number of bits.

\param [in] value Value to rotate

\param [in] value Number of Bits to rotate

\return Rotated value

*/

#define __ROR __ror

#if (__CORTEX_M >= 0x03)

/** \brief Reverse bit order of value

This function reverses the bit order of the given value.

\param [in] value Value to reverse

\return Reversed value

*/

#define __RBIT __rbit

/** \brief LDR Exclusive (8 bit)

This function performs a exclusive LDR command for 8 bit value.

\param [in] ptr Pointer to data

\return value of type uint8_t at (*ptr)

*/

#define __LDREXB(ptr) ((uint8_t ) __ldrex(ptr))

/** \brief LDR Exclusive (16 bit)

This function performs a exclusive LDR command for 16 bit values.

\param [in] ptr Pointer to data

\return value of type uint16_t at (*ptr)

*/

#define __LDREXH(ptr) ((uint16_t) __ldrex(ptr))

/** \brief LDR Exclusive (32 bit)

This function performs a exclusive LDR command for 32 bit values.

\param [in] ptr Pointer to data

\return value of type uint32_t at (*ptr)

*/

#define __LDREXW(ptr) ((uint32_t ) __ldrex(ptr))

/** \brief STR Exclusive (8 bit)

This function performs a exclusive STR command for 8 bit values.

\param [in] value Value to store

\param [in] ptr Pointer to location

\return 0 Function succeeded

\return 1 Function failed

*/

#define __STREXB(value, ptr) __strex(value, ptr)

/** \brief STR Exclusive (16 bit)

This function performs a exclusive STR command for 16 bit values.

\param [in] value Value to store

\param [in] ptr Pointer to location

\return 0 Function succeeded

\return 1 Function failed

*/

#define __STREXH(value, ptr) __strex(value, ptr)

/** \brief STR Exclusive (32 bit)

This function performs a exclusive STR command for 32 bit values.

\param [in] value Value to store

\param [in] ptr Pointer to location

\return 0 Function succeeded

\return 1 Function failed

*/

#define __STREXW(value, ptr) __strex(value, ptr)

/** \brief Remove the exclusive lock

This function removes the exclusive lock which is created by LDREX.

*/

#define __CLREX __clrex

/** \brief Signed Saturate

This function saturates a signed value.

\param [in] value Value to be saturated

\param [in] sat Bit position to saturate to (1..32)

\return Saturated value

*/

#define __SSAT __ssat

/** \brief Unsigned Saturate

This function saturates an unsigned value.

\param [in] value Value to be saturated

\param [in] sat Bit position to saturate to (0..31)

\return Saturated value

*/

#define __USAT __usat

/** \brief Count leading zeros

This function counts the number of leading zeros of a data value.

\param [in] value Value to count the leading zeros

\return number of leading zeros in value

*/

#define __CLZ __clz

#endif /* (__CORTEX_M >= 0x03) */

#elif defined ( __ICCARM__ ) /*------------------ ICC Compiler -------------------*/

/* IAR iccarm specific functions */

#include

#elif defined ( __TMS470__ ) /*---------------- TI CCS Compiler ------------------*/

/* TI CCS specific functions */

#include

#elif defined ( __GNUC__ ) /*------------------ GNU Compiler ---------------------*/

/* GNU gcc specific functions */

/** \brief No Operation

No Operation does nothing. This instruction can be used for code alignment purposes.

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __NOP(void)

{

__ASM volatile ("nop");

}

/** \brief Wait For Interrupt

Wait For Interrupt is a hint instruction that suspends execution

until one of a number of events occurs.

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __WFI(void)

{

__ASM volatile ("wfi");

}

/** \brief Wait For Event

Wait For Event is a hint instruction that permits the processor to enter

a low-power state until one of a number of events occurs.

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __WFE(void)

{

__ASM volatile ("wfe");

}

/** \brief Send Event

Send Event is a hint instruction. It causes an event to be signaled to the CPU.

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __SEV(void)

{

__ASM volatile ("sev");

}

/** \brief Instruction Synchronization Barrier

Instruction Synchronization Barrier flushes the pipeline in the processor,

so that all instructions following the ISB are fetched from cache or

memory, after the instruction has been completed.

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __ISB(void)

{

__ASM volatile ("isb");

}

/** \brief Data Synchronization Barrier

This function acts as a special kind of Data Memory Barrier.

It completes when all explicit memory accesses before this instruction complete.

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __DSB(void)

{

__ASM volatile ("dsb");

}

/** \brief Data Memory Barrier

This function ensures the apparent order of the explicit memory operations before

and after the instruction, without ensuring their completion.

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __DMB(void)

{

__ASM volatile ("dmb");

}

/** \brief Reverse byte order (32 bit)

This function reverses the byte order in integer value.

\param [in] value Value to reverse

\return Reversed value

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __REV(uint32_t value)

{

uint32_t result;

__ASM volatile ("rev %0, %1" : "=r" (result) : "r" (value) );

return(result);

}

/** \brief Reverse byte order (16 bit)

This function reverses the byte order in two unsigned short values.

\param [in] value Value to reverse

\return Reversed value

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __REV16(uint32_t value)

{

uint32_t result;

__ASM volatile ("rev16 %0, %1" : "=r" (result) : "r" (value) );

return(result);

}

/** \brief Reverse byte order in signed short value

This function reverses the byte order in a signed short value with sign extension to integer.

\param [in] value Value to reverse

\return Reversed value

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE int32_t __REVSH(int32_t value)

{

uint32_t result;

__ASM volatile ("revsh %0, %1" : "=r" (result) : "r" (value) );

return(result);

}

/** \brief Rotate Right in unsigned value (32 bit)

This function Rotate Right (immediate) provides the value of the contents of a register rotated by a variable number of bits.

\param [in] value Value to rotate

\param [in] value Number of Bits to rotate

\return Rotated value

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __ROR(uint32_t op1, uint32_t op2)

{

__ASM volatile ("ror %0, %0, %1" : "+r" (op1) : "r" (op2) );

return(op1);

}

#if (__CORTEX_M >= 0x03)

/** \brief Reverse bit order of value

This function reverses the bit order of the given value.

\param [in] value Value to reverse

\return Reversed value

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __RBIT(uint32_t value)

{

uint32_t result;

__ASM volatile ("rbit %0, %1" : "=r" (result) : "r" (value) );

return(result);

}

/** \brief LDR Exclusive (8 bit)

This function performs a exclusive LDR command for 8 bit value.

\param [in] ptr Pointer to data

\return value of type uint8_t at (*ptr)

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint8_t __LDREXB(volatile uint8_t *addr)

{

uint8_t result;

__ASM volatile ("ldrexb %0, [%1]" : "=r" (result) : "r" (addr) );

return(result);

}

/** \brief LDR Exclusive (16 bit)

This function performs a exclusive LDR command for 16 bit values.

\param [in] ptr Pointer to data

\return value of type uint16_t at (*ptr)

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint16_t __LDREXH(volatile uint16_t *addr)

{

uint16_t result;

__ASM volatile ("ldrexh %0, [%1]" : "=r" (result) : "r" (addr) );

return(result);

}

/** \brief LDR Exclusive (32 bit)

This function performs a exclusive LDR command for 32 bit values.

\param [in] ptr Pointer to data

\return value of type uint32_t at (*ptr)

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __LDREXW(volatile uint32_t *addr)

{

uint32_t result;

__ASM volatile ("ldrex %0, [%1]" : "=r" (result) : "r" (addr) );

return(result);

}

/** \brief STR Exclusive (8 bit)

This function performs a exclusive STR command for 8 bit values.

\param [in] value Value to store

\param [in] ptr Pointer to location

\return 0 Function succeeded

\return 1 Function failed

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __STREXB(uint8_t value, volatile uint8_t *addr)

{

uint32_t result;

__ASM volatile ("strexb %0, %2, [%1]" : "=&r" (result) : "r" (addr), "r" (value) );

return(result);

}

/** \brief STR Exclusive (16 bit)

This function performs a exclusive STR command for 16 bit values.

\param [in] value Value to store

\param [in] ptr Pointer to location

\return 0 Function succeeded

\return 1 Function failed

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __STREXH(uint16_t value, volatile uint16_t *addr)

{

uint32_t result;

__ASM volatile ("strexh %0, %2, [%1]" : "=&r" (result) : "r" (addr), "r" (value) );

return(result);

}

/** \brief STR Exclusive (32 bit)

This function performs a exclusive STR command for 32 bit values.

\param [in] value Value to store

\param [in] ptr Pointer to location

\return 0 Function succeeded

\return 1 Function failed

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __STREXW(uint32_t value, volatile uint32_t *addr)

{

uint32_t result;

__ASM volatile ("strex %0, %2, [%1]" : "=&r" (result) : "r" (addr), "r" (value) );

return(result);

}

/** \brief Remove the exclusive lock

This function removes the exclusive lock which is created by LDREX.

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __CLREX(void)

{

__ASM volatile ("clrex");

}

/** \brief Signed Saturate

This function saturates a signed value.

\param [in] value Value to be saturated

\param [in] sat Bit position to saturate to (1..32)

\return Saturated value

*/

#define __SSAT(ARG1,ARG2) \

({ \

uint32_t __RES, __ARG1 = (ARG1); \

__ASM ("ssat %0, %1, %2" : "=r" (__RES) : "I" (ARG2), "r" (__ARG1) ); \

__RES; \

})

/** \brief Unsigned Saturate

This function saturates an unsigned value.

\param [in] value Value to be saturated

\param [in] sat Bit position to saturate to (0..31)

\return Saturated value

*/

#define __USAT(ARG1,ARG2) \

({ \

uint32_t __RES, __ARG1 = (ARG1); \

__ASM ("usat %0, %1, %2" : "=r" (__RES) : "I" (ARG2), "r" (__ARG1) ); \

__RES; \

})

/** \brief Count leading zeros

This function counts the number of leading zeros of a data value.

\param [in] value Value to count the leading zeros

\return number of leading zeros in value

*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint8_t __CLZ(uint32_t value)

{

uint8_t result;

__ASM volatile ("clz %0, %1" : "=r" (result) : "r" (value) );

return(result);

}

#endif /* (__CORTEX_M >= 0x03) */

#elif defined ( __TASKING__ ) /*------------------ TASKING Compiler --------------*/

/* TASKING carm specific functions */

/*

* The CMSIS functions have been implemented as intrinsics in the compiler.

* Please use "carm -?i" to get an up to date list of all intrinsics,

* Including the CMSIS ones.

*/

#endif

/*@}*/ /* end of group CMSIS_Core_InstructionInterface */

#endif /* __CORE_CMINSTR_H */