2.3 Verilog HDL运算符

运算符

- 1 算术运算符

- 2 逻辑运算符

- 3 按位运算符

- 4 关系运算符

- 5 等式运算符

- 6 缩减运算符

- 7 移位运算符

- 8 条件运算符和拼接运算符

-

- 8.1 条件运算符

- 8.2 拼接运算符

- 9 运算符的优先级

1 算术运算符

注意:

在进行整数的除法运算时,结果要略去小数部分,只取整数部分;而进行取模运算时(%,亦称作求余运算符)

结果的符号位采用模运算符中第一个操作数的符号。

例如,-10%3 结果-1 ,11%-3 结果为2。

在进行算术运算时,如果某一个操作数有不确定的值x,则整个结果也为不确定值x。

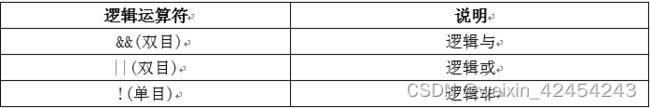

2 逻辑运算符

逻辑运算只区分真假,而不管是什么数值。逻辑运算的输入4’ha1和4’h01是没有区别的,都是逻辑真,**而0为逻辑假。**一般来说,逻辑运算的结果要么为真(1)要么为假(0)。

特例是如果有一个输入为未知X,那么结果也是X。

例如,4’ha1&&4h01是1,4’ha1&&4h00是0。

只有两个输入都是0的时候,逻辑或的结果才是0。

对于逻辑非,当输入为非0值,输出就是0。

逻辑运算最常用于条件判断语句。

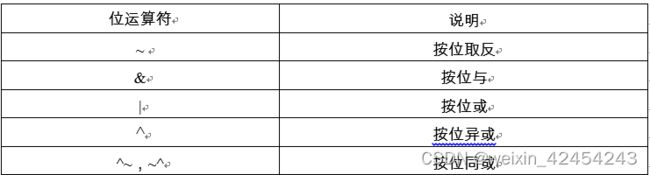

3 按位运算符

通常使用按位运算符完成基本的与、或、非、异或及同或逻辑运算。使用这些位运算符进行组合,很容易完成其他的逻辑运算。

按位运算要求对两个操作数的相应位逐位进行运算。

例如 0101&1100=0100,0101|1100=1101

f=abc应表示为f=a&b&c

4 关系运算符

关系运算符和逻辑运算符一般用于条件判断语句。

关系运算结果为1位的逻辑值1(真)或0(假),但也可能是x(未知)。关系运算符根据关系运算的结果是真还是假,用于条件判断。

关系运算时,若关系为真,则返回值为1;若声明的关系为假,则返回值为0;若某操作数为不定值x,则返回值也一定为x。

5 等式运算符

“”和“!=”称作逻辑等式运算符,其结果由两个操作数的值决定。由于操作数可能是x或z,其结果可能为x。

“=”和“!”常用于case表达式的判别,又称作case等式运算符。其结果只能为0和1。如果操作数中存在x和z,那么操作数必须完全相同结果才为1,否则为0。

“”和“=”是完全不同的,“=”是对寄存器赋值使用的。

6 缩减运算符

c=((b[0]&b[1]) &b[2] ) & b[3];

7 移位运算符

a>>n中a代表要进行向右移位的操作数,n代表要移几位。a<

但是当a是一个4位的寄存器,那么a=4’b1001<<1,a的结果就是4’b0010。

8 条件运算符和拼接运算符

8.1 条件运算符

条件运算符是书写效率非常高的运算符。

条件运算符为?,很像C语言里面的?运算符。它实现的是组合逻辑,或者说就是多路复用器。

用法:assign wire类型变量 = 条件?表达式1:表达式2;

例如assign out = sel? in1:in0;描述了

当sel为1的时候 out=in1;

否则, out=in0;

是多路选择逻辑。

如果想对寄存器变量赋值,不能使用条件运算符,而要用always块中使用条件判断语句。

8.2 拼接运算符

拼接运算是非常有意思的,非常高效率。

使用拼接运算符可以将变量任意组合后输出或送给另一个变量。

用法:{信号1的某几位,信号2的某几位,…信号n的某几位}

{a,b[3:0],w,3'b101} //等同于{a,b[3],b[2],b[1],b[0],w,1b'1,1'b0,1'b1}

{4{w}} //等同于{w,w,w,w}

{b,{3{a,b}}} //等同于{b,a,b,a,b,a,b}

这里面的3、4必须是常量表达式

例如变量r1定义为 reg[8:0] r1,并且a,b都是8位的变量。

r1={a[3:0],b[3:0]}表示r1的 r[7]=a[3],r[6]=a[2]…r[0]=b[0]。

如果a=17即8‘b00110001,b=138即8’b10001010,那么r1=8‘b0001 1010。

r1={r1[3:0],r1[7:4]}实现了将r1的高4位和低4位交换。