21 跨时钟域(CDC)电路设计——clock domain cross

芯片通常多个时钟,如何保证数据在各个时钟间传输的正确性——跨时钟域处理。 Metastable——亚稳态——解决:单bit 多bit CDC,FIFO IP核

首先叠个甲,这里是课程笔记,如果觉得侵权请联系删帖。

目录

1.同步时钟/异步时钟定义

2.亚稳态的产生 metastable

2.1亚稳态产生的原因和后果:

2.2解决办法:同步时钟的跨时钟域处理!!

2.3跨时钟域处理目标

3. 一位数据的跨时钟域电路——总结:比较复杂,容易出错

3.1电路要正常工作,需要一些前提假设:

总结:为什么用两个寄存器能够100%保证数据的同步是正确的:

3.2完整的情况——这个现象很重要,记住!

3.3错误的1bit CDC电路

1.本质:组合逻辑的输出不稳定,会产生错误的翻转脉冲!

2.原因:第一级同步寄存器在发生亚稳态效应时,工具是不知道它CK to Q延时的,并且会比cell library里面正常的ck to Q要大,工具看起来正常的setup hold,实际情况下可能是不对的,导致整个CDC电路的输出还有可能是亚稳态的。

3.已经有一个完整的两拍寄存了

4.多位跨时钟域同步电路

4.1首先,不能简单直接扩展单位跨时钟域电路

4.2怎么做?

1.注意:将vld信号先经过1bit跨时钟域同步信号,这是sync1就是一个能够同步的使能信号(时钟),但是他不能直接作为时钟(时钟要干净 STA中会讲),需要经过寄存器、sync1 异或后 输出cap脉冲信号,这个cap信号当enabel使能信号,来直接将数据data从clk0时钟域抓到clk1时钟域。

2.效率更高:上升沿可以传输,下降沿也可以传输,无反馈——但vld的长度 和 clk1还有一定的需要,(需要把sync 0 1的波形画下来,同时假设时钟上升沿vld慢一拍?),vld可能需要2-三个周期传一次

5.能否更快?——Async—FIFO设计

6.跨时钟域电路设计

1.注意使用的时候,还是读一下ip源码,用CDC准则去检查一下,看有没有做错,因为原有设计的频率可能只要跑50M,现在设计要跑100M甚至1Ghz,是不是需要做更多的timing constrain——高速情况下!?

2.跨时钟域电路验证——仿真无法验证——因为仿真一个寄存器是不会检查 setup/hold的,同时也不会产生ck to Q的delay!

3.所以后仿也不能仿出来!——如何保证CDC电路的正确性?——所以写1bit跨时钟域电路要仔细再仔细,同时一般不要自己去写Async-FIFO。

7.跨时钟域电路的时序约束

1.电路结构√,然后,Timing做STA时,怎么约束一个跨时钟域的path?

2.一位1bit信号CDC电路

3. 其他

1.同步时钟/异步时钟定义

2.亚稳态的产生 metastable

2.1亚稳态产生的原因和后果:

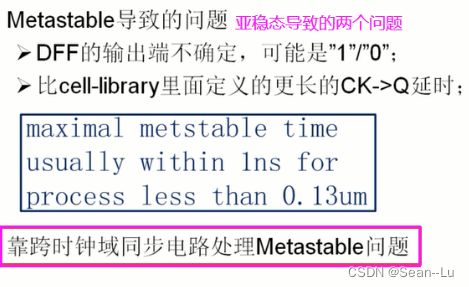

为什么会不满足setup/hold?——因为跨时钟域,从clk0 到 clk1,时钟域时,clk0时钟域下数据寄存器的输出端d_saync,作为下一个在clk1时钟域下寄存器的D端输入,寄存器的输入在clk1上升沿到来时可能不满足 setup/hold 的要求,导致出现亚稳态的现象。后果有两个。

下面这张图一定要记住! 因为setup/hold不满足,会产生亚稳态效应,亚稳态会产生两个问题:1.ck to Q的延时相对于满足setup/hold的寄存器更长(如小于点13um的工艺,一般最大不超过1ns) 2.最终的输出能稳定,但会出现稳定值在0或1的两种情况!

2.2解决办法:同步时钟的跨时钟域处理!!

2.3跨时钟域处理目标

3. 一位数据的跨时钟域电路——总结:比较复杂,容易出错

3.1电路要正常工作,需要一些前提假设:

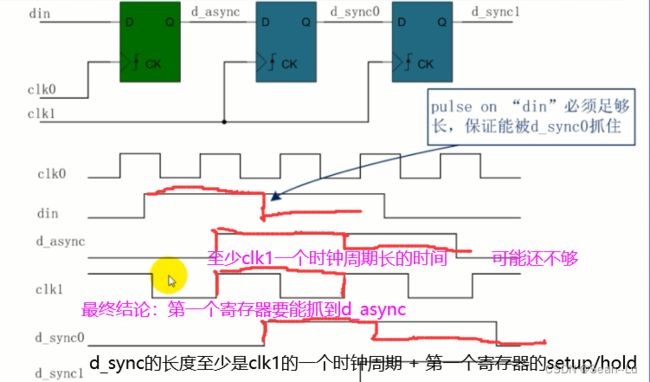

一共三个寄存器,分别是寄存器,第一个同步寄存器、第二个同步寄存器

①寄存器的输入信号din需要传输的电平需要保持足够长,保证能被d_sync0,即同步信号0看到(同步信号0是指第一个同步寄存器的Q输出端)

问题:多长叫足够长?

答:(图中有误,是d_async)输入第一个同步寄存器的信号d_async维持传输电平的长度,至少是同步寄存器时钟clk1的一个周期长度,加上第一个同步寄存器的setup/hold的时间。

大学老师:两个寄存器打两拍是有一定概率 亚稳态效应,如第一个同步寄存器有万分之一概率亚稳态输出,第二个也是万分之一,如1/10^8 的概率还是存在亚稳态效应?

工程师:假设电路频率为200M,1s有2*10^8个时钟,亚稳态概率1/10^8,即1s,会错误2次——无法接受!!!——所以不太赞同大学老师的说法。

赞同的说法:第一个同步寄存器肯定会有亚稳态效应,它的Ck 到 Q有最大值,比如是最大1ns; 只要同步时钟clk1周期能够大于1ns(如500Mhz,2ns),再加上第一个寄存器的一些setup/hold的时间,那么第二个寄存器至少有1ns的setup时间,所以只要第二个寄存器的setup时间小于1ns,第二个同步寄存器的输出就是正确的。——保证100%正确!

总结:为什么用两个寄存器能够100%保证数据的同步是正确的:

答:有两个前提假设:

①寄存器的输入信号din传输电平需要保持足够长,能够被同步时钟clk1抓住

②第一个寄存器发生亚稳态时,同步时钟ck1 到 Q端输出有的最大延时需要小于同步时钟clk1的时钟周期,就能保证第二个寄存器不发生亚稳态现象。

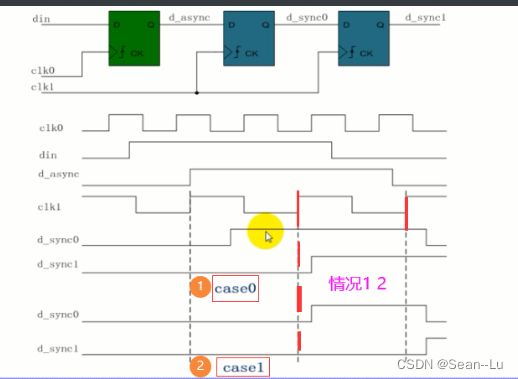

3.2完整的情况——这个现象很重要,记住!

问题:1bit的跨时钟域同步电路存在不确定性,即输入信号到同步信号的输出时延是无法确定的(有可能早一个时钟周期(case0),有可能晚一个(case1)),无法预期同步信号的输出时间,可能早一个周期,可能晚一个周期。 出现原因——画波形图能够看出来。

3.3错误的1bit CDC电路

1.本质:组合逻辑的输出不稳定,会产生错误的翻转脉冲!

解决办法:clk0 到 clk1之间不能假如任何的组合逻辑,用寄存器输出直接接过来!

原因:组合电路运算时会产生一些不必要的脉冲,当输入信号0 1 2 发生变化,因为每个信号到输出时长都是不一样的,导致会得到一些错误的中间输出(上下翻转的脉冲),只有经过一段时间后的输出才会是稳定的。

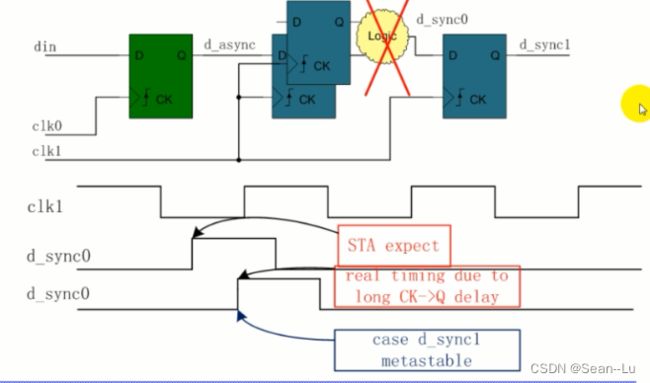

2.原因:第一级同步寄存器在发生亚稳态效应时,工具是不知道它CK to Q延时的,并且会比cell library里面正常的ck to Q要大,工具看起来正常的setup hold,实际情况下可能是不对的,导致整个CDC电路的输出还有可能是亚稳态的。

解决办法:直接Q输出接到D,不能接组合逻辑

对DC到PT工具来说,就算不接logic,接一根线Q到D,也是有风险的。这是一个盲点!!

规避方法: ①Q到D加一个时序约束——set maximum delay,设定最大延迟,并把亚稳态的延迟的扣掉。把以前基于cycle的分析给重写、覆盖掉。 ②有的cell会把两个寄存器做到一起,D 到 Q delay就很小。

3.已经有一个完整的两拍寄存了

4.多位跨时钟域同步电路

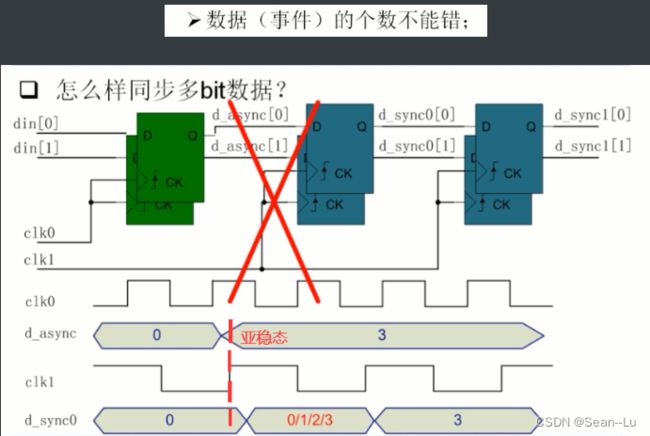

4.1首先,不能简单直接扩展单位跨时钟域电路

原因:因为第一级的两个同步寄存器存在亚稳态现象,会导致d_async【0】输出0 1 两种情况、【1】输出两种情况,会出现多个数据!

设计时常犯的错误,因为两位信号都有亚稳态的可能,然后最后输出使用时出现组合的问题,有的状态,如10,甚至在状态机中都没有设定,肯定是不行的。

在同一地方,被同一个组合逻辑看到,都是不行的。

4.2怎么做?

第一种方案,有点类似:TCP/IP 三次握手,0-1-2-3这些个流程理解为握手。 对两个时钟频率基本没有要求——但耗时太多!

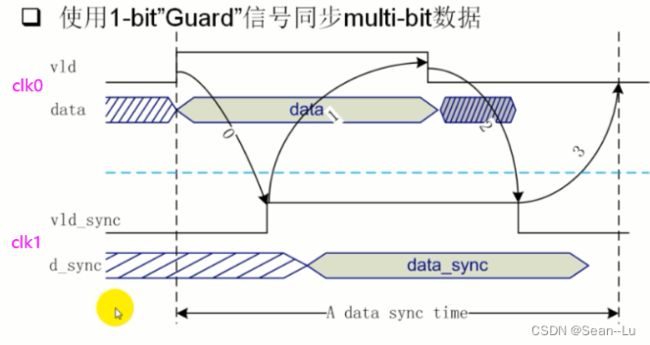

1.注意:将vld信号先经过1bit跨时钟域同步信号,这是sync1就是一个能够同步的使能信号(时钟),但是他不能直接作为时钟(时钟要干净 STA中会讲),需要经过寄存器、sync1 异或后 输出cap脉冲信号,这个cap信号当enabel使能信号,来直接将数据data从clk0时钟域抓到clk1时钟域。

思想:把vld做同步,同步后产生一个pulse脉冲,直接把data抓过来。(data不需要经过1bit同步电路!)

sync1不能作为时钟信号:会出现多的数据?

2.效率更高:上升沿可以传输,下降沿也可以传输,无反馈——但vld的长度 和 clk1还有一定的需要,(需要把sync 0 1的波形画下来,同时假设时钟上升沿vld慢一拍?),vld可能需要2-三个周期传一次

5.能否更快?——Async—FIFO设计

ic设计就直接调用就行了,大公司也有的自己的大的ip 轻易不要自己写,容易犯错!

6.跨时钟域电路设计

1.注意使用的时候,还是读一下ip源码,用CDC准则去检查一下,看有没有做错,因为原有设计的频率可能只要跑50M,现在设计要跑100M甚至1Ghz,是不是需要做更多的timing constrain——高速情况下!?

2.跨时钟域电路验证——仿真无法验证——因为仿真一个寄存器是不会检查 setup/hold的,同时也不会产生ck to Q的delay!

各种toggle排列组合是否验证足够?——之前只会验证单一信号的翻转。 仿真时间是否足够长?

3.所以后仿也不能仿出来!——如何保证CDC电路的正确性?——所以写1bit跨时钟域电路要仔细再仔细,同时一般不要自己去写Async-FIFO。

7.跨时钟域电路的时序约束

1.电路结构√,然后,Timing做STA时,怎么约束一个跨时钟域的path?

并且也知道在D pin处一定会有 亚稳态,如果不去掉,后面会出现很多的unknown信号!