UART 实验

UART 实验

串口实验,异步串行通信,异步串行是指UART(Universal Asynchronous Receiver/Transmitter),通用异步接收/发送。

使用PL每秒钟向外部发送数据,同时将收到的数据也发送出去即回环。

实验原理

异步串口通信协议

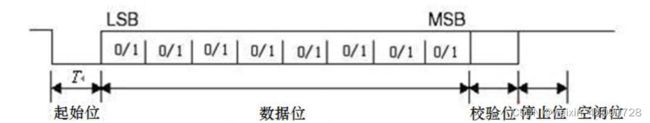

消息帧从一个低位起始位开始,后面是7 个或8 个数据位,一个可用的奇偶位和一个或几个高位停止位。接收器发现开始位时它就知道数据准备发送,并尝试与发送器时钟频率同步。

奇偶校验用于检验传输是否出差。

时序图如下,注意该图只常用的设计时序,实际还可能相反,比如(高电平为0,低电平为1,默认为低电平,RS232)。

一个消息帧只传输8个字节以下的数据,在起始位进行时钟同步,根据波特率进行数据采样。

根据传输协议,需要根据起始位进行数据的传输。

实验步骤

这里尝试使用软件工程的思想去进行描述,学习下软件工程。

需求分析

为了加深用户对verilog语言和串口知识的掌握,需要使用开发板实现一个“伪”回环的串口,实现功能如下:

- 串口数据为8位,停止位为1位。

- 每秒向外发送“HELLO ALINX”字符串。

- 串口将收到的数据发送回去,实现回环的功能。

概要设计

模块设计

开发板对外的接口是一个micro-usb的接口,可简单理解为一个两条线(发送tx,接收rx)的串口,时钟是一个200MHz的差分时钟,一个复位按钮,电平默认为高,按下为低。

一共划分为3个模块,数据接收模块,数据发送模块,数据处理模块。

数据接收模块实现对硬件接收管脚的采样,完成对串口数据的接收。

数据发送模块实现将数据按串口协议通过发送管脚发送出去的功能。

数据处理模块负责每秒钟向外发送字符串,将接收数据发送出去的功能。

其中,数据处理模块调用数据接收模块和数据发送模块,数据接收模块和数据发送模块相互独立。

各个模块的接口设计其实也比较简单。在verilog中,时钟是驱动模块的灵魂,复位是保证模块正常工作的基础,因此在设计中这两个是不可或缺的。还有硬件的物理管脚也需要加上去。除了这些不可以改变的,剩下的主要是一些控制信号,由开发者自行设计。

数据接收模块设计接口如下,clk、rst_n为时钟和复位信号,rx_pin为硬件接收接口,rx_data存放接收到的数据,rx_data_valid用来表示接收数据是否有效,rx_data_ready表示后端是否已将数据接收,如果接收了才可正常进行下一个数据的采样。参数CLK_FRE、BAUD_RATE用来表示输入时钟频率和需要的波特率,增加模块的可移植性。

module uart_rx

#(

parameter CLK_FRE = 50, //clock frequency(Mhz)

parameter BAUD_RATE = 115200 //serial baud rate

)

(

input clk, //clock input

input rst_n, //asynchronous reset input, low active

output reg[7:0] rx_data, //received serial data

output reg rx_data_valid, //received serial data is valid

input rx_data_ready, //data receiver module ready

input rx_pin //serial data input

);

数据发送模块的设计接口如下,clk为输入时钟,rst_n为输入复位信号,tx_data为输入发送数据寄存器,tx_data_valid为输入发送有效信号,tx_data_ready为输出发送准备信号(为高时表示可以进行数据的发送),tx_pin为输出发送管脚。

module uart_tx

#(

parameter CLK_FRE = 50, //clock frequency(Mhz)

parameter BAUD_RATE = 115200 //serial baud rate

)

(

input clk, //clock input

input rst_n, //asynchronous reset input, low active

input[7:0] tx_data, //data to send

input tx_data_valid, //data to be sent is valid

output reg tx_data_ready, //send ready

output tx_pin //serial data output

);

数据处理模块的设计接口如下,sys_clk_p、sys_clk_n为输入差分时钟,rst_n为输入复位信号,uart_rx为输入接收管脚,uart_tx为输出发送管脚。

module uart_test(

input sys_clk_p, //system clock 200Mhz postive pin

input sys_clk_n, //system clock 200Mhz negetive pin

input rst_n, //reset ,low active

input uart_rx,

output uart_tx

);

详细设计

详细设计前面概要设计中的各个模块。

数据接收模块

上电进入S_IDLE空闲状态,下降沿到来到S_START起始位状态,等待1bit的停止位,开始接收数据S_REV_BYTE,接收(采样)8个数据位进入停止位S_STOP,等待0.5bit后发送数据到其他模块S_DATA,后端接收数据后再次进入空闲状态。这里主要的难点是各个状态之间的转移关系。

起始位检测设计

这里串口的起始位为下降沿,主要是边沿判断,这一需要记录电平的两个状态,当前一个状态为1,后一个状态为0时,则表示下降沿到来。这是要注意在时间上前一个状态为旧的,后一个状态为新的。可以使用两个rx_d0、rx_d1寄存器来实现,rx_d0记录输入管脚最新的电平,rx_d1用来保存rx_d0上次的电平,只要rx_d1&&~rx_d0为真时,表明下降沿到来。

reg rx_d0; //delay 1 clock for rx_pin

reg rx_d1; //delay 1 clock for rx_d0

assign rx_negedge = rx_d1 && ~rx_d0;

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

begin

rx_d0 <= 1'b0;

rx_d1 <= 1'b0;

end

else

begin

rx_d0 <= rx_pin;

rx_d1 <= rx_d0;

end

end

时钟周期计数设计

模块中需要等待固定的时间,比如1个bit、0.5个bit,这里计数一个bit位需要的时钟周期数(从这个方面来看的话,串口是不是用频率高的时钟实现一个频率低的数据,接收数据就是用频率高的时钟去采样、还原数据的过程)。

使用一个16位的寄存器cycle_cnt来进行计数,计数周期根据输入时钟CLK_FRE和波特率BAUD_RATE进行计算即一个bit占用的时钟周期数为CYCLE = CLK_FRE * 1000000 / BAUD_RATE。

复位有效时,寄存器清零。

当状态发生变化时,也进行清零操作。接收数据时需要接收8位,因此在周期到头时也进行清零。

其余时间进行递增即可。

localparam CYCLE = CLK_FRE * 1000000 / BAUD_RATE;

reg[15:0] cycle_cnt; //baud counter

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

cycle_cnt <= 16'd0;

else if((state == S_REC_BYTE && cycle_cnt == CYCLE - 1) || next_state != state)

cycle_cnt <= 16'd0;

else

cycle_cnt <= cycle_cnt + 16'd1;

end

接收位计数设计

接收数据时需要接收特定bit位时才可结束,同时保存数据时也需要知道当前的处理的位数。

由于只有8位,使用一个3位的寄存器进行计数。在接收数据状态时进行计数,当时钟周期数到最大时寄存器递增1,否则保持即可。其余状态为0。

reg[2:0] bit_cnt; //bit counter

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

begin

bit_cnt <= 3'd0;

end

else if(state == S_REC_BYTE)

if(cycle_cnt == CYCLE - 1)

bit_cnt <= bit_cnt + 3'd1;

else

bit_cnt <= bit_cnt;

else

bit_cnt <= 3'd0;

end

数据采样设计

在数据接收状态进行工作,使用一个8bit的寄存器rx_bits来保存采样数据,同时在时钟周期计数的中点进行采样以避免出错。

reg[7:0] rx_bits; //temporary storage of received data

//receive serial data bit data

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

rx_bits <= 8'd0;

else if(state == S_REC_BYTE && cycle_cnt == CYCLE/2 - 1)

rx_bits[bit_cnt] <= rx_pin;

else

rx_bits <= rx_bits;

end

数据输出设计

将采样的数据进行输出,在即将从停止状态转为数据状态时,将数据输出到tx_data寄存器,同时将接收数据有效信号rx_data_valid置为高,告诉后端模块已经有数据。后端读取数据之后要将rx_data_ready拉高一下,使状态机从数据状态退出。

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

rx_data_valid <= 1'b0;

else if(state == S_STOP && next_state != state)

rx_data_valid <= 1'b1;

else if(state == S_DATA && rx_data_ready)

rx_data_valid <= 1'b0;

end

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

rx_data <= 8'd0;

else if(state == S_STOP && next_state != state)

rx_data <= rx_bits;//latch received data

end

状态机设计

算上前面的,应该是三段式的写法。第一段现态,第二段次态,第三段输出。

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

state <= S_IDLE;

else

state <= next_state;

end

always@(*)

begin

case(state)

S_IDLE:

if(rx_negedge)

next_state <= S_START;

else

next_state <= S_IDLE;

S_START:

if(cycle_cnt == CYCLE - 1)//one data cycle

next_state <= S_REC_BYTE;

else

next_state <= S_START;

S_REC_BYTE:

if(cycle_cnt == CYCLE - 1 && bit_cnt == 3'd7) //receive 8bit data

next_state <= S_STOP;

else

next_state <= S_REC_BYTE;

S_STOP:

if(cycle_cnt == CYCLE/2 - 1)//half bit cycle,to avoid missing the next byte receiver

next_state <= S_DATA;

else

next_state <= S_STOP;

S_DATA:

if(rx_data_ready) //data receive complete

next_state <= S_IDLE;

else

next_state <= S_DATA;

default:

next_state <= S_IDLE;

endcase

end

数据发送模块

上电为空闲状态,有数据发送请求进入起始位,起始位结束后进行数据位发送,数据位完毕后发送停止位,停止位发送完毕后进入空闲状态。

时钟周期计数设计

和数据接收一样,数据发送每位的时间也需要精确计数。

数据发送设计

数据只能在空闲状态,或者停止位状态进行发送,是否可以发送数据由信号tx_data_ready决定。该信号表示当前模块是否空闲,是否可以进行数据的发送,在空闲状态且发送数据tx_data_valid无效时为1,或者数据发送停止位后为1。

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

begin

tx_data_ready <= 1'b0;

end

else if(state == S_IDLE)

if(tx_data_valid == 1'b1)

tx_data_ready <= 1'b0;

else

tx_data_read <= 1'b1;

else if(state == S_STOP && cycle_cnt == CYCLE-1

tx_data_ready <= 1'b1;

end

数据锁存模块

在复位时候清零。

在空闲状态且发送数据tx_data_valid 有效的时候,将发送数据锁存到内部寄存器tx_data_latch 。(为什么要在内部使用一个寄存器,是可以提前准备发送的数据吗,流水线?)

reg[7:0] tx_data_latch; //latch data to send

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

begin

tx_data_latch <= 8'd0;

end

else if(state == S_IDLE && tx_data_valid == 1'b1)

tx_data_latch <= tx_data;

end

时钟周期计数设计

和前面接收一样,计数一个波特的时间。在发送状态变化或者需要多次计数的时候进行清零,这里只有发送的时候需要多次计数,其余状态一个bit就够了。

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

cycle_cnt <= 16'd0;

else if((state == S_SEND_BYTE && cycle_cnt == CYCLE - 1) || next_state != state)

cycle_cnt <= 16'd0;

else

cycle_cnt <= cycle_cnt + 16'd1;

end

接收位计数设计

计数bit位数,便于发送。

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

begin

bit_cnt <= 3'd0;

end

else if(state == S_SEND_BYTE)

if(cycle_cnt == CYCLE - 1)

bit_cnt <= bit_cnt + 3'd1;

else

bit_cnt <= bit_cnt;

else

bit_cnt <= 3'd0;

end

数据发送设计

根据状态机的状态输出即可,空闲态或者停止位态输出高,起始位输出低,发送状态根据发送数据进行管脚的状态控制即可,注意这里是从最低位开始的(协议要求),默认状态也为高。

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

tx_reg <= 1'b1;

else

case(state)

S_IDLE,S_STOP:

tx_reg <= 1'b1;

S_START:

tx_reg <= 1'b0;

S_SEND_BYTE:

tx_reg <= tx_data_latch[bit_cnt];

default:

tx_reg <= 1'b1;

endcase

end

状态机设计

和接收差不多,比较简单。

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

state <= S_IDLE;

else

state <= next_state;

end

always@(*)

begin

case(state)

S_IDLE:

if(tx_data_valid == 1'b1)

next_state <= S_START;

else

next_state <= S_IDLE;

S_START:

if(cycle_cnt == CYCLE - 1)

next_state <= S_SEND_BYTE;

else

next_state <= S_START;

S_SEND_BYTE:

if(cycle_cnt == CYCLE - 1 && bit_cnt == 3'd7)

next_state <= S_STOP;

else

next_state <= S_SEND_BYTE;

S_STOP:

if(cycle_cnt == CYCLE - 1)

next_state <= S_IDLE;

else

next_state <= S_STOP;

default:

next_state <= S_IDLE;

endcase

end

数据处理模块

数据处理模块也使用了状态机。

空闲状态比较简单。

发送状态,这里发送的数据是指定数据,并不是串口数据的发送。主要是串口发送模块tx_data_valid和tx_data_ready 信号的处理。在指定的数据发送完之前tx_data_valid一直有效,当tx_data_ready有效的时候,表示可以开始下一个数据的发送,计数加1,等待数据发送完毕后进入等待状态。

等待状态,等待1s,如果有接收数据就把数据在被状态发送回去,1s后转回发送状态。rx_data_valid有效表示接收到一个数据,读取数据到tx_data,设置发送数据信号tx_data_valid有效,当tx_data_valid和tx_data_ready都有效的时候,表示该字节已经发送出去,设置发送数据信号tx_data_valid无效。

always@(posedge sys_clk or negedge rst_n)

begin

if(rst_n == 1'b0)

begin

wait_cnt <= 32'd0;

tx_data <= 8'd0;

state <= IDLE;

tx_cnt <= 8'd0;

tx_data_valid <= 1'b0;

end

else

case(state)

IDLE:

state <= SEND;

SEND:

begin

wait_cnt <= 32'd0;

tx_data <= tx_str;

if(tx_data_valid == 1'b1 && tx_data_ready == 1'b1 && tx_cnt < 8'd12)//Send 12 bytes data

begin

tx_cnt <= tx_cnt + 8'd1; //Send data counter

end

else if(tx_data_valid && tx_data_ready)//last byte sent is complete

begin

tx_cnt <= 8'd0;

tx_data_valid <= 1'b0;

state <= WAIT;

end

else if(~tx_data_valid)

begin

tx_data_valid <= 1'b1;

end

end

WAIT:

begin

wait_cnt <= wait_cnt + 32'd1;

if(rx_data_valid == 1'b1)

begin

tx_data_valid <= 1'b1;

tx_data <= rx_data; // send uart received data

end

else if(tx_data_valid && tx_data_ready)

begin

tx_data_valid <= 1'b0;

end

else if(wait_cnt >= CLK_FRE * 1000000) // wait for 1 second

state <= SEND;

end

default:

state <= IDLE;

endcase

end

实验记录

创建工程,按照前面的详细设计进行编码,生成bit,不再复述。

在线仿真

这里的仿真主要需要模拟一个数据的接收,时钟和数据的延时都由我们控制。

`timescale 1ns / 1ps

module vtf_uart_test;

// Inputs

reg sys_clk_p;

wire sys_clk_n;

reg rst_n;

reg uart_rx;

// Outputs

wire uart_tx;

// Instantiate the Unit Under Test (UUT)

uart_test uut (

.sys_clk_p (sys_clk_p),

.sys_clk_n (sys_clk_n),

.rst_n (rst_n ),

.uart_rx (uart_rx ),

.uart_tx (uart_tx )

);

initial begin

// Initialize Inputs

sys_clk_p = 0;

rst_n = 0;

// Wait 1000 ns for global reset to finish

#100;

rst_n = 1;

// Add stimulus here

#20000;

// $stop;

end

always #2.5 sys_clk_p = ~ sys_clk_p; //5ns一个周期,产生200MHz时钟源

assign sys_clk_n = ~ sys_clk_p;

parameter BPS_115200 = 8680;//每个比特的时间

parameter SEND_DATA = 8'b1010_0011;//要发送的数据

integer i = 0;

initial begin

uart_rx = 1'b1; //bus idle

#1000 uart_rx = 1'b0; //transmit start bit

for (i=0;i<8;i=i+1)

#BPS_115200 uart_rx = SEND_DATA[i]; //transmit data bit

#BPS_115200 uart_rx = 1'b0; //transmit stop bit

#BPS_115200 uart_rx = 1'b1; //bus idle

end

endmodule

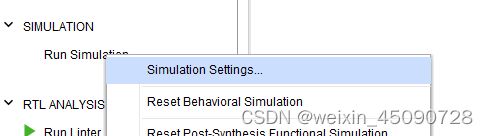

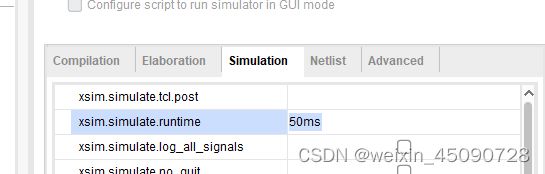

不生成bit的时候也可以进行仿真,点击Run Simulation,也可以右键进行一些设置。

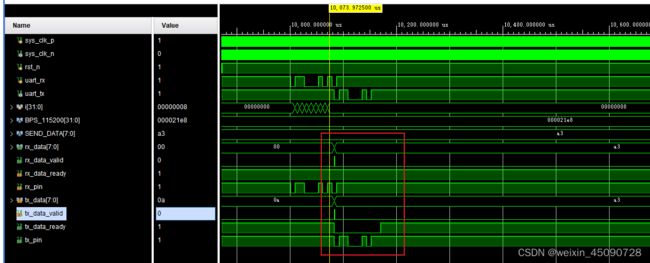

数据发送,发送计数可以看作下一个需要数据,在当前数据进入到串口发送模块就不管了,实际发送了13个。

数据接收,接收数据有效的时候表示有一个数据,但是这里是在数据发送状态,没去处理数据,相当于忽略了。而且这里的接收数据一直是0xa3,应该是因为数据接收模块会锁存一个接收的数据,rx_data是wire型的。

把接收的数据延时一些,与发送状态错过,再次仿真,可以看到数据被发送回去。

上板验证

在线加载,烧写到板子里面。使用串口调试助手可以进行收发数据的测试,这里用putty连接串口看打印信息。串口每秒打印指定的字符串,输入的数据会被接收到。

实验总结

本次实验使用fpga实现串口数据的解析和发送,掌握串口发送的时序。实现的本质是使用高频率的时钟进行采样。

简单使用了软件工程的一些思想,先进行功能的概要和详细设计,根据设计进行编码即可。不过在这里完全是对着源代码去写的,详细设计使用的也是源码,属实是先开枪后画靶。

问题记录

暂无。

TODO

能力暂时不够,后续有时间的话进行解决。

- 三段式状态机怎么写,这里面的时钟是否有差1的问题?

- 串口的发送和接收的控制信号是怎么控制的,连续发送或者接收的数据控制会不会有问题,特别是数据处理模块那里?

- 现在发送和接收都需要前面模块的控制,能不能加上bram,后面直接从bram里面进行读取?

- 添加ILA,在线加载的时候进行抓信号,确认下是否和仿真一致。

- 查找一些关于信号采样与恢复的资料。