国产安路FPGA(三)-FPGA位流文件加密(DNA方式)

使用TD软件对EG4S20BG256芯片进行DNA方式加密

一、设计概述

TD软件版本:TD5.6.1_56362-64bit

工程 :PLL_LED

参考工程 : APUG001_基于 FLASH ID与FPGA DNA的FPGA应用加密(fpga_app_flash_ecy——该部分由安路官方提供,包括使用手册)

二、顶层设计模块

module PLL_LED_DNA(

input clk ,

input rst_n ,

//output reg led,

output Cipher_ok ,

//output LED ,

//M25P16

output SPI_SCK ,

output SPI_nCS ,

output SPI_MOSI ,

input SPI_MISO ,

output SPI_WP ,

output SPI_HOLD

);

wire clk_100MHZ;

wire clk_200MHZ;/*synthesis keep=true*/

wire lock;

wire Rst;

wire [63:0] ecy_key= 64'h0102030405060711;

//assign Rst=!lock;

assign Rst=!rst_cnt[26];

reg [26:0] rst_cnt;

wire Ecy_vld;

wire [63:0] Flash_id;/*synthesis keep=true*/

wire Ecy_over;

wire [63:0] Key;

wire [63:0] Flash_cipher;/*synthesis keep=true*/

wire Flash_en;/*synthesis keep=true*/

wire [3:0] Flash_cmd;

wire [23:0] Flash_addr;

wire [8:0] Flash_len;

flash status

wire Flash_busy;

wire Flash_op_over;

flash rw data

wire Flash_rd_en;

wire [7:0] Flash_rd_dout;

wire Rd_buf_en;

wire [7:0] Flash_rd_buf_din;/*synthesis keep=true*/

/*

always @(posedge clk_100MHZ or negedge rst_n)

begin

if(!rst_n)

led <= 1'd1;

else

led <= 1'd0;

end

*/

always @(posedge clk_200MHZ)

begin

if(lock)

if(rst_cnt[26])

rst_cnt <= rst_cnt;

else

rst_cnt <= rst_cnt+1'b1;

else

rst_cnt <= 27'd0;

end

pll_50MHZ pll_50MHZ(

.refclk (clk),

.reset (!rst_n),

.extlock (lock),

.clk0_out (clk_100MHZ),

.clk1_out (clk_200MHZ)

);

ecydcy_con ecydcy(

.Clk(clk_200MHZ),

.Rst(Rst),

.Ecy_vld(Ecy_vld),

.Flash_id(Flash_id),

.Ecy_over(Ecy_over),

.Key(Key), //ecy_key),

.Ecy_update_en(Ecy_update_en),

.Flash_cipher(Flash_cipher),

.Cipher_ok(Cipher_ok),

master cmd

.Flash_en(Flash_en),

.Flash_cmd(Flash_cmd),

.Flash_addr(Flash_addr),

.Flash_len(Flash_len),

flash status

.Flash_busy(Flash_busy),

.Flash_op_over(Flash_op_over),

flash rw data

.Flash_rd_en(Flash_rd_en),

.Flash_rd_dout(Flash_rd_dout),

.Rd_buf_en(Rd_buf_en),

.Flash_rd_buf_din(Flash_rd_buf_din)

);

key key(

.Clk(clk_200MHZ),

.Rst(Rst),

.Ecy_vld(Ecy_vld),

.Flash_id(Flash_id),

.Ecy_over(Ecy_over),

.Key(Key),

.Ecy_update_en(Ecy_update_en)

);

flash_rw flash

(

.Clk(clk_200MHZ),

.Rst(Rst),

master cmd

.Flash_en(Flash_en),

.Flash_cmd(Flash_cmd),

.Flash_addr(Flash_addr),

.Flash_len(Flash_len),

flash status

.Flash_busy(Flash_busy),

.Flash_op_over(Flash_op_over),

flash rw data

.Flash_rd_en(Flash_rd_en),

.Flash_rd_dout(Flash_rd_dout),

.Rd_buf_en(Rd_buf_en),

.Flash_rd_buf_din(Flash_rd_buf_din),

.SPI_SCK(clk_vld),

.SPI_nCS(SPI_nCS),

.SPI_MOSI_IO0(SPI_MOSI_IO0),

.SPI_MISO_IO1(SPI_MISO_IO1),

.SPI_WP_IO2(SPI_WP_IO2),

.SPI_HOLD_IO3(SPI_HOLD_IO3)

);

endmodule

该部分代码中我是将DEMO中Flash ID和DNA部分直接添加到测试工程中,其中加密号为0102030405060711;

三、根据安路DNA手册(基于 FLASH ID 与 FPGA DNA 的 FPGA 应用加密)

根据安路手册中的操作步骤,需要将TD软件中生成的BIN文件的起始地址进行更改,即将key秘钥进行输入,且仅有64位;

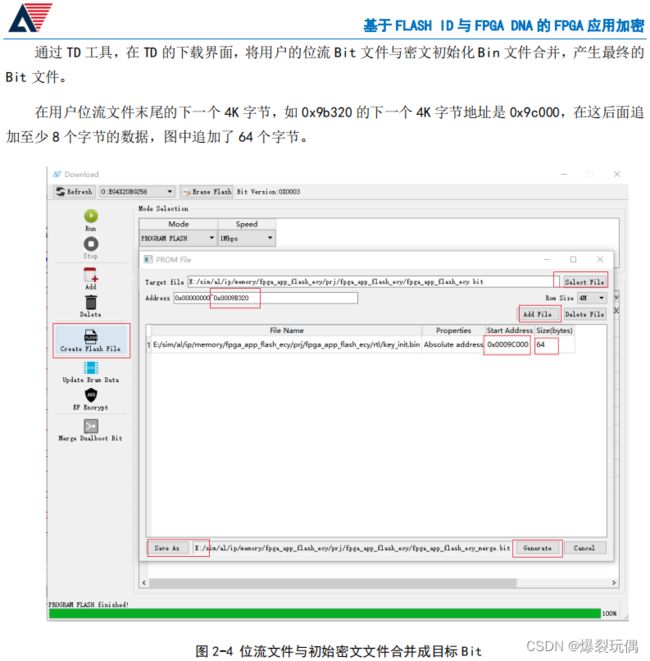

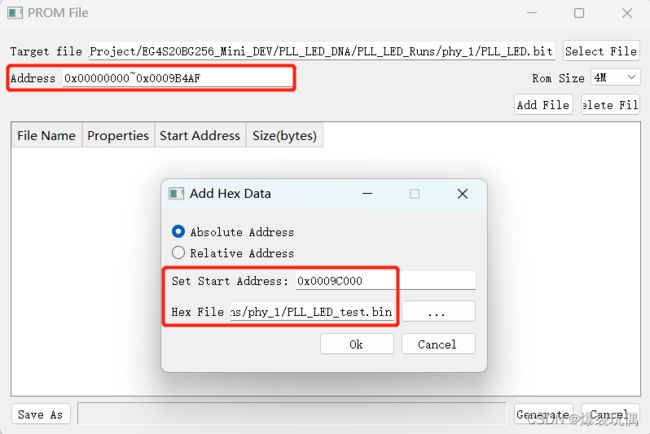

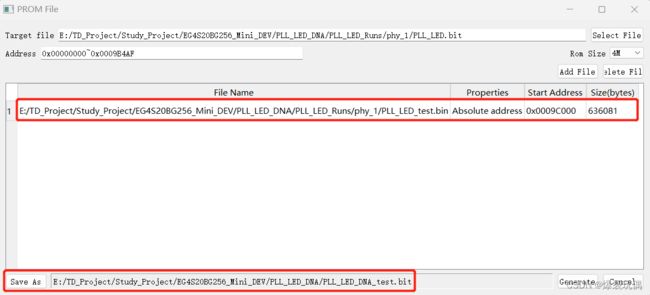

在TD软件中点击Create Flash File后可以对已经生成的bit文件进行合并,在该界面中Address为正常位流文件的地址大小,通过Add File后,需要将刚刚加入秘钥的bin文件添加,同时将Flash地址进行扩展,即Address为0X0009B320,把flash按照4K为单位进行划分,所以起始地址应该以4K进行扩充,即起始地址变为0X0009C000;

然后可以根据读取Flash的结果观察Flash秘钥是否写入,并且符合预期;

四、实测结果

1. 实测步骤1

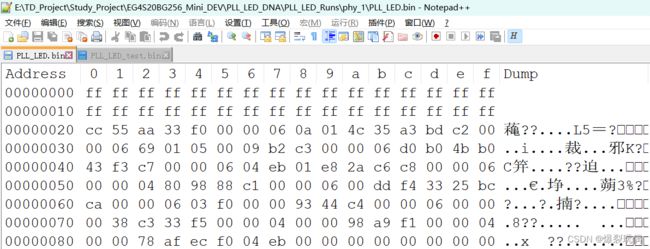

(1)BIN文件中添加秘钥,采用Notepad++进行二进制查看,但目前未找到能够一次性复制秘钥粘贴的方式,只能一个一个输入;

原BIN文件:

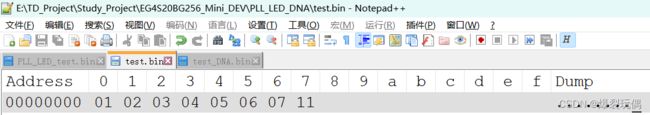

添加秘钥后的BIN文件:

2. 实测步骤2

- 添加正常的bit流文件

- 根据地址做出余量

- 添加已经加好秘钥的BIN文件

并将bit文件和bin文件合并后的bit文件进行存储,选择存储路径,并将该合并后的bit文件以Program Flash的方式固化进板卡中

固化完成之后,需要对板卡进行断电重启后,在进行Flash文件的回读,操作如下:

3. 实测步骤3

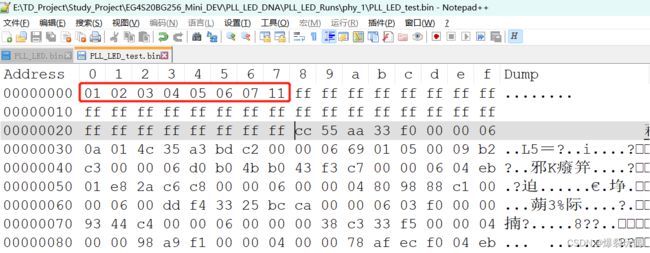

回读的Flash文件以bin文件的形式进行显示,并采用二进制的方式进行查看,可以看到首地址的前64bit的数据为0102030405060711,即为秘钥;此时FPGA bit文件的加密已经完成;后续将会研究EF2L等系列的AES加密方式