【计算机组成原理】流水线式指令执行

文章目录

- 前言

- 一、处理器的构成

- 二、数据通路

-

- 1. 流水线工作

- 2. 冒险

- 3. 流水线寄存器

- 三、FPGA相比于CPU的速度优势

- 总结

前言

最近在阅读《计算机组成与设计 硬件/软件接口(原书第5版)》这本书,它的讲解由浅入深,对计算机底层的硬软件进行了详细介绍,内容清晰且层次分明,是可以反复阅读的计算机书籍。

这一版的《计算机组成与设计》是基于目前最火的开源指令集RISC-V编写的,也是与时俱进了。

本文的内容是该书第4章——处理器 的提炼。书中对于流水线的指令执行方式介绍的很清楚,我这里只是根据自己的理解简要记录了核心内容,推荐大家有时间阅读原文==

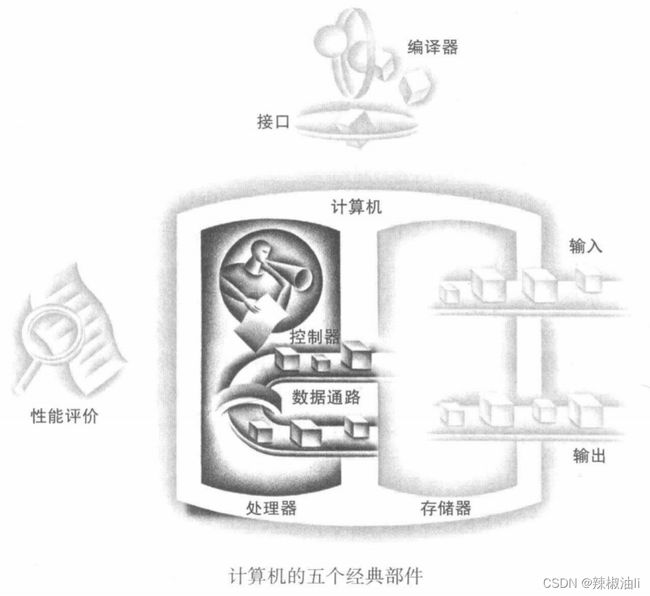

一、处理器的构成

处理器由数据通路和控制器构成。

数据通路负责取指令、计算数据、存取数据,它使用了指令存储器、数据存储器、通用寄存器、多路选择器以及ALU(算数逻辑单元)。

其中ALU是用来执行加减与或计算的模块。

数据存储器和指令存储器都属于内存,通用寄存器用来放置指令执行过程中需要使用的数及产生的数。多路选择器是为了能在一条数据通路中完成多种指令的执行而采用的硬件。

这张图片很重要,把计算机的五个基本部件之间的关系刻画得很清楚,它在书中也反复出现。

控制器负责译码,即根据指令(32位二进制串)生成ALU、多路选择器的相关控制信号以及存储器的读写信号。控制信号可由组合逻辑生成。

二、数据通路

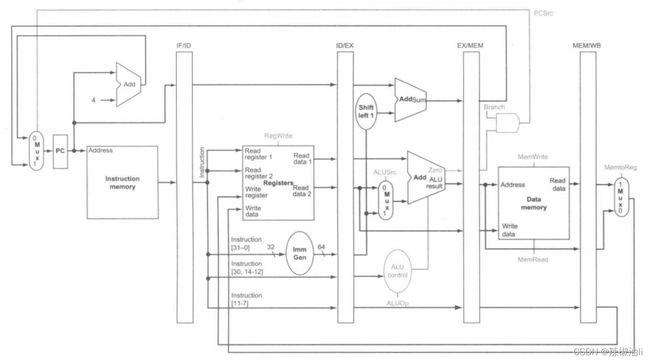

一条能完成存取指令以及算数指令、分支指令的数据通路如下图所示:

ps:上面这张图中没有画出控制器

可以看到它分成了五个部分:取指,译码及读寄存器堆,执行,存储器访问,写回。

每条指令都必须经历这五个步骤,尽管可能在某个步骤中不需要做任何事情。 比如对于加载指令,在“写回”这一步中不需要有任何动作。

这样设计是为了方便流水线式执行指令。

在编写RISCV处理器核时可以按照流水线的每个步骤来编写对应的硬件控制逻辑。

下面这张图是加入了控制器后的完整数据通路(浅色的线代表了控制信号的流动),可以看出控制信号在ALU、多路选择器等部分都起到了作用。

1. 流水线工作

若不采用流水线,就会执行完一个指令再去执行下一条指令,若执行一条指令需要n个时钟周期,那么执行完m条指令就需要m*n个时钟周期。

现在我们在第一个时钟周期内令第一条指令在执行上图中第二个步骤,同时令第二条指令执行第一个步骤;在第二个时钟周期内,令第一条指令执行第三个步骤,第二条指令执行第二个步骤,第三条指令执行第一个步骤。如下图所示,就像工厂中的流水线生产一样,指令需要经过五个连续车间才能完成最终的执行,我们在输入端按时钟周期把一条条指令放进去,在输出端就会在每个时钟周期都有成品(执行结果)出来。这样平均算下来每条指令执行所需的执行时间只有一个时钟周期,即CPI=1。流水线过程如下图所示:

2. 冒险

流水线式的指令执行中会存在冒险的问题,包括

- 结构冒险:指硬件水平不支持流水线操作;

- 数据冒险:指因无法提供指令所需数据而使得后面的指令无法在预期的时钟周期内执行,如上一条指令的“写回”结果需要在下一条指令“执行”中使用;

- 控制冒险:也称分支冒险,由于取到的指令不是所需要的,或指令地址的流向不是代码所预期的,导致正确的指令无法在正确的时钟周期中执行,产生于分支指令出现的时候。

书中对每种冒险都进行了详细的解释,并给出了相应的解决方案,比如针对控制冒险提出了动态分支预测。在需要时可以翻阅该书寻找答案。

3. 流水线寄存器

在流水线中,为了使一条指令的执行所需数据在该流水线处理下一个指令时不丢失,我们需要在每两个步骤中间都增加一个寄存器用来保存当前指令该步骤的相关数据。称这些寄存器为流水线寄存器,即下图表示的数据通路中染色的部分:

三、FPGA相比于CPU的速度优势

在了解了处理器的流水线式指令执行后,我产生一个疑问,处理器和FPGA同样具有流水线执行的能力,为什么FPGA的速度要比CPU快很多呢?

这里面有个盲点,原因其实也很简单,因为FPGA没有指令。

CPU虽然可以有流水线执行指令,但是ALU的运算还是串行的,需要一个一个数据地计算。

然而FPGA不需指令,通过逻辑编写直接实现了确定功能的计算模块(相当于ALU),并且这个计算模块可以采用流水线的方式运行,所以计算速度很高,平均下来可以做到一个时钟周期算出一个数据。

因此FPGA在运算方面比CPU快。

下面是某篇博客的说法,可供参考。(原文不记得在哪里了,下面是之前复制出来的部分内容)

CPU和GPU都属于冯·诺依曼结构,指令译码执行,共享内存。FPGA之所以比CPU、GPU更快,本质上是因为其无指令,无共享内存的体系结构所决定的。

冯氏结构中,由于执行单元可能执行任意指令,就需要有指令存储器、译码器、各种指令的运算器、分支跳转处理逻辑。而FPGA的每个逻辑单元的功能在重编程时就已经确定,不需要指令。CPU虽然可以有流水线执行指令,但是ALU的运算还是串行的,一个一个数据地计算。然而FPGA不需指令,直接实现了确定功能的计算模块(相当于ALU),并且这个计算模块可以采用流水线的方式运行,所以计算速度很高,平均下来可以做到一个时钟周期算出一个数据。

在数据中心,FPGA相比GPU的核心优势在于延迟。FPGA为什么比GPU的延迟低很多?本质上是体系结构的区别。FPGA同时拥有流水线并行和数据并行,而GPU几乎只有数据并行(流水线深度受限)。

处理一个数据包有10个步骤,FPGA可以搭建一个10级流水线,流水线的不同级在处理不同的数据包,每个数据包流经10级之后处理完成。每个处理完成的数据包可以马上输出。而GPU的数据并行方法是做10个计算单元,每个计算单元也在处理不同的数据包,但是所有的计算单元必须按照统一的步调,做相同的事情(SIMD,单指令流多数据流运行)。这就要求10个数据包必须同进同出。当任务是逐个而非成批到达的时候,流水线并行比数据并行可实现更低的延迟。

因此对流水式计算的任务,FPGA比GPU天生有延迟方面的优势。

缺少指令同时是 FPGA 的优势和软肋。每做一点不同的事情,就要占用一定的 FPGA 逻辑资源。如果要做的事情复杂、重复性不强,就会占用大量的逻辑资源,其中的大部分处于闲置状态。这时就不如用冯·诺依曼结构的处理器。FPGA 和CPU协同工作,局部性和重复性强的归FPGA,复杂的归 CPU。

总结

理解作者所说的数据通路,对于理解处理器指令执行的方式是十分重要的。

一条硬件组成确定的数据通路,通过控制器的控制可以完成多类指令的执行。

相关文章:

【计算机组成原理】层次存储结构(一)

【计算机组成原理】层次存储结构(二)