从版图到原理图

一、图像采集和处理

高质量的芯片图像是进行芯片分析设计的基础。随着芯片特征尺寸减小、规模增大、金属层数增多,芯片反向分析时对于芯片图像的完整性和清晰度的要求也越来越高。

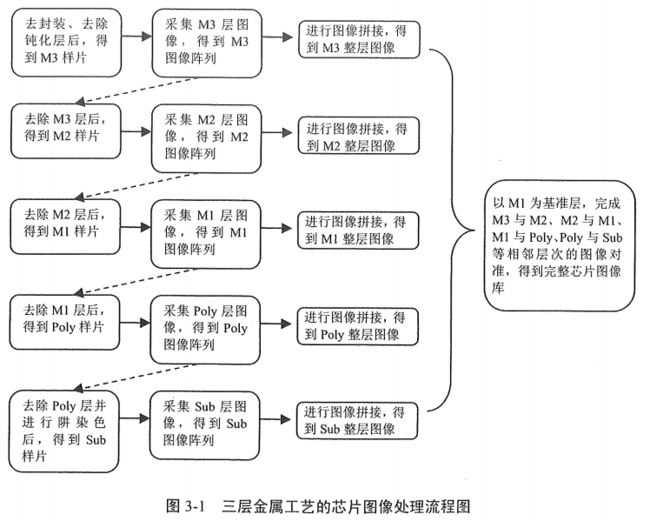

芯片图像库的建立是一个较为复杂的过程,其核心步骤是同层图像拼接和邻层图像对准。在一定放大倍数下进行显微图像采集时,每幅图像均对应一个特定的芯片区域。对解剖后的某层次芯片进行连续图像采集后,通常可以得到一个若干行列的图像阵列。将图像阵列进行同层图像拼接,就可形成该芯片解剖层次的整层图像。按照芯片版图的对应关系,可以进一步将任意两个相邻层次的整层图像进行邻层图像对准。经过上述逐层图像拼接、邻层图像对准,就可以得到完整的芯片图像数据库。

以图3-1所示的三层金属工艺芯片为例。进行芯片逐层解剖和阱染色后,可以先后得到金属三层(M3)、金属二层(M2)、金属一层(M1)、多晶硅层(Poly)和染色层 (Sub)等5个层次的芯片解剖样片。

为方便叙述,本文后续章节中一律以Mi、Poly、Sub代表上述图像层名称。对每个芯片样片进行图像拍摄,对拍摄得到的单层图像阵列进行同层图像拼接,可以得到每个解剖层次的整层图像;先后完成4次邻层图像对准(M3与M2对准、M2与MI对准、M1与Poly对准、Poly与Sub对准),就可以得到最终的芯片图像数据库。在具体进行图像拼接前,还需要对拍摄后的所有单幅芯片图像进行一系列图像预处理,这些图像预处理包括图像变形纠正、图像倾角纠正、图像翻转、图像色彩和亮度调整等。

不同芯片层次的图像采集,有时会用不同的放大倍率,而在进行邻层图像对准时要求必须具有相同的放大倍率,此时就需要对某层图像进行缩放(通常是放大)。例如,某芯片的Sub层(阱染色层)采用500倍拍摄,而Poly层采用1000倍拍摄,在进行Sub层与Poly层的图像对准时,需要将Sub层图像由500倍光学图像放大为1000倍效果,此时缩放因子就等于2。此时的放大实际上是“虚放大”,即图像尺寸虽然放大了,但图像清晰度仍然为500倍效果。事实上,显微镜是存在拍摄倍数误差的,图像拍摄效果并不严格等于设定的拍摄倍数,而且不同显微镜的拍摄误差也是不同的。例如,显微镜A的500倍拍摄效果相当于499.6倍,而显微镜B的1000倍拍摄效果相当于1000.3倍,此时的实际缩放因子就约为2.002倍。在进行图像缩放时,往往需要精确测量邻层图像中对应点的像素点距离,将其比值作为缩放因子。

二、芯片解剖及工艺分析

半导体器件制作过程可分为前工序和后工序。从晶圆开始,经过多次的制膜、氧化、扩散、掺杂、刻蚀等工艺步骤,在晶圆上制作成集成电路元件阵列,再将晶圆切割成一个个矩形的管芯,这就是前工序的过程。后工序是进行装片、固定、键合连接、塑料灌封、引出接线端子等工序,将管芯制作成为封装后芯片的过程。无论从技术实现上还是流程上,前工序都比后工序要复杂得多,因此有时也会将芯片的制造工艺仅定义为前工序所对应的内容。

1、薄膜沉积

半导体器件是由材质厚度不同的多层薄膜,经过多次光刻、刻蚀等工艺后而形成的。将这些薄膜覆盖在晶圆上的技术,便是薄膜沉积(thin film deposition)工艺。半导体器件的薄膜主要包括钩、氨化钛等导体,多晶硅和单晶硅等半导体,以及二氧化硅、氮化硅、磷硅玻璃等介质材料。薄膜沉积技术从早期的蒸镀开始至今,已经发展成两个主要方向:物理气相沉积(physical vapor deposition, PVD)和化相沉积(chemical vapor deposition, CVD),两者分别以物理作用和化学反应为主来实现薄膜沉积。物理气相沉积主要应用于金属薄膜的沉积,主要有蒸镀(evaporation)和溅射(sputtering)两种。其中蒸镀是利用被蒸镀材料在高温时所具备的饱和蒸汽压来进行薄膜沉积的;在溅射过程中,靶材中的原子被荷能离子轰击而溅射出来并沉淀在基片化学气相沉积是利用相关化学反应在特定条件下将反应气体转化为固态生成物,并沉积在晶圆表面的技术。目前,化学气相沉积已经成为半导体工艺中的主要薄膜沉积技术,几乎所有的半导体器件薄膜都可以通过化学气相沉积方法制造 。

2、光刻

光刻工艺是通过光刻胶的显影、定影等操作,把掩膜版上的图形转换到硅平面上,的过程。光刻工艺在半导体制造技术中有着举足轻重的作用,凡是与MOS器件相关的结构,如各层膜结构、掺杂区域,都是光刻工艺实现的。因此工艺的复杂程度通常以光刻次数或者掩膜版数量来表示。集成电路生产线的工艺能力通常也是以能够刻蚀的最小图形的宽度来评定的。光刻工艺比较复杂,但是其基本原理却很简单。

①首先是在晶圆表面覆盖一层光刻胶(感光材料),然后在晶圆上覆盖掩膜版,再利用特定光源(通常是紫外线)进行照射,此时晶圆表面未被掩膜版阻挡的光刻胶就会感光,此后再经过显影和定影就可以把光刻胶感光的部分去掉,这样就把掩膜版中的图案完全转移到光刻胶上了。

②通过对晶圆进行刻蚀或离子注入就可以进一步将光刻胶上的图案转移到硅平面上。

光刻工艺所需要的材料主要包括光源、掩膜版、光刻胶和显影液等。光刻的基本工艺是由光刻胶覆盖、曝光和显影等三大步骤完成。为了加强图案传递的精确性和可靠性,整个光刻的过程还包括去水烘烤、软烤和硬烤等步骤。

3、蚀刻

刻蚀是把没有被光刻胶覆盖的沉积薄膜部分,以化学反应或物理作用的方式加以去除的过程。通过刻蚀可以将掩膜版上的图形转移到薄膜上。换句话说,掩膜版上的图案,通过光刻工艺转移到光刻胶上后,利用刻蚀工艺可以进一步转移到薄膜上。这层薄膜可能是二氧化硅、氢化硅、多晶、铝合金或是硼磷硅玻璃等。目前广泛应用在半导体工艺上的刻蚀技术主要有两种,即湿法刻蚀(wet etching)和干法刻蚀(dry etching)。前一种刻蚀方法是利用化学反应来进行刻蚀,呈各向同性特性;而后一种则主要是利用等离子刻蚀机来完成,呈各向异性特性。这两种刻蚀方法将在本章后续内容中加以介绍。

4、 掺杂

掺杂是在半导体中加入少量特定杂质的过程。半导体器件中的有源区、阱区等结构都是通过掺杂来实现的。集成电路制造工艺中的参杂技术主要有两种,一种是传统的扩散法(diffusion), 另一种是较为先进的离子注入法(ion implantation)。扩散法是通过高温下的扩散作用,将杂质从材质中的高浓度区域向低浓度区域移动来进行掺杂;而离子注入法则是借助离子注入机将杂质以离子的形式直接注入到硅材质内来进行掺杂,通过控制离子注入的深度和浓度,达到改变导电特性的目的。两种掺杂方法的原理不同,但其目的都是对半导体进行杂质掺入,改变掺杂区域的导电性,形成P型或N型的半导体区域 。

参考:硼和磷的扩散原理与工艺

5、氧化

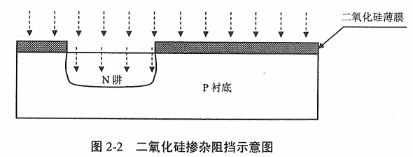

氧化是按照厚度要求在硅表面生长一层均匀无缺陷的二氧化硅薄膜的工艺过程。在集成电路制造技术中,氧化工艺占有重要的地位。利用二氧化硅的屏蔽作用实现选择区域的扩散掺杂,是20世纪50年代以来集成电路制造技术最重要的技术发展之二氧化硅薄膜的产生可通过热生长和淀积等两种方式实现。热生长也称为湿氧氧化,是指在高温环境中通过外部供给氧气或水蒸汽,使之与硅衬底发生氧化反应生成二氧化硅薄膜的过程,其特点是薄膜生长速度快,膜质疏松。淀积也称为干氧氧化,当外部供给的氧气和硅源在腔体中反应,可以在硅表面形成一层二氧化硅薄膜,其特点是生长速度慢,膜质致密。二氧化硅薄膜是集成电路制造中应用最为普遍的膜材料,在半导体制造工艺中它有如下重要应用。

(1)器件保护和隔离。二氧化硅是一种坚硬而致密的材料,可以有效避免制造过程中划伤和损坏。通过生长一层厚的二氧化硅还可以实现器件之间的隔离。在0.25m以下的工艺中,为了更有效地隔离器件,通常会采用填充二氧化硅的浅沟槽工艺进行器件之间的隔离。

(2)掺杂阻挡。P+或B3+等物质在二氧化硅中的扩散速度远远低于其在硅衬底中的扩散速度,因此二氧化硅可作为掺杂的阻挡层。在需要掺杂的地方通过刻蚀去除二氧化硅以形成掺杂窗口,掺杂材料可以通过此窗口进入硅衬底进行扩散,而表面覆盖二氧化硅的地方,掺杂材料很难渗透,因此二氧化硅起到阻挡掺杂的作用。图2-2为二氧化硅掺杂阻挡示意图

(3)制作棚氧的材料。在MOS器件的多晶栅下面常用二氧化硅制作一层很薄的栅氧层。栅氧通常采用干氧方式制作,要求质量高、致密均匀、无杂质。

(4)金属层之间的介质层。二氧化硅是很好的绝缘体,可以用来制作金属层之间的绝缘层。金属层之间的二氧化硅通常采用气相沉淀的方式制作。

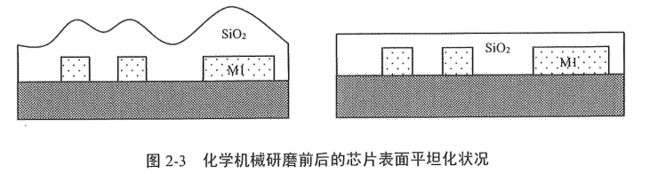

6、化学机械研磨

利用表面布满研磨颗粒的研磨垫和特定的化学研磨液,以化学反应和机械研磨相结合的方式对芯片表面进行平坦化加工,这个过程就是化学机械研磨(chemicalmechanical polish, CMP)。在集成电路制造中,随着场氧化层、CMOS晶体管、金属层等结构的产生,晶圆的表面也逐渐变得凸凹不平,这将严重影响薄膜沉积、光刻、刻蚀等工艺的效果。对薄膜沉积工艺来说,晶圆表面平坦性越差,沉积薄膜的台阶覆盖能力就越差;在光刻过程中,受光刻机聚焦深度的限制,晶圆表面高低起伏越剧烈,图形转移的过程也就越困难、越容易失真;而在刻蚀工艺中,为了弥补晶圆表面的起伏,必须强化刻蚀的程度,但过度刻蚀又容易造成线路断裂、通孔接触不良等问题。IBM公司从20世纪80年代开始研发化学机械研磨技术,并于90年代初期将其应用在实际生产中。由于这项技术是集成电路制造业界唯一且必须依赖的平坦化工艺,因此一经IBM公布其可行性之后,全球各大半导体厂商,无不倾尽全力开发这项技术,以便维持自己产品的竞争力。图2-3显示了化学机械研磨操作前后的效果图。

典型工艺组合

随着芯片上晶体管的集成度越来越高,器件尺寸以及器件之间距离都越来越小。这种减小趋势达到某一程度后,各种因尺寸减小所衍生的问题就会发生,使集成电路性能下降甚至功能丧失。因此集成电路制造商研发了一些先进的工艺组合来克服和解决这些衍生问题。下面选择几种典型的工艺组合进行介绍。

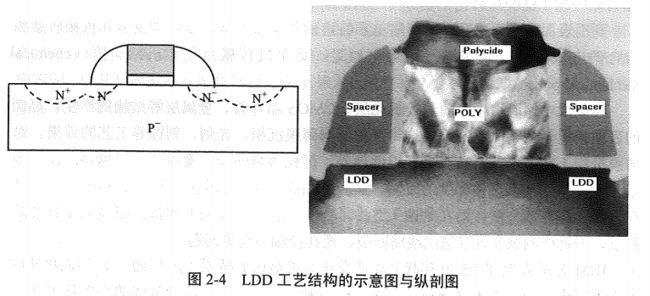

1.轻掺杂漏极工艺

轻掺杂漏极(lightly doped drain, LDD)工艺在MOS管源极和漏极位置处进行轻掺杂。通过LDD设计, NMOS沟道内的电场分布将向漏极移动,并且电场强度也有所减小,因此可以在很大程度上解决次开启电流、短沟道效应和载流子倍增效应等所带来的MOS器件功能和性能影响。图2-4显示了LDD工艺结构的示意图与透射电子显微镜拍摄的纵剖图。