触发器建立时间和保持时间的关系(含题目详解)

参考文献:

建立时间和保持时间关系详解 - Lilto - 博客园 (cnblogs.com)

建立时间、保持时间、传播延时、组合逻辑延时都是什么呢?_weixin_34402090的博客-CSDN博客

一、定义

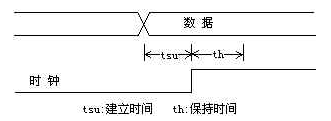

1、建立时间(setup time)

指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;

- 如果不满足建立时间要求,这个数据就不能被这一时钟打入触发器,只有在下一个时钟上升沿,数据才能被打入触发器,或者说,该数据就会被永久“跳过”而未被“采样”。

- 如果数据信号在时钟沿触发前的持续时间超过了建立时间,那么这个时间间隔就叫做建立时间裕量。

- 举个例子:坐火车时需要提前到站检票安检,而不是一到火车站就可以乘坐。必须的提前到站的时间就是建立时间。

2、保持时间(hold time)

指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器。

- 如果数据信号在时钟沿触发后的持续时间超过了保持时间 Th,那么这个时间间隔就叫做保持时间裕量。

从延迟的角度来说,

- 建立时间决定了该触发器之间的组合逻辑的最大延迟。

- 保持时间决定了该触发器之间的组合逻辑的最小延迟。

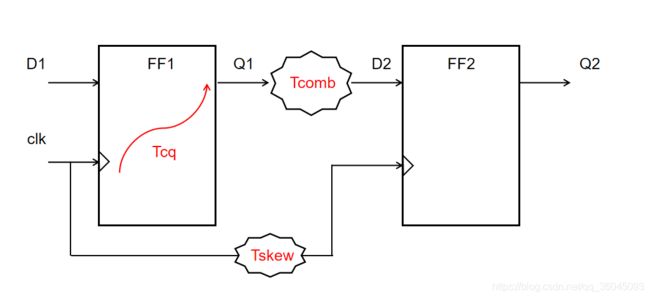

3、传播延时(触发器输出的响应时间)

是指一个数字信号从器件(一般是 DFF,符号表示为 Tcq / Tco)的输入端到输出端所需的时间。一般在 FPGA 中是指时钟上升沿之后延时 Tcq 的时间,数据才到达寄存器 Q端。

区别于门传播延时:反应为其对输入信号变化响应有多快,表示为信号通过该门所经历的时间,定义为输入信号和输出信号波形在 50% 翻转点之间的时间。

4、组合逻辑延时

一般是指两级寄存器之间的输出端 Q 到输入端 D 之间的组合逻辑延时,符号表示为 Tlogic / Tcomb。

二、关于建立时间和保持时间的约束

华为题目:

时钟周期为T,触发器D1的建立时间最大为T1max,最小为T1min。组合逻辑电路最大延迟为T2max,最小为T2min。问:触发器D2的建立时间T3和保持时间T4应满足什么条件?

分析:建立时间容限(建立时间裕量)≥0;保持时间容限(保持时间裕量)≥0

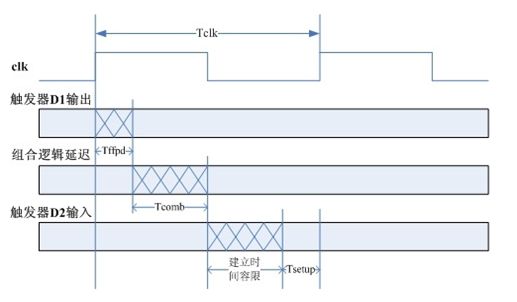

1、建立时间的约束

建立时间约束条件: clk上升沿到来之前,数据需要保持稳定一定时间

建立时间容限=Tclk - Tcq - Tcomb - Tsetup ≥ 0 ;→ Tclk - Tcq - Tcomb - Tsetup ≥ 0; →

即Tclk - Tcq(max) - Tcomb(max) - Tsetup ≥ 0; (取max是为了获得可能出现的最小的Tclk的值,也是能出现的最大的建立时间容限)

Tsetup ≤ Tclk - Tcq(max) - Tcomb(max)

由于题目没有考虑Tcq,则Tcq = 0; 那么Tsetup ≤ Tclk - Tcomb(max) = T - T2max;

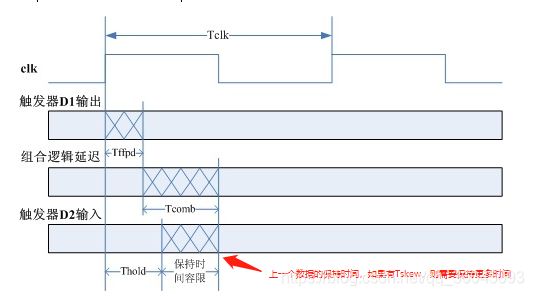

2、保持时间的约束

保持时间约束条件:clk上升沿到来之后,数据需要保持稳定一定时间

Tcq + Tcomb = Thold + 保持时间容限 →

保持时间容限 = Tcq + Tcomb - Thold ≥ 0 →

Thold ≤ Tcq(min) + Tcomb(min)

即Thold ≤ Tcomb(min) = T2(min);

无skew:

Tsetup ≤ Tclk - Tcq(max) - Tcomb(max);

Thold ≤ Tcq + Tcomb;

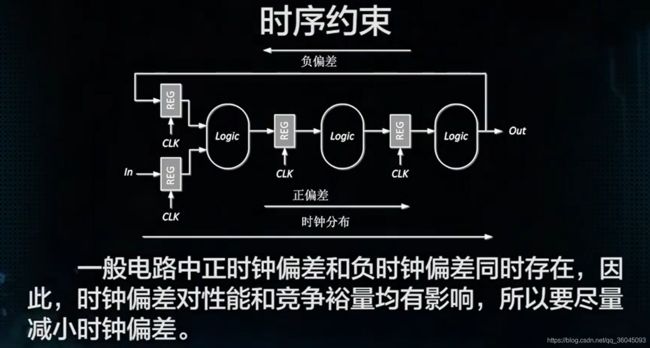

有skew:

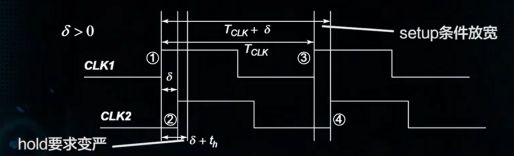

①正时钟偏差(Tskew > 0)

Tsetup + Tcq + Tcomb≤ Tclk + Tskew ,即Tsetup ≤ Tclk + Tskew - Tcq(max) - Tcomb(max);

Thold ≤ Tcq + Tcomb - Tskew;(因为CLK2的时钟来的比CLK1晚,采样时间会更紧张,对Thold要求更严格)

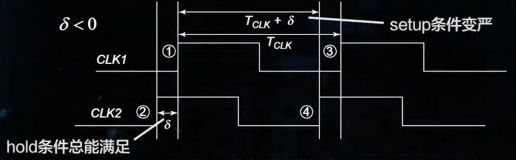

②负时钟偏差(Tskew < 0)

因为CLK2超前,②采集不到数据,由采样边沿④来采集,那么②处的Thold裕量就会很大。

三、习题

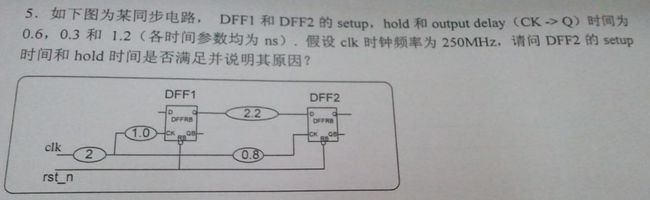

【全志科技笔试题】

分析:

由题知:Tsetup = 0.6ns, Thold = 0.3 ns, Tcq = 1.2ns, Tclk = 4 ns,

由图知:Tcomb = 2.2ns,Tskew = -0.2 ns;

建立时间约束公式:T1cq + Tcomb + T2setup ≤ Tclk + Tskew ;

保持时间约束公式:T1cq + Tcomb ≤ Thold + Tskew;

解答:

①建立时间应满足:Clk_delay_FF2(0.8ns) + Tclk ≥ Clk_delay_FF1(1ns) + T1cq + Tcomb + T2setup,

则0.8 + 4 ≥ 1 + 1.2 + 2.2 + 0.6, 则4.8ns ≥ 5ns,上式不成立,即T2setup过大,建立时间不满足要求;

或:

约束要求的T2setup ≤ Tclk + Tskew(= Clk_delay_FF2 - Clk_delay_FF1 = -0.2 ns) - T1cq - Tcomb = 4 + (-0.2)- 1.2 - 2.2 = 0.4ns<器件实际的0.6ns,建立时间不满足要求

②保持时间应满足:Clk_delay_FF2(0.8ns) + T2hold ≤ Clk_delay_FF1(1ns) + T1cq + Tcomb,

则0.8 + 0.3 ≤ 1 + 1.2 + 2.2,则1.1ns ≤ 4.4ns,上式成立,保持时间满足要求(裕量为3.3ns);

或:

约束要求的T2hold ≤ T1cq + Tcomb - Tskew(= Clk_delay_FF2 - Clk_delay_FF1 = - 0.2 ns) = 1.2 + 2.2 - (-0.2) = 3.6ns >器件实际的0.3ns(裕量为3.3ns)