【DRAM存储器十一】SDRAM介绍-各类读操作详解,附带解释了几个重要时序参数

个人主页:highman110

作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容

参考资料:《镁光SDRAM数据手册》、《PC SDRAM specification》

目录

读操作

Consecutive READ Bursts

Random READ Accesses

Read Terminated By Read

Read Terminated By Write

Read Terminated By Precharge

Read Terminated By BURST TERMINATE

Alternating Bank Read Accesses

READ Continuous Page Burst

之前三篇文章介绍的是SDRAM的基础命令或功能,接下来继续介绍基于这些命令的一些常用读写操作,比如读操作,就有连续突发读、随机读、读带不带预充电、突发读被截断、读后面跟着写等等一系列使用情况。

读操作

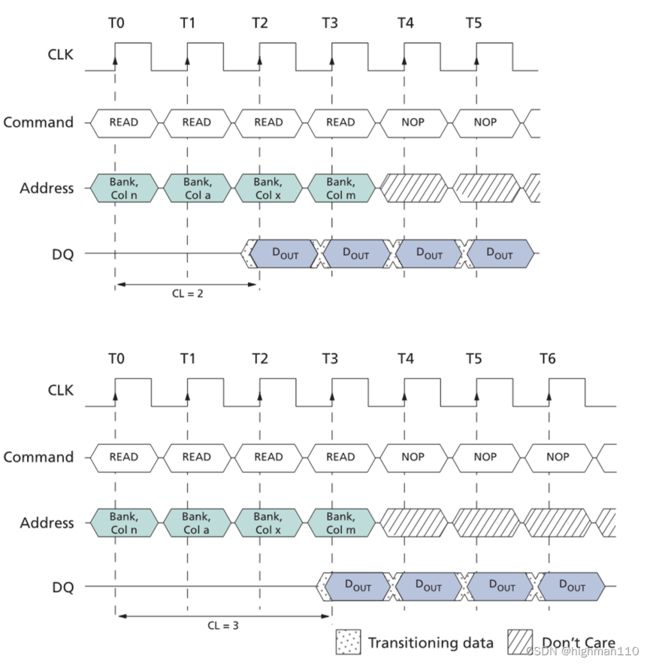

Consecutive READ Bursts

如下图例,在同一行内,只要重新下读命令和列地址,就可以连续突发读,下发第二个读命令的时机为前一次突发最后一个数据周期的前X个时钟周期,其中X=CL-1,说白了就是在满足CL时间的前提下,使前后突发的两笔数据连续上。

Random READ Accesses

如下图例,随机读就是一次只输出一个列地址的数据,每次读命令更改列地址。

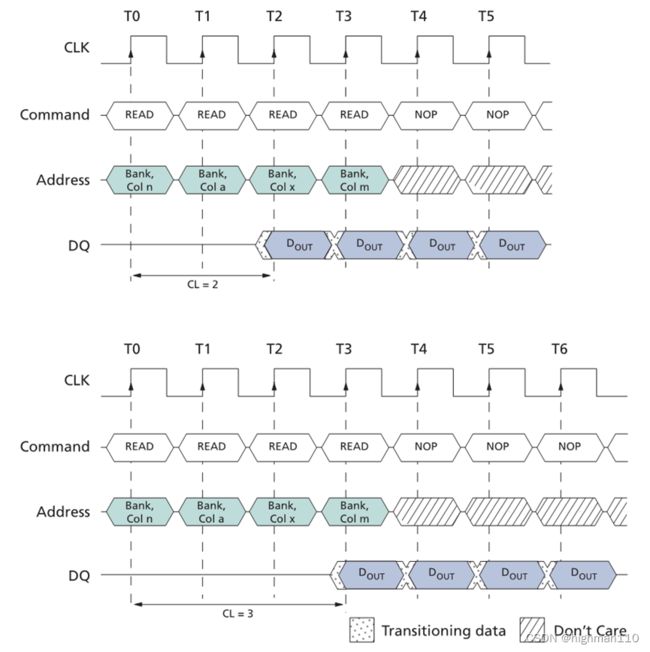

Read Terminated By Read

如下图例,先是激活了bank0的某行(这个在图里没画出来),经过trcd(RAS to CAS delay,行选通周期)后发出不带预充电的读命令和列地址,再经过CL(CAS latency,CAS潜伏期,又称RL,read latency,读潜伏期)后在时钟上升沿发出数据。

任何读突发的数据可以被随后的读命令截断,并且新的读命令的数据会紧接着上一次被截断的数据发送。这使得在任何一种情况下,都可以保持连续的数据流。来自新突发的第一个数据要么紧跟着上一次完整突发数据,要么就紧跟着上一次被截断的最后一个数据,这就要求新的读命令应在最后一个所需数据元素有效的时钟沿之前x个周期发出,其中x=CL-1。这句话读起来拗口,大家看如下两张CL=2和CL=3的例子的图就比较好理解。

在突发完成时,假设没有其他命令被启动,DQ信号将进入高阻状态。突发过程可以被其他命令截断。突发到页面末尾但还小于突发长度时,它会切换到第0列并继续输出数据。

连续突发读

随机读

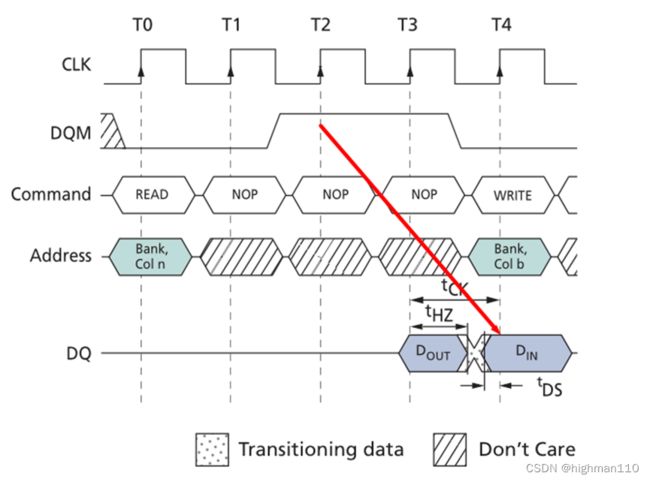

Read Terminated By Write

同理,任何读突发的数据也可以被随后的写命令截断,但是与读命令截断读命令不同的是,读输出和写输入需要避免I/O争用。如前面的DQM功能章节所述,DQM输入用于可避免I/O争用。DQM信号必须在写命令之前至少两个时钟被拉高,以抑制从读数据的输出。另外,DQM需要在写命令生效时提前拉低,否则输入数据会被屏蔽。如下图所示:

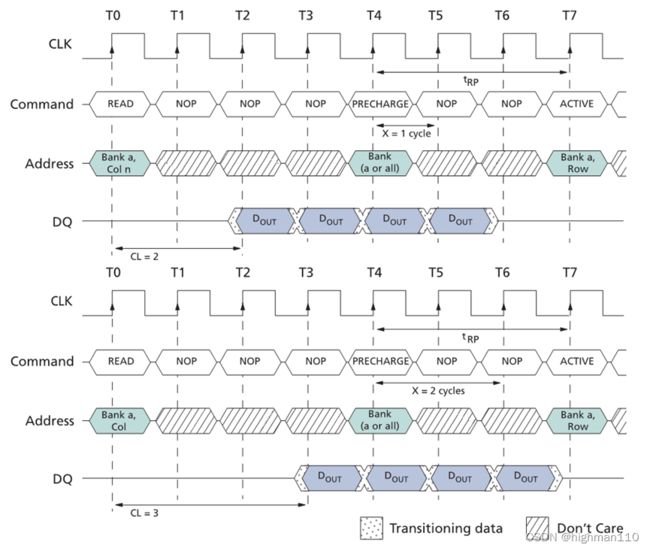

Read Terminated By Precharge

如果一个固定突发长度的读操作不带自动预充电,则该读操作可以被同一个bank的预充电命令截断。PRECHARGE命令应在最后一个所需数据元素有效的时钟沿之前x个周期发出,其中x=CL-1。在PRECHARGE命令之后,在满足tRP之前,不能向同一bank发出后续命令。PRECHARGE命令的缺点是它要求命令和地址总线在适当的时间可用以发出命令。PRECHARGE命令的优点在于,它可以用于截断固定长度或连续的页面突发。

Read Terminated By BURST TERMINATE

镁光这颗256Mb的SDRAM颗粒还支持一个BURST TERMINATE命令用来截断读突发,这个效果和预充电差不多,发命令的时机要求也和预充电截断一样。如下图所示:

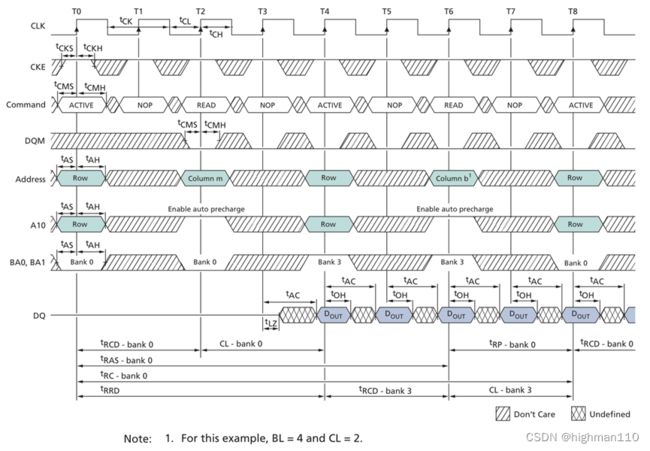

Alternating Bank Read Accesses

SDRAM支持多bank间的乒乓操作,在当前bank输出尚未完成时,就可以向另一bank发送激活和读命令,两个bank的激活间隔需满足tRRD(RAS to RAS delay)。下图中的几个时序参数再讲一下:

tRCD:RAS to CAS delay,行选通周期,行激活后必须经过tRCD才能进行列选通。

CL:CAS latency,CAS潜伏期,列选通或读命令之后要经过CL数据才出现在IO上。

tRAS:ACTIVE to PRECHARGE command,在使能自动预充电的情况下,行激活后经过tRAS就会自动预充电。

tRP:预充电周期。

tRC:ACTIVE to ACTIVE/Auto Refresh command period,同一bank内不同行的激活的间隔。可以看到tRC= tRAS+ tRP。

tRRD:不同bank的行激活间隔,tRRD远小于tRC,所以不同bank间交错访问可以有效提升吞吐量。

READ Continuous Page Burst

连续页突发读,很好理解,可以突发完一整页,并且突发完一页后不会自己结束,可以用burst terminate命令结束突发。这里再解释一下CL和tAC的区别,CL是从CAS有效到数据IO有效,这其中包括列地址采样、解析、列选通MOS管打开,感测放大器放大并锁存,输出缓冲器输出等一系列过程;而tAC我理解纯粹指的是数据从输出缓冲器到IO的时间延迟,不包括控制逻辑的操作时间和感测放大的时间,从下图可以明显看到,它是从时钟上升沿开始计算的,输出缓冲器就是在时钟的控制下,将输出一拍拍打出。