蓝牙选型、蓝牙设计注意事项

【原创不易,请多鼓励】

上一篇文章,盘点了国产蓝牙芯片的现状,有些朋友后台留言推荐;

红海市场,最全国产蓝牙芯盘点

今天从芯片选型角度,介绍下如何选择合适的芯片;

全文干货,看完保准提出对芯片原厂的灵魂拷问,提前绕过许多不必要的坑。有帮助,请分享给你的朋友~

01

标准自问

产品总是会分层,买啥都会有中高低端;正式选芯片前,要先了解好,自己的应用需求是什么?功耗? 距离?SRRC/FCC认证?还是集成度?不同的应用需求,具体选型适合的标准线会不一样;别人无法使用的,也许我就能够使用;

02

芯片基础信息

创始人背景

靠谱的人做靠谱的事;船长以及核心骨干的出身,基本能定下基调;

芯片工艺

一般来说,芯片的工艺反应了芯片基础水平及价格水平;当前无线SOC产品及MCU产品的主流工艺还是55nm;以泰凌微举例,其上一代芯片基本是110nm工艺,功耗级别基本在; 新一代产品基于55nm工艺,功耗级别在;

另一方面,更高的工艺,芯片的整体面积会更小,芯片成本也会更有优势;

芯片可用GPIO

一定要提前算好;不同芯片设计时候需要外封的电源口,晶振口,其他固有功能IO情况都不同,QFN32封装的,多的GPIO可能到22,少的可能也只有18,因此前期要沟通好,计算清楚;

芯片内部Flash类型

目前的无线芯片,Flash一般都是SiP Flash的Die,这里需要确认SiP的Flash是否成熟,SiP的Flash接口类型,Flash支持的速率;如果是非SiP的Flash,最好了解下Flash是哪家的IP,哪些芯片已经成熟应用;别发生程序跑着跑着Flash内容改变或者Flash无法稳定运行的无奈情况;

03

睡眠相关

睡不仅仅是人的主题,也是低功耗芯片的永恒主题。针对BLE,需要了解和睡相关的特性,如下:

1. BLE协议栈唤醒可工作的睡眠状态下,需要多少RAM Retention,睡眠电流是多少;尤其针对睡眠模式RAM大小可配置的芯片,这个对于睡眠功耗影响较大;

2. 是否支持RTC唤醒;一般情况下,睡眠状态都是需要内部定时器唤醒,如果芯片睡眠状态只支持外部GPIO中断唤醒,需要确认是否满足要求;

3. 唤醒时间:芯片唤醒时间多长(包括协议栈正常工作),对功耗也有影响,尤其是频繁唤醒的应用;一般而言,芯片唤醒时间在us级别;

4. 管脚状态是否保留:很多时候,调试时候才发现,GPIO在睡眠状态下的状态不保留;因此,对GPIO掉电有要求的应用,一定要确认GPIO在睡眠情况下的状态;

5. 看门狗是否能够工作:目前睡眠状态下,基本都不支持看门狗工作;这就需要设计好幻想逻辑;很多应用可能都发生过睡眠状态无法唤醒的问题;针对稳定性要求极高的应用,建议外部加看门狗(定时器)芯片;

04

射频相关

射频,是BLE最重要的一个指标,这里需要特别注意的有以下几点:

射频匹配电路

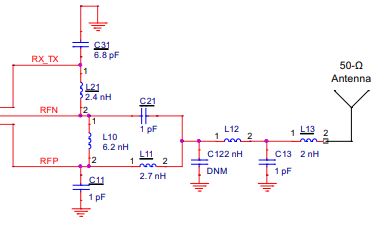

有些芯片的射频匹配电路非常复杂,如下图是TI的CC2640R2F,射频匹配电路元器件过多带来的不仅仅是射频性能问题,还是额外的成本及更高的失效风险;(图中是差分,单端会简单点)

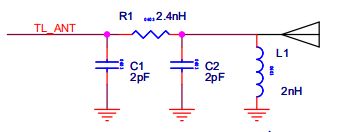

而目前很多国产蓝牙芯片,都内置了匹配,通过简单的PI电路即可以连到倒F天线,好用又省钱,如下图;

射频性能

BLE芯片一共40个信道;不同信道的灵敏度都不一样,如果说某些关键信道,如广播信道,灵敏度特别差,那么对于整体的性能影响会很大;同时,有射频认证需求的,如FCC/SRRC,最好提前确认芯片是否有通过过相关认证,拿到认真测试的结果,避免到了最后认证阶段出现问题;

射频的一致性

射频在不同温湿度,不同供电电压下的影响;比如电池供电设备,在降低到2.4V情况下,射频性能是否能够满足要求;这个一般专业的芯片公司,都必须提供低/中/高三个不同温度下的,全频段的RF指标;

05

协议栈相关

协议栈哪里的

买的成熟的协议栈?还是自己做的?还是基于开源的协议栈优化的?协议栈所做的功能性测试、稳定性测试及兼容性测试情况;如果芯片公司针对自己的协议栈测试清单都说不清楚...

协议栈认证

协议栈有没有拿到BQB认证;可以在SIG的LaunchStudio里面查询到;

协议栈的开销

基本现在都是BLE SOC,应用代码与蓝牙协议栈共存;这里需要了解协议栈实现的footprint,消耗了多少Flash/RAM,MIPS及Timer资源;这样可以评估剩余资源是否足够我们做应用的开发;

协议栈架构

协议栈架构如何,基于RTOS还是基于自己的任务管理系统;协议栈是如何实现功耗管理的;协议栈能够支持哪些低功耗状态;进入低功耗及唤醒后的流程如何?这个必须原厂做好,否则应用开发很难进行;

协议栈配套例程

一般而言,协议栈配套都会提供Central/Peripherial/Scanner/OTA例程;丰富的例程,将使你的开发速度更快;

06

硬件设计

关键元器件选型

一般而言,比较大的几个元器件有DC-DC电感,滤波电容,16M/24M晶振,32.768K晶振,这里需要了解清楚针对这些元器件选型的要求,拿到推荐的BOM清单;

针对晶振,需要了解是否需要外部匹配电容,如果不需要,内部匹配电容的大小选择范围多少?基于内部的匹配电容,能够达到的精度是多少,能不能满足蓝牙500ppm的要求?

最小系统Layout指南

最小系统,尤其DC-DC供电及RF走线的要求,包括线粗,走线等,这对RF性能有很大的影响;

其他注意事项

芯片设计中其他注意事项,比如某些IO口是否必须上下拉等;不然系统可能无法正常工作;

07

生产支持

产品最终离不开批量;不批量的产品都在耍流氓;生产过程一般还是需要进行测试验证。

1. 芯片是否支持PTM模式?是如何支持PTM的, 是固化在ROM里面还是可以提供PTM的源代码,或者库;

2. 芯片的产线烧录方案是什么? 烧录时间和效率是多少? 这个直接影响生产便利性和成本;

3. 如何进行频偏的校准;工具是否直接支持;校准后的频偏范围是多少;

4. 芯片的功耗数据,RF性能的最大偏差是多少,方便产线进行挑选? 一般芯片公司在芯片测试阶段应该有这方面的数据积累;比如说睡眠电流一般是2uA,那么最恶劣的情况会是6uA还是4uA以内? 同理RF性能也是;

08

结语

做产品不容易,硬件产品设计,芯片的选型更至关重要;不要因为前期功课的不足,导致人财两空;

我们不介意做第一个吃螃蟹的人,但是,拒绝当小白鼠;同意请分享 :-)

加微信好友

“一个专注在无线物联网的产品”

![]()

往期精彩文章

蓝牙AoA定位技术

蓝牙Mesh, ZIGBEE, THREAD网络性能对比?