PLL与DLL的区别

DLL即Delay Lock Loop, 主要是用于产生一个精准的时间延迟, 且这个delay不随外界条件如温度,电压的变化而改变.这个delay是对输入信号的周期做精确的等分出来的, 比如一个输入信号周期为20ns, 可以设计出等分10份的delay, 即最小2ns的delay. 这在高速界面做clock recovery and data recovery上很有用处。 由于普通的delay cell在不同的corner其delay会发生很大的变化(FF与SS相差几乎3倍), 有时候会被迫采用DLL来产生一个精准的delay而不是用普通的delay cell.

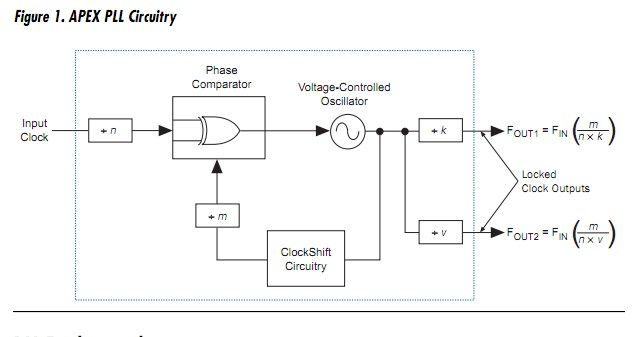

而PLL即Phase lock loop, 主要是根据一个输入时钟产生出一个与输入时钟信号in phase的倍/除频时钟, 其中倍频时钟和输入、输出时钟in phase是最主要的应用。

从内部结构上来看

DLL只有一个大的反馈环来调节最后1T后的信号与输入信号in phase来保证delay 出来的结果是对输入信号周期的均分,如示意图DLL.jpg; 输出信号只是对输入信号的一个delay, 即为同频且有一个固定的phase差,同时由于输出信号与输入直接关联,输入信号的jitter,frequency 漂移会直接反映在输出信号上。在实现上,可以是模拟电路也可以是数字电路实现,但绝大多数应该是模拟电路实现比较好,因为需要调节电压来补偿环境变化带来的delay 变化。

PLL除了有一个大的反馈环来让PLL振出的clock与reference clock in phase,内部还有一个小的ring oscillatorl来振出想要的clock,如示意图PLL.jpg。由于输出clock是由一个单独的ring oscillator振出来的,所以与reference clock的jitter,frequency漂移几乎完全无关。但由于是内部自己起振,所以比DLL要复杂。这个以前也有提过数字PLL, 但做出来的数字PLL振出来的clock很差,就几乎没有提数字PLL, 而是采用模拟电路来做。 好像xilinx用dll,altera用pll

dll是延时锁相环 delay locked loop,pll是锁相环 phase lock loop

dll 一般由数字电路实现的 , pll一般由模拟电路实现的

顺便说一句,pll下还分为增强型锁相环和快速型锁相环 (epll 和 fpll)

总结一下

(1) DLL 优势在于可以做到很高精度,可以排除温度、电压变化带来的影响,使得skew 可以作得很小,而且可以调整时钟占空比。

(2) PLL 优势在于抑制clock jitter 以及输入时钟的frequency漂移。

补充一点:DLL中由于Delay的时间范围有限,所以不大适用于低频信号

在用过ALTERA和XILINX的FPGA之后,

没有觉得PLL与DLL的区别能表现到做的项目上。

我想是不是对于大多数FPGA设计来说,还不用考虑这两者的区别

PLL,把相位差变成压差,然后控制VCO,调整输出时钟; DLL,把相位差变成延迟信号,然后通过延迟线调整输出时钟。 PLL是模拟电路的,DLL是数字电路的。

一般在altera公司的产品上出现PLL的多,而xilinux公司的产品则更多的是DLL,开始本人也以为是两个公司的不同说法而已,后来在论坛上见到有人在问两者的不同,细看下,原来真是两个不一样的家伙。DLL是基于数字抽样方式,在输入时钟和反馈时钟之间插入延迟,使输入时钟和反馈时钟的上升沿一致来实现的。又称数字锁相环。

PLL使用了电压控制延迟,用VCO来实现和DLL中类试的延迟功能。又称模拟锁相环。功能上都可以实现倍频、分频、占空比调整,但是PLL调节范围更大,比如说:XILINX使用DLL,只能够2、4倍频;ALTERA的PLL可以实现的倍频范围就更大毕竟一个是模拟的、一个是数字的。两者之间的对比:对于PLL,用的晶振存在不稳定性,而且会累加相位错误,而DLL在这点上做的好一些,抗噪声的能力强些;但PLL在时钟的综合方面做得更好些。总的来说PLL的应用多,DLL则在jitter power precision等方面优于PLL。

目前大多数FPGA厂商都在FPGA内部集成了硬的DLL(Delay-Locked Loop)或者PLL(Phase-Locked Loop),用以完成时钟的高精度、低抖动的倍频、分频、占空比调整移相等。目前高端FPGA产品集成的DLL和PLL资源越来越丰富,功能越来越复杂,精度越来越高(一般在ps的数量级)。Xilinx芯片主要集成的是DLL,而Altera芯片集成的是PLL。Xilinx芯片DLL的模块名称为CLKDLL,在高端FPGA中,CLKDLL的增强型模块为DCM(Digital Clock Manager)。

Altera芯片的PLL模块也分为增强型PLL(Enhanced PLL)和高速(Fast PLL)等。这些时钟模块的生成和配置方法一般分为两种,一种是在HDL代码和原理图中直接实例化,另一种方法是在IP核生成器中配置相关参数,自动生成IP。Xilinx的IP核生成器叫Core Generator,另外在Xilinx ISE 5.x版本中通过Archetecture Wizard生成DCM模块。Altera的IP核生成器叫做MegaWizard。另外可以通过在综合、实现步骤的约束文件中编写约束属性完成时钟模块的约束。