vitis报错:platform out-of-date,编译时makefile error;修改后application编译报undefined reference

参考资料:

https://forums.xilinx.com/t5/Embedded-Development-Tools/Drivers-and-Makefiles-problems-in-Vitis-2020-2/td-p/1188742

https://forums.xilinx.com/t5/Embedded-Development-Tools/Vitis-2019-2-LWIP-Echo-Server-Template-Build-Error/td-p/1124509

工作环境:

2020.2vitis

主要内容:

1、platform出现out-of-date问题

2、platform中加入了自定义的ip核,出现makefile error的问题,使用版本一makefile解决问题

3、用版本一的makefile解决platform编译问题后,出现application中undefined reference错误,使用版本二的makefile

(因此若需要改makefile,请根据不同vitis版本进行修改,我的为vitis2020.2使用版本二)

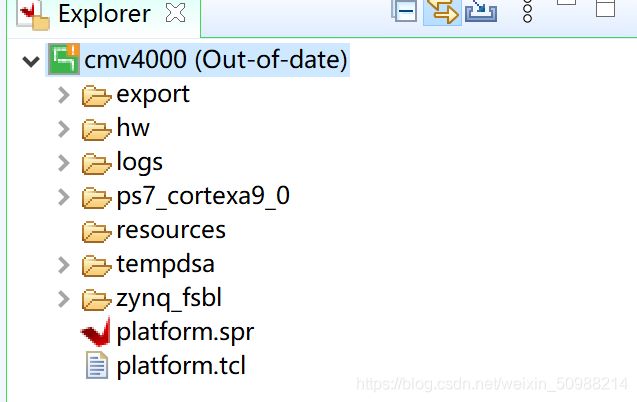

问题1、platform出现out-of-date问题

在我们VIVADO导出硬件平台XSA之后,我们将其添加入vitis的platform project中,这事我们需要查看platform的版本是否out-of-date,若过期则需要进行更新。

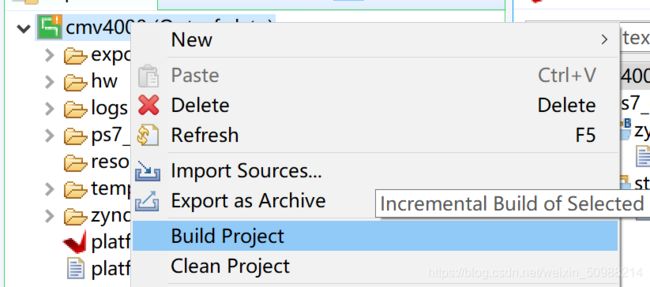

若出现out-of-date,直接的办法就是对platform,进行clean project和进行编译build project。一般来说只要编译通过,out-of-data标志就会消失,就可以添加如application project进行编写。

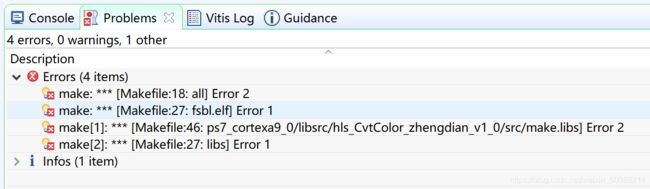

问题2、platform编译不通过,出现makefile error问题

对platform工程进行了多次的clean和build的操作,均提示以下问题:makefile error。一切的问题都指向了Makefile文件。

(下面部分为我自己的解决的艰辛历程,失败告终。最终的解决方案在最后,请自行拖到最后查看)

网上查阅的可能的解决方案:

1、如赛灵思论坛上说,修改make文件

2、可能是系统的原因,win10会报错。因此在linux上用vitis实现

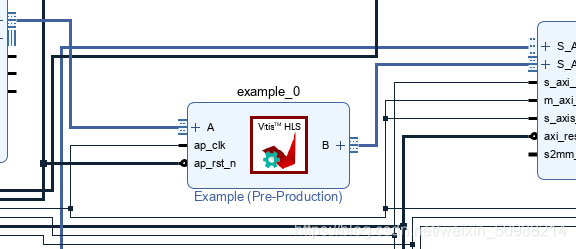

3、版本不匹配vivado hls2018应更为vitis hls 2020

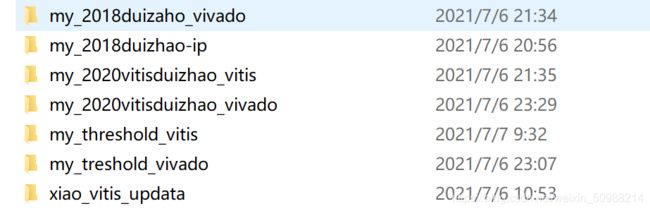

尝试(打算采用对照法找出问题):

1、师兄提供的vivado直接导出硬件,driver内有对应驱动(见桌面,fuxian),成功!!!!

2、使用最简单的2018生成的hls_color ip,导出硬件。driver内有对应驱动,(桌面,my)报错

3、(my_treshold_vivado文件夹)使用2018生成的hls_color,hls_threshold,导出硬件,driver内有对应驱动(桌面,my)报错。因此不是ip核编写难度问题。

4、使用自己写的重心法ip核,在vivado部分就报黑盒子,报错。

还在排查相关原因。

5、updata文件夹:updata尝试下,使用师兄的vitis工程中,直接更新xsa文件会产生的效果。失败。

更新方法网址:

https://forums.xilinx.com/t5/Design-and-Debug-Techniques-Blog/Step-By-Step-Guide-To-Xilinx-SDK-Project-Migration-To-Vitis/ba-p/1050061

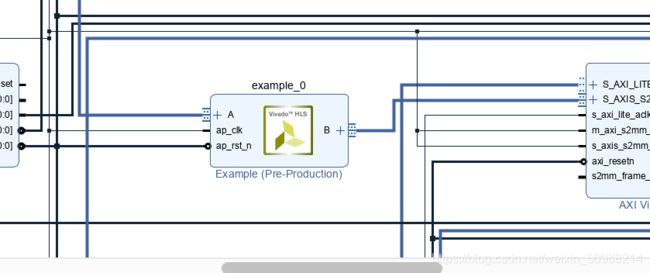

6、找了一个简单的vitis工程,接口两个Stream,中间简单的加减赋值。分别用2020.2vitis hls和2018.3vivado hls导出ip核(my_2018duizaho_vivado:装了2018vivado example核的vivado工程;my_2020vitis_vivado:2020vitis核的vivado工程,里面有+cvt核的xsa vitis_example核的xsa)将这两个工程的hardware platform导出到vitis中,全部通过。。

该部分为了探究使用不同版本的hls实现,是否是产生问题的原因。

(目前使用对照vivado工程进行验证,第一次采用的程序太简单,没能在vitis内产生driver,两者都通过)

设置的对照组图片

对照实验的结果与总结:

最后以失败告终,主要还是建议vitis hls在装完了vision库之后,调用里面的函数产生driver进行对照能看出效果,由于时间原因,关于vitis hls vision之后在进行尝试。

最终的解决办法:

特别感谢本贴作者,将详细内容均展示出来,感谢!!!

参考文献:https://forums.xilinx.com/t5/Embedded-Development-Tools/Drivers-and-Makefiles-problems-in-Vitis-2020-2/td-p/1188742

原因:

在VIVADO 2020.2中放入了2018.3vivado hls的自定义ip核。在2020中,makefile的内容出现了变化,导致这个ip的Makefile文件在编译时,出现了报错。需要对IP的文件中的Makefile文件进行手动的修改。

解决方法:

赛灵思论坛上varas的方法解决了这个问题,大力感谢。

要确保在平台的三个目录中替换更正的 makefile:

- Platform/hw/drivers/

/src/Makefile - Platform/ps7_cortex_a9_0/standalone_domain/bsp/ps7_cortex_a9_0/libsrc/

/src/Makefile -

Platform/zynq_fsbl/zynq_fsbl_bsp/ps7_cortex_a9_0/libsrc/

/src/Makefile

另外,根据不同的vitis版本,有两种不同的makefile文件。

版本一:

我只更改了其中的两行:.o的内容出现更改变为下面两行。其他位置如clean部分没有进行改动。

OBJECTS = $(addsuffix .o, $(basename $(wildcard *.c)))

ASSEMBLY_OBJECTS = $(addsuffix .o, $(basename $(wildcard *.S)))

在这三个主要更改之后,您的项目将正确构建并且您的自定义 IP 将正常工作!

下面是所需要的Makefile文件,大家可以对照着原代码进行修改。

COMPILER=

ARCHIVER=

CP=cp

COMPILER_FLAGS=

EXTRA_COMPILER_FLAGS=

LIB=libxil.a

RELEASEDIR=../../../lib

INCLUDEDIR=../../../include

INCLUDES=-I./. -I${INCLUDEDIR}

INCLUDEFILES=*.h

LIBSOURCES=*.c

OBJECTS = $(addsuffix .o, $(basename $(wildcard *.c)))

ASSEMBLY_OBJECTS = $(addsuffix .o, $(basename $(wildcard *.S)))

libs:

echo "..."

$(COMPILER) $(COMPILER_FLAGS) $(EXTRA_COMPILER_FLAGS) $(INCLUDES) $(LIBSOURCES)

$(ARCHIVER) -r ${RELEASEDIR}/${LIB} ${OBJECTS} ${ASSEMBLY_OBJECTS}

make clean

include:

${CP} $(INCLUDEFILES) $(INCLUDEDIR)

clean:

rm -rf ${OBJECTS} ${ASSEMBLY_OBJECTS} 这个版本的问题:

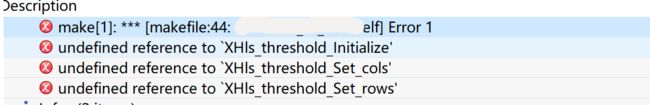

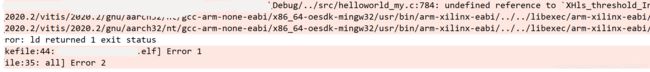

在后面的application编译时,若不使用新ip核的函数不会出现问题。但是一旦使用新的ip核函数,会报错:

编译小的,报错信息为下面的图1,2

编译大的,报错为:

![]()

报错原因如下:

https://forums.xilinx.com/t5/Embedded-Development-Tools/Vitis-2019-2-LWIP-Echo-Server-Template-Build-Error/td-p/1124509

原因大意是:

如果提示缺少的函数已在 BSP 文件中编译,就可以在 .o 文件中看到它们。如果已经正确编译是这样,那么链接器中出现缺失函数错误的唯一原因是:没有链接正确的 libxil.a 文件。

最核心的问题就是makefile文件编写不正确。

因此我的2020.2vitis得使用版本二的makefile(从别的函数的makefile复制而来)还是更改上面提到的三个部分

DRIVER_LIB_VERSION = 1.0

COMPILER=

ARCHIVER=

CP=cp

COMPILER_FLAGS=

EXTRA_COMPILER_FLAGS=

LIB=libxil.a

CC_FLAGS = $(COMPILER_FLAGS)

ECC_FLAGS = $(EXTRA_COMPILER_FLAGS)

RELEASEDIR=../../../lib/

INCLUDEDIR=../../../include/

INCLUDES=-I./. -I$(INCLUDEDIR)

SRCFILES:=$(wildcard *.c)

OBJECTS = $(addprefix $(RELEASEDIR), $(addsuffix .o, $(basename $(wildcard *.c))))

libs: $(OBJECTS)

DEPFILES := $(SRCFILES:%.c=$(RELEASEDIR)%.d)

include $(wildcard $(DEPFILES))

include $(wildcard ../../../../dep.mk)

$(RELEASEDIR)%.o: %.c

${COMPILER} $(CC_FLAGS) $(ECC_FLAGS) $(INCLUDES) $(DEPENDENCY_FLAGS) $< -o $@

.PHONY: include

include: $(addprefix $(INCLUDEDIR),$(wildcard *.h))

$(INCLUDEDIR)%.h: %.h

$(CP) $< $@

clean:

rm -rf ${OBJECTS}

rm -rf $(DEPFILES)

使用该版本进行编译,platform和application都不报错

no such file

另外若出现更改platform后,重新编译application project发现找不到部分头文件。是因为project链接着原来的platform,需要删除project,新建后,将src复制入。就可以解决。