A 0.18um CMOS SOC for a 100-m-Range 10-Frame/s 200x96 pixel time-of-flight Depth Sensor翻译

摘要

随着高级辅助驾驶(ADAS)对高分辨率光探测和测距(LIDAR)技术的需求,我们介绍了一种用于飞行时间(TOF)传感器进行时间相关单光子计数和完整数字信号处理的片上系统(SoC)。在0.18-mcmos片上系统的核心部分,我们采用了基于单光子雪崩二极管的16 TOF和32仅限强度宏像素的线性阵列,从而同时获得有源TOF和无源强度图像。SoC还包括能够在时空相关事件上产生精确触发的电路阵列、64个12-b时间数字转换器阵列和768kb SRAM存储器。SoC提供系统级串行低比特率数字接口做以下功能:1)多回波距离;2)距离可靠性;3)强度;4)被动强度;从而减轻系统级强度和开销。已经实现了一个概念验证原型,该原型能够以10帧/秒的速度实现高达100米的深度成像,分辨率为202x96像素。对TOF传感器在强太阳背景照度(即70klux)下的定量评估表明,在100 m的距离范围内,重复性误差为14.2cm,因此相对精度为0.14%。在相同条件下,相对非线性误差为0.11%。为了证明我们的方法对ADAS相关应用的适用性,我们还报告了深度传感器在典型交通状况下的实验结果。

介绍

主动安全系统在全世界汽车制造商中越来越受到关注,因为一些新的汽车评估计划(NCAP)鼓励汽车制造商大大超过当地法规中的最低安全要求,并将其评级标准扩展到包括这些系统[1]。事实上,例如,欧洲NCAP一直在修订其评级标准,将重点放在包括行人安全在内的整体车辆安全上,而不是只考虑成年乘客的安全。在这种情况下,一类特殊的安全系统是所谓的高级驾驶员辅助系统(ADASs)。前面的碰撞警告(FCW)、自动紧急制动(AEB)、自适应巡航控制(ACC)和行人检测系统都依赖于各种传感技术。在这些传感器中,毫米波雷达仍然是首选的传感器,在某些ADAS设计中,雷达已经与单目或立体视觉相机之类的无源光学传感器相结合以实现所需的功能。最近,基于飞行时间(TOF)原理的主动光学传感器已经成为具有竞争力的替代传感器或ADAS应用的辅助传感器。

具有成像能力的光探测和测距(LIDAR)传感器的一个快速发展类别是所谓的TOF三维(3-D)相机[2]–[20]在这些系统中,使用发光二极管(led)或激光二极管(LDs)阵列来漫射照亮场景中的目标。由于其简单的电光结构以及低成本和紧凑的实现潜力,这些传感器似乎已经引起了人们的极大兴趣。然而,在这些传感器中,由于扩散光方法中发生的强烈信号衰减,像素需要应对极低的光信号强度。虽然它们在受控环境(如室内)的数米范围内运行良好,但在更恶劣的环境光照条件下,它们的性能往往会迅速恶化。在[2]-[20]中描述的传感器,尤其是基于相位测量和/或间接TOF原理的传感器,另一个常见且显著重要的局限性是无法处理多回波距离评估。在大多数实际交通场景中,多回波是普遍存在的。当一个特定的像素将来自两个或多个不同距离的目标的后向反射信号进行积分时,或者当光信号通过半透明介质传输时,就会出现这种情况。虽然后一个问题在传感器通过玻璃物体成像时很明显,但它也可能源于非理想的天气条件,如雨和雾。然而,更重要的是,多回波通常与前景目标物体的边缘相关联,而前景目标物体是通过传感器的有限角度(像素)分辨率采样的。在基于锁定[2]或间接TOF原理(例如[7])的像素中,多个回波信号被卷积成单个且通常是错误的距离输出。

在我们的实验室中,我们一直在研究扩散光传感器的优越替代品,以便使成像光检测和测距(LIDAR)能够在完全不受控制的环境中可靠地工作,并受到成本效益的限制。在文献[21]中,介绍了一种激光扫描CMOS TOF深度传感器。该传感器实现了基于单个LD的实时和远程深度成像,并实现了与使用64个离散LD阵列的高端成像LIDAR系统相当的测距性能[22]。利用微机电系统(MEMS)扫描仪方法的成像TOF传感器也获得了相对于扩散光TOF 3-D相机的优异性能[23],[24]。尽管激光扫描传感器有其优点,但也有其自身的局限性。在这些方法中,小型化、高帧速率和机械鲁棒性更具挑战性。雪崩光电二极管偏压高于其特征击穿电压,因此操作在称为Geiger mode,一直是CMOS传感器的核心。这些器件通常被称为单光子雪崩二极管(spad),其一个关键特性是能够检测低功率光信号,其时间分辨率为100ps[25]。通过触发基于光子时空相关性的TOF评估,以及先进的时间相关单光子计数(TCSPC)处理,实现了对室外环境光产生的不相关光子的电路级抑制。然而,到目前为止,基于TCSPC的实时数字信号处理(DSP)算法(涉及内存密集型直方图处理)只在外场可编程门阵列(FPGA)器件上实现。基于SPAD的前端和DSP后端集成电路(前者通常包括一系列高通量时间数字转换器(tdc))之间的分离对系统架构和相关成本具有重要影响。实际上,除了在系统中需要一个配套的FPGA之外,前端和后端集成电路之间的读出接口的特点是数据速率为几千兆/秒[10]、[21]、[23]、[24],从而进一步增加了系统的复杂性和成本。

在这篇论文中,我们报告了一个CMOS片上系统(SoC)的设计和特性,该SoC执行了100米范围TOF传感器的完整TCSPC传感和DSP处理[26]。每像素可分解多个目标,因此可大大扩展ADAS特定计算机视觉算法的三维点云数据,同时抑制通常发生在锁定和间接TOF像素中的相关错误距离估计。片上DSP还确定每个多回波距离评估的完整性级别,同时将可靠性信息输出到系统级电子设备。通过获取主动(信号和环境光)以及被动(仅环境光)强度图像,在芯片上实现对传感数据的进一步增强。因此,CMOS芯片为系统级电子设备提供串行和低比特率数字接口:1)多回波距离;2)多回波距离可靠性;3)主动强度;4)被动强度,从而降低系统级复杂性和成本。一个以10转/秒的速度旋转的六面多面体反射镜与单个LD结合,以55度的水平视场(FOV)进行激光扫描,同时达到9度的垂直视野。在室外日光下获得实时、精确的距离图像,分辨率为202x96像素,10帧/秒,100米范围内,最差精度是在非合作目标显示只有可控反射9%上获得,它被利用模拟通用物体最低反射率,是0.14%,整个测量范围。

本文组织如下:在第二节,我们描述了我们的激光雷达系统设计,并介绍了新的前瞻性被动成像概念。在第三节,在片上实现的原始DSP算法。在第四节,我们详细介绍了传感器芯片的设计。第五节报告并讨论了实验结果。论文在第六节结束。

II 成像激光雷达系统

成像激光雷达系统基于激光扫描方法在[21]中介绍。它还是被重新设计来实现更多的功能和实现更好的性能,但是它的体积要小得多。电光系统的示意图如图1所示。单个LD同轴对准六面多面体反射镜,以半峰全宽(FWHM)发射4ns全宽脉冲,重复率为133k脉冲/秒。LD中心波长为870nm,而其线宽约为4nm半峰全宽。它的光束在垂直和水平方向上的发散角分别为1.5和0.05度,类似于[21],多边形反射镜的每个面都有稍微不同的倾斜角度。结果,在每一次100毫秒的旋转中,多边形反射镜在六个垂直方向反射激光束,从而覆盖,与激光垂直发散一起,9度连续的垂直视野。在55度水平扫描过程中,在每个平面上,场景中目标的后向反射光子由同一平面采集,并在凹面镜焦平面处的CMOS传感器芯片上成像。光学近红外干涉滤波,为清楚起见,没有在Fig.1中显示,也被放置在传感器前面,以增强背景光抑制。该滤波器的通带透射率为80%带宽为10nm半峰全宽,然而阻带透过率为1%。不像[21],soc包括两个相邻的像素垂直线性阵列。图2描绘了激光雷达系统及其视场图。一个16像素的阵列用于测量主动激光束的TOF,而32个像素的第二个阵列用于执行被动成像。这些阵列的像素在不同的平面时间解析场景的不同垂直部分,从而为主动图像和被动图像生成96和192像素的实际垂直分辨率。在完全旋转结束时,同时获取202x96像素的主动图像和202x192像素的被动图像。如Fig.2所示,被动成像是由一个原始的前瞻性概念实现的,被动像素暴露于场景中尚未被激光束照亮的部分的光子。因此,相对于TOF像素,被动像素以稍微提前的时间对环境光照明场景进行成像。在我们的概念中,TOF和被动图像之间的像素到像素的对应是通过设计实现的,因此无需计算昂贵的处理来实现这一功能。此外,由于场景任何部分的被动和主动成像之间的延迟非常短,只有88us,在本研究中,典型的交通场景中的运动物体不会导致这些图像之间的场景不匹配。因此,可以利用被动图像精确地预测要在TOF图像上任何像素背景光的量。被动图像也为高层次的计算机视觉算法提供了有价值的信息。

系统电子设备包括几个印刷电路板,以容纳不同的子系统,如SoC本身、激光驱动电路、接口电子设备、电源和通用串行总线(USB)收发器。该系统需要一根USB数据传输电缆和一个外部交流适配器才能工作。

III时空相关数字信号处理

如第二节描述,我们的传感器通过光学近红外干涉滤波实现了对杂散光的第一级抑制。然而,由于太阳环境光和单个LD之间的功率悬殊,即使在中等日光条件下,光学水平的背景光(BG)抑制也不充分。为了应对强环境光照条件,传感器必须在电路和DSP级执行额外的BG抑制。在这项工作中,BG光子的抑制是通过一个原始原理实现的,即信号光子的TOF是根据两个或更多个光子的时空相关性来测量的[21]。基本原理如图3所示。在该图中,给定像素内的入射光波形被描绘为一系列光子事件,反过来,用波形数据包形状符号描述。黑色(虚线)符号表示来自不相关环境光的像素内检测到的光子,而红色(实心)符号表示来自LD的信号光子。此外,每个波形的开始与激光脉冲的发射时间一致。由于激光脉冲持续时间为4ns,因此像素电路可以故意忽略(在时间上至少分散4ns的)单个光子事件。这些孤立的光子事件更有可能来自不相关的背景光,其显示出不同的到达时间。信号光子在时间上受限于激光脉冲的持续时间,因此,表现出相当高的关联概率。因此,像素电路生成TOF评估检测时间相关光子触发信号,在4ns内同时检测到两个或多个光子的事件。如将在第四节中描述的,时空相关事件的检测是通过包括几个空间受限spad的宏像素来实现的。

在强环境光下,涉及到两个或多个不相关光子错误相关事件仍可能以不可忽略率发生。然而,这些错误相关事件也与激光信号时间无关。作为结果,为了进一步提高对这些有害要的事件的抑制,在像素级执行一个时间相关DSP。如图3所示,通过添加相关光子数量到一个直方图容器,每个相关事件被保存在一个时间直方图中,和测量时间延时、激光脉冲发射方面成比例。时间延时由像素级TDCs估计,在章节IV中描述。这个处理会重复几个激光脉冲。在图3中,与激光信号相关的事件往往以相同的延迟发生,从而在与期望TOF周围附近的bins中的直方图中形成一个峰值。由于错相关事件呈现随机触发时间,它们往往在直方图中均匀分布。此外,直方图统计的平均值 和错相关事件在总比例中的成比例减少。

从直方图数据中提取单个回波返回的TOF的典型有效算法包括确定所有直方图单元中具有最大值的bin的位置[21]。一旦获得直方图,并且忽略二阶效应,如激光散斑和大气湍流,直方图的每个bin值可以精确地建模为泊松变量。在极低的信号背景光比(SBR)条件下,直方图库的随机性对直接确定与单个或多个回波信号返回相关的每个TOF峰值提出了挑战。因为具有期望值N的直方图bin中的相对波动相对于其均值减小,与N的平方根成比例,通过积累多次激光重复周期,提高了TOF的准确测定[5]。然而,在激光扫描方法中,除非牺牲图像分辨率,否则无法执行这种长时间平均处理[21]。另一种提高柱状图单元期望值的方法是减少柱状图单元的数量,从而减少它们的相对波动。实际上,通过减少bins的数量,平均来说,每个柱状图箱子捕获更多的事件,从而增加其预期值。该技术提高了从均匀分布组分中鉴别TOF峰的成功率,前提是柱状图的持续时间与激光脉冲的持续时间相当

超过此临界持续时间后,均匀分布的信号峰值振幅与平均值对比度降低。然而,直方图的个数与距离分辨率直接相关,从而限制了该方法的适用性。

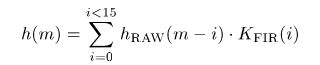

在这项工作中,为了减少散粒噪声引起的bin值波动,在确定TOF峰值位置之前,我们提出DSP算法用有限脉冲响应(FIR)滤波器对获得的直方图进行滤波。该技术在不影响距离分辨率的情况下,显著提高了确定实际飞行时间信号返回的成功率。考虑到光学规格和SoC设计的分析表明, 11-b字 2048 bins的柱状图代表了传感器性能和芯片尺寸之间的良好折衷 。FIR滤波器由一个低通滤波器组成,15个字的内核定义为

K FIR = {6,8,10,11,12,13,14,15,14,13,12,11,10,8,6}

K FIR的长度和值是通过我们传感器系统模型仿真得到的。过滤操作是通过将直方图与滤波器核卷积来执行的

h(m)是第m次滤波直方图bin,h raw表示未处理的bin值。下一个DSP操作包括确定直方图中对应于多个回波信号返回的信号峰值的TOF位置。这是通过使用图4中描述的算法来实现的。经过简单的初始化后,该算法对滤波后的直方图进行处理,并分别跟踪三个最高值的直方图的值和位置。然而为了防止这些最大值与单个TOF峰值相关,它们的位置必须用预定数量的bin隔开。我们假设FIR滤波器核的长度,即15,足以区分独立的TOF峰值。图4中的算法利用三个变量来存储三个多回波距离的TOF位置,命名为TOF(1),TOF(2),TOF(3),还有三个附加的来存储各自的振幅,RELY(1),RELY(2),RELY(3)。后一个变量也被用作可靠性的度量,在高级应用特定的信号处理中,可以从中确定信任水平。最后,DSP算法还确定了整体直方图的积分作为主动照明强度的度量。这些信息保存在一个名为INT的变量中,由一系列七个处理结果完成,通过DSP电路输出每个像素。未处理和过滤的直方图,以及DSP的理想结果,如图5所示。

IV 传感器芯片设计

A SOC结构

图6描绘了SoC架构的框图。芯片传感器包括两个像素线性阵列,用于执行被动强度成像和主动多回波TOF成像。被动和主动成像线性阵列的每个像素由几个空间受限的spad组成。这些像素被称为“宏像素”。当多个SPAD宏像素用于在主动像素中执行时空相关函数时,仅用于被动的宏像素也利用多个SPAD来增加其动态范围。TOF宏像素包括排列在6x4个元素的矩形阵列中的24个spad,而被动强度像素中的spad的数量减少到12个或6x2,为了使垂直分辨率加倍。16个TOF宏像素共享64个TDC的阵列以及32个2048x11b的SRAM块的阵列。后者在DSP电路中使用了768kb的片上存储器。整个SoC还包括基准锁相环(PLL)、偏置电路和片上联合测试自动化组(JTAG)控制器。芯片读出接口被高度简化,以减轻对系统级电子器件的限制。然而,出于测试目的,JTAG控制器允许对大多数片上寄存器(包括片上SRAM块)进行读写访问。

在系统级不需要实现JTAG接口的正常工作模式下,两个读出电路同时实现主动和被动像素的数字串行接口。被动成像接口输出544b的数据包,即对应于32个被动像素的17b强度信息的32个字。1216-b主动TOF数据包由3个11-b距离的字、3个10-b可靠性的字和每个像素的13-b信号强度组成16个像素,通过TOF串行接口从芯片上读出。每个图像帧读取这些数据包的重复次数对应每个多面镜采样的像素列的数量,202x6。作为结果,在10帧/秒下,片外数据率数量级大约为6.6和14.7Mb/s对应被动和主动TOF图像,相应的。这些数据速率比之前的工作[10]、[21]、[23]、[24]慢了大约三个数量级。

B TOF宏像素电路

图7所示为主动宏像素电路的示意图。单光子探测由24个spad阵列实现,这些spad分别连接到24个前端电路阵列上。每个前端电路在其相应的SPAD中检测到光子后,输出一列持续4ns的数字矩形脉冲。24个前端电路的输出被组合为并发检测(CD)电路的输入,而当两个或多个输入同时激活时,该电路输出断言。由于前端电路的输出对检测到的光子保持激活4ns,任何其他前端电路上随后检测到的光子将导致CD电路断言其输出,从而实现检测时空相关事件的期望功能。这种宏像素电路结构,包括CD电路的设计,是在[21]中针对12 SPAD TOF宏像素而提出的。在这里,我们使用相同的电路架构。然而,CD电路被重新设计来检测24个输入端之间的活动信号的并发性,而不是文献[21]中使用的12个输入端。

我们还修改了前端电路,以实现更短的死区时间,并添加了一个JTAG接口,以允许禁用单个spad用于测试目的。前端电路的示意图如图8所示。除JTAG接口外,被动quenching和主动recharge电路操作与[21]中使用的相同。尤其是D触发器FF1,它保持其相应SPAD的启用/禁用状态,由1.8伏电源供电。它的输出可以方便地用作厚氧化物(3.3v)晶体管M1的共栅偏置,与晶体管M2形成共栅电流源。这个源的电流值被设计成比所谓的SPAD锁存电流小得多,从而确保了适当的雪崩quenching[21]。偏置电压是在芯片上产生的,并在全局范围内分布到所有的spad。spad的设计,包括布局以及对共深n阱阴极(VAPD)的偏压分布,与文献[21]中的设计完全相同。当spad的室温击穿电压为22.3v时,VAPD为25.6v时,可获得3.3v以上的过量偏压。当SPAD中的光子被探测到时,雪崩电流流入M1和M2形成的共源共栅电流源。如图8所示,由于SPAD电流远大于此电流源的标称电流,阳极电压上升极为迅速,从而减小了SPAD对电流的偏压,并最终使其电流熄灭。一旦SPAD完全熄灭,它的结电容和节点上的寄生电容由同一电流源向地充电。如图8(b)所示,由逆变器将振幅约为的电压脉冲转换为矩形数字脉冲。这个脉冲的持续时间大致定义了SPAD死区时间,即SPAD无法检测到后续光子的时间,通过调整共源共源电流源的值,在本研究中将其从[21]中的40 ns设置为20 ns。在随后的反转之后,矩形脉冲被一个简单的单稳态电路缩短到4ns,如图8(a)所示。SPAD级JTAG接口由一个shadow D触发器FF2镜像FF1以及实现诸如捕获(CAPT)、更新(UPD)和移位寄存器(shift)等常用功能的附加逻辑组成。回到图7,宏像素的其余功能包括对每个相关事件中涉及的光子数进行采样的加法器电路、tdc和用于与下一级同步的FIFO存储器,即DSP电路。在图7中没有展示,在CD电路的输出端加入一个单稳态电路,以产生可管理的4ns触发脉冲,从而防止后续阶段的亚稳态误差。加法器的24个输入在CD触发事件时寄存,而其输出则将相关光子计数编码为5b字。在[21]中,每个TDC以及宏像素可以记录相关事件的最大转换速率被限制为12.5M采样/s。我们的光学模型的系统级仿真显示,先前的转换率,受到片外读出吞吐量的限制,在室外环境光的极端条件下是不够的。随着宏像素尺寸从[21]中的12spad增加到新像素中的24 spad,高转换率的要求也变得更高。在这项工作中,我们利用片上DSP实现的数据压缩,并将每个宏像素的最大事件率提高到100Msample/s,从而提高TOF像素对环境光的抗扰度。这是通过将相关事件分布到四个像素级的tdc来实现的。在[27]中引入并在[23]中扩展到64个TDC的实现的12-b TDC阵列需要100 MHzSoC时钟的四个周期来完成转换。通过在四个tdc之间顺序分布相关事件,宏像素的有效转换时间减少到10ns。 事件分布由由下降沿触发的2-b计数器驱动的基于AND的解码器执行,如图7的插图所示。如图中所示,从解码器的输入A到其任何输出的传播延迟完全匹配,以至于四个输出AND门彼此匹配。在SoC时钟频率下工作的像素级TDC读出电路用其对应的相关光子数读出有效的TDC结果,并将其编码成写入同步FIFO的16-b字。由于DSP直方图有2048个bin(见第三节),它不能容纳TDC的全部12-b分辨率。因此,通过范围选择信号RANGESEL丢弃最高或最低有效位,TDC分辨率被压缩一位。名义上,使用853.3ns[27]的TDC范围,从而将其最低有效位(LSB)分辨率提高到416.7ps。此设置对应于飞行时间128米范围内的6.25厘米分辨率。可选地,可以通过JTAG控制器设置RANGESEL,以在64m的范围内实现3.125cm的距离分辨率。

C 数字信号处理电路

第三节中提出的基于直方图的DSP算法,具有在TOF评估中从不相关噪声中获得几乎唯一的信号识别的优点。这种优势与电路面积和处理时间有关。后者是一个关键问题,因为与其他散粒噪声受限的光学检测系统一样,整体性能取决于传感器最大限度地暴露于光信号的能力。例如,暂停像素的光子信号采集以执行DSP和/或直方图重置,无疑会影响测距性能或图像分辨率。在我们的设计中,我们通过整合两个2048x11b每像素的存储块来防止信号采集的中断。这些块被全局地安排在两个内存bank中,每个内存库有16个块,即bank A和bank B。图9示出宏像素级DSP电路的框图。它独立实现两个基本功能:直方图采集和直方图DSP处理。缓存通过模式选择信号MSEL依次分配给直方图采集和DSP。在存储器组a中执行多边形刻面上给定像素列的直方图获取,DSP执行先前存储B获得的数据。一旦该列的像素获取时间过去,则交换存储库并重复该过程。因此,这种方法允许同时采集和处理飞行时间数据。如图9所示,宏像素的FIFO电路连接到直方图获取电路,建立一个直方图来自时空相关事件来源于FIFO。直方图DSP电路完成后,将多回波DSP结果以及直方图积分记录到输出寄存器中,随后在芯片外串行读出。

图10(a)表示TOF图像帧内的像素的坐标,以及细小组成202x16像素与多面镜形状的实际位置。图10(b)展示了TOF图像帧级到像素级一系列相关信号有关的波形。当传感器以10帧/秒的额定帧速率工作时,整个帧采集需要100毫秒。当传感器光圈挡板与镜面接合边缘对齐时,无法进行信号采集。因此,如图所示,每个面的有效曝光时间限制为(100ms/6=16.666ms=8.89ms+7.77ms)8.89ms。在平面之间7.77 ms的非活动时间内,大多数SoC功能(包括像素和DSP电路)保持非活动状态。因此,LD发射以每帧6次的8.89ms的脉冲频率工作。每个活动刻面时间被细分为202个时间间隔 ,在此期间并行获取和处理16 TOF像素的子列。这些间隔与像素获取时间相对应,精确地占用(8.89ms/202=44us)44 us。例如,facet#2获取TOF图像帧的像素PX{(x,y):0≤x≤201 ^ 16≤y≤31}的数据。在其活动时间窗口的开始PX{(0,y):16≤y≤31}由存储bank A获得。一旦像素采集时间过去,存储器组A切换到DSP模式,存储器组B开始采集PX{(1,y):16≤y≤31}.在DSP模式下,对存储库A中采集的16个直方图进行数字处理,以输出距离、可靠性和强度。PX{(1,y):16≤y≤31}获取事件结束时,存储库再次切换PX{(2,y):16≤y≤31}在bankA中执行。在此期间,串行读出电路输出PX{(0,y):16≤y≤31}的DSP寄存器结果。然后继续该过程,直到与每个面相关联的所有像素被完全获取、处理和读出。

假设在像素时间开始时直方图为空,直方图获取电路从FIFO读取16-b字数据,并根据MSEL利用11 LSB(即TDC输出)作为bank A或bank b存储器的地址信号。该地址的存储器内容在一个时钟周期内被读出。在接下来的周期中,存储器内容加上FIFO读出的高5位数据(msb),即光子计数,并且结果被重写到相同的存储器地址。对于像素获取时间内的所有相关事件,重复该过程。

利用图11所示的五级流水线电路来执行直方图DSP。图12示出了与流水线操作相关联的时序图。DSP的执行是由初始化操作(INIT)开始的,通过该操作可以擦除许多内部寄存器的内容。一个15字的寄存器HB(i),其中i {0,1,2……,14};3字寄存器TOF(n)和RELY(n),其中i {0,1,2},一个单字寄存器INT和一个内存地址寄存器ADDR。由于直方图内存是通过递增其地址顺序处理的,因此HB被用来保存直方图的15个尾随bin值。TOF(n)和relay(n)分别用于记录三个TOF回波的TOF位置和可靠性,INT作为寄存器来计算直方图的积分。如图12中的图所示,流水线执行从读取存储器操作(RM)开始。在这个循环中,直方图存储器在ADDR寄存器指向的地址读取,bin值(DIN)被写入的第一个元素HB。在同一循环中,HB的元素同时移位,即

HB(i) = HB(i - 1) i {1,2,3,4……14}

作为下一个像素获取的准备,必须顺序重置直方图内容。由于我们的片上SRAM块有一个单端口接口,复位操作需要在同一个内存地址上的另一个时钟周期。因此,在接下来的时钟周期中,在图中表示为写入存储器(WM),相同地址的存储器内容被擦除,ADDR递增。 在同一个循环中,执行两个并行计算。当HB(0)加到INT的现有值上时,HB按元素乘以第三节中定义的15个字的过滤器内核K FIR,结果存储在15个字的寄存器中HBK,

HBK(i) = hb(i) * kK FIR(i) i {0,1,2,3,……,14}

为了完成(2)中定义的卷积计算,下一个操作涉及对HBK的所有元素进行求和(SU)运算。结果保存到名为H

H=求和累加hbk(i) i=0,……15

在下一个循环中,执行几个比较(CP)操作。将的当前值H与RELY(n)进行比较,其中n {0,1,2},如图11所示,同时根据图4中列出的算法1考虑额外的细节。TOF(n)和relay(n)的新值最终在流水线的最后阶段被写回(WB)到这些寄存器中,这取决于上一个周期中执行的比较结果。然后,对所有柱状图存储单元继续执行流水,尽管由于单端口SRAM访问,延迟了两个周期而不是一个周期。这个特性是一种设计选择,而不是电路限制。由于直方图包含2048个单元,整个处理(包括将DSP结果保存到输出寄存器的最后一步(RG))需要4102个时钟周期。此外,DSP电路以与SoC主时钟相同的频率工作,即100mhz。结果,整个DSP处理耗时41us,可以在44 us的像素积分时间内有效地适应。一个双端口SRAM接口可以用来减少DSP时间,但是需要更大的电路面积。