AD9371 官方例程HDL详解之JESD204B TX侧时钟生成 (一)

AD9371 系列快速入口

AD9371+ZCU102 移植到 ZCU106 : AD9371 官方例程构建及单音信号收发

ad9371_tx_jesd -->util_ad9371_xcvr接口映射: AD9371 官方例程之 tx_jesd 与 xcvr接口映射

梳理 AD9371 时钟,理解采样率和各个时钟之间的关系 : AD9371 官方例程HDL详解之JESD204B TX侧时钟生成 (三)

参考资料:

UltraScale Architecture GTH Transceivers User Guide UG576

文章目录

- 前言

- 一、AD9528 与 MGTREFCLK

- 二、QPLL 和 CPLL 的 Reference Clock

- 三、通过QPLL 或 CPLL 得到 LineRate

前言

AD9371 官方例程HDL 中 TX 侧各个时钟的产生,与采样率之间的关系

后续见 AD9371 官方例程HDL详解之JESD204B TX侧时钟生成 (二)

一、AD9528 与 MGTREFCLK

ADRV9371-W/PCBZ上的 AD9528 OUT1(B20、21)、2(D04、05)、3(G36 、37)通过FMC 连接入FPGA中,OUT2后续未使用,OUT12、13提供给 AD9371 使用

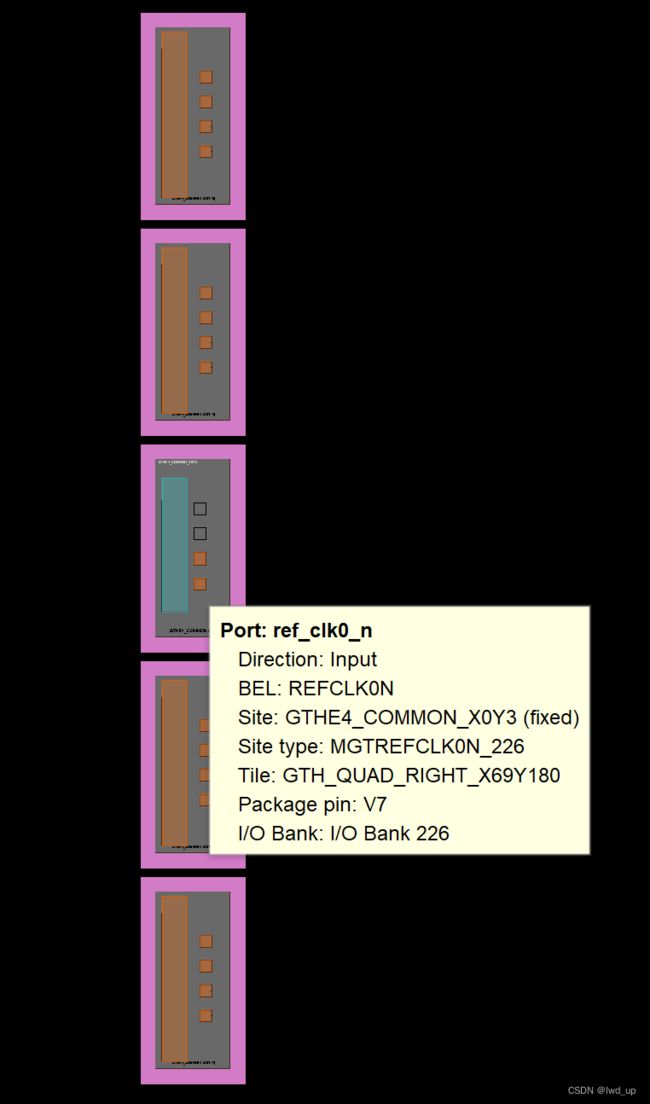

set_property -dict {PACKAGE_PIN V8 } [get_ports ref_clk0_p] ; ## D04 FMC_HPC0_GBTCLK0_M2C_C_P

set_property -dict {PACKAGE_PIN V7 } [get_ports ref_clk0_n] ; ## D05 FMC_HPC0_GBTCLK0_M2C_C_N

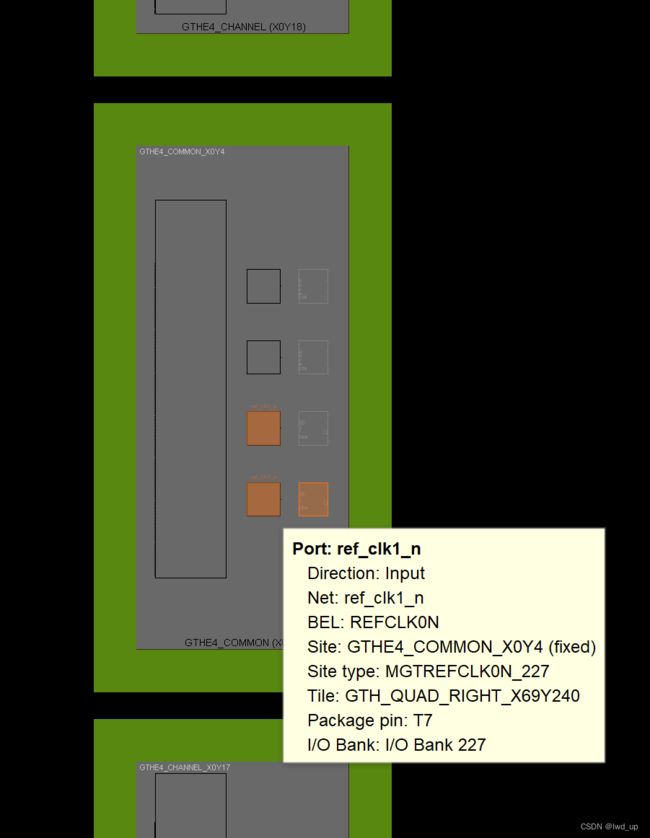

set_property -dict {PACKAGE_PIN T8 } [get_ports ref_clk1_p] ; ## B20 FMC_HPC0_GBTCLK1_M2C_C_P

set_property -dict {PACKAGE_PIN T7 } [get_ports ref_clk1_n] ; ## B21 FMC_HPC0_GBTCLK1_M2C_C_N

BANK 226和BANK 227各是一个Quad,ref_clk0 后续未使用,即后续FPGA中参考时钟使用的是BANK 227 的MGTREFCLK0。

IBUFDS_GTE4 i_ibufds_rx_ref_clk (

.CEB (1'd0),

.I (ref_clk0_p),

.IB (ref_clk0_n),

.O (ref_clk0),

.ODIV2 ());

IBUFDS_GTE4 i_ibufds_ref_clk1 (

.CEB (1'd0),

.I (ref_clk1_p),

.IB (ref_clk1_n),

.O (ref_clk1),

.ODIV2 ());

...

...

system_wrapper i_system_wrapper (

.rx_ref_clk_0 (ref_clk1),

.rx_ref_clk_2 (ref_clk1),

...

.tx_ref_clk_0 (ref_clk1),

ref_clk 先通过 IBUFDS_GTE4, 使用O输出提供给GTHE3/4_CHANNEL 和

GTHE3/4_COMMON

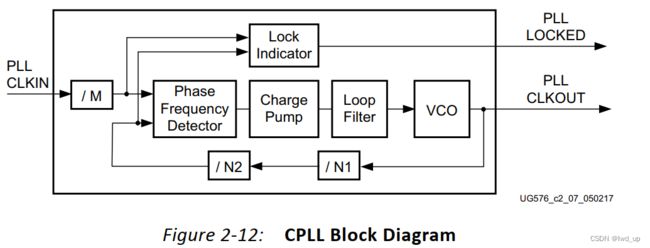

二、QPLL 和 CPLL 的 Reference Clock

对于BANK 226和BANK 227的MGTREFCLK0 和 MGTREFCLK1(两个BANK都未使用),QPLL0 的可选参考时钟源 GTREFCLK00 是MGTREFCLK0 通过 IBUFDS_GTE4 后提供的,GTREFCLK10 是MGTREFCLK1(不能使用) 通过 IBUFDS_GTE4 后提供的;

QPLL1 的可选参考时钟源 GTREFCLK01 是MGTREFCLK0 通过 IBUFDS_GTE4 后提供的,GTREFCLK11 是MGTREFCLK1(不能使用) 通过 IBUFDS_GTE4 后提供的

程序中 QPLL0 和 QPLL1 的 QPLL0REFCLKSEL 都选择了MGTREFCLK0 通过 IBUFDS_GTE4 后提供的参考时钟

.QPLL0REFCLKSEL (3'b001),

.QPLL1REFCLKSEL (3'b001),

同理,而CPLL 的可选参考时钟源 GTREFCLK0 是MGTREFCLK0 通过 IBUFDS_GTE4 后提供的,GTREFCLK1 是MGTREFCLK1(不能使用) 通过 IBUFDS_GTE4 后提供的;

.CPLLREFCLKSEL (3'b001),

程序中每个CHANNEL 的 CPLL0REFCLKSEL 都选择了MGTREFCLK0 通过 IBUFDS_GTE4 后提供的参考时钟

官方例程中使用了4个CHANNEL(可扩展),GTHE3/4_CHANNEL 和 GTHE3/4_COMMON 使用的是 BANK 226里的,MGTREFCLK使用的是BANK 227 的MGTREFCLK0,即上图中的模式,其他Quad的MGTREFCLK 通过 IBUFDS_GTE4后提供给本Quad里的 CPLL 和 QPLL 作为参考信号

完成的布局布线也符合上述说明

三、通过QPLL 或 CPLL 得到 LineRate

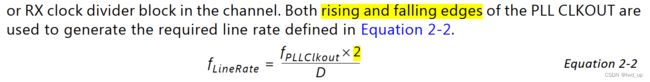

通过CPLL或者QPLL产生的信号经过选择器后进入T/RX clock divider (1, 2, 4, 8, 16)得到 Lane 时钟,根据不同的TX Clock Dividers 和 RX Clock Dividers ,在同一个 CHANNEL 里 TX_LineRate 可以不同于 RX_LineRate(整数)

由于 PLL CLKOUT 的上升沿和下降沿都有效,LineRate 如下图所示,D是Clock Dividers

对于 QPLL0/1 或者 CPLL ,LineRate 都如下所示

未完,后续见 AD9371 官方例程HDL详解之JESD204B TX侧时钟生成 (二)