使用virtuoso和calibre对版图进行DRC& LVS的检查

merge

将ICC产生的GDSII版图文件,使用virtuoso的library manager,与标准单库的版图文件以及IO库的版图文件做merge;

也可以使用华大的EDA工具aether,进行版图的merge和调用calibreDRC LVS的检查;

简述工艺情况

本项目所用的 SIMC的.18 的工艺,项目为纯数字电路,未使用RAM 等宏单元和其他IP; 添加IOpad

DRC

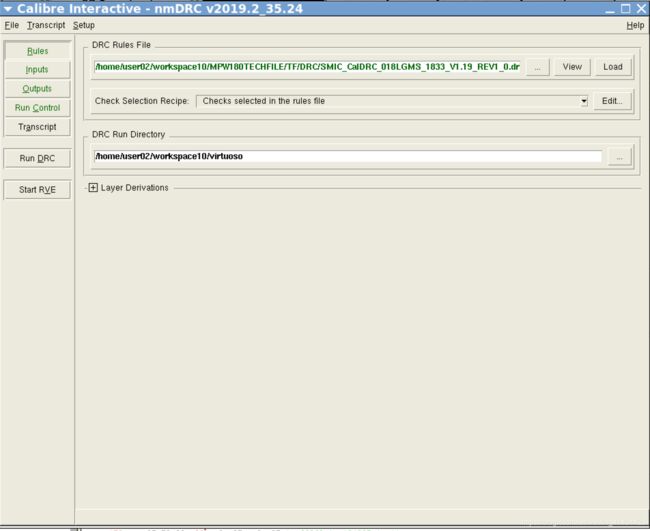

在virtuoso中调用 calibre 进行DRC的检查;

前提是 ICC中已经不出现 DRC violated nets 以及annote 效应; 或者ICC中的DRC问题无法解决;

使用工艺库中提供的RULE文件:

rule文件一般存放的位置 /TF/DRC/ ***.rule

输入有两种选择; 一是在virtuoso中读入 merge后的版图文件; 在窗口中勾选 export from layerout view 意思是从当前读入的版图进行相关的检查;

然后直接run DRC进行DRC的检查

出现的问题

- M3_11_v123

Space between two Mn regions when one or both Mn with >= 3-level continuous stacked via arrays (include TV), >= 3.0um - DRC waive when metal edge encloses stacked via array > 10um.

- DRC only flag space violation region when Parallel run length >= 15um.

The continuous stacked via array definition:

- Two vias whose space is <= 5um are considered to be in the same array, two via arrays with spacing <= 10um will be treated as one via array.

- All via array overlapped width is >= 5um, and parallel run length >= 15um.

- Each layer via density >= 1.66/um2,Top via density >=1.29/um2.

- The vias in stacked via array interact with the same interlayer metal.

- The 3-level continuous stacked via array means the stacked via array are 3 continuous via layers and corresponding 2 continuous stacked interlayer metals all have no metal cross (DRC waive width <= 2um metal line and check all interlayer metals projected space > 0um).

这个规则信息来自于工艺库中给定的Design rule文档;

根据不同类型的违例 可去文档中查询;

此问题出现在IO中,IO使用的.18库中的标准IO,DRC可以忽略,但是学习态度,分析违例:

当一个或两个Mn通过阵列(包括TV)≥3级连续堆叠时,> = 3.0um时,两个Mn区域之间的空间

1.当金属边缘围成大于10um的阵列堆叠时,DRC免收。

2.当并行游程长度> = 15um时,DRC仅标记空间违反区域。

连续堆叠通过数组定义:

1)间距小于等于5um的两个通孔被视为在同一阵列中,间距小于等于10um的两个通孔阵列将被视为一个通孔阵列。

2)所有过孔阵列的重叠宽度> = 5um,平行走线长度> = 15um。

3)每层通孔密度> = 1.66 / um2,顶部通孔密度> = 1.29 / um2。

4)堆叠过孔阵列中的过孔与相同的夹层金属相互作用。

5)3级连续堆叠通孔阵列意味着堆叠通孔阵列是3个连续通孔层,并且对应的2个连续堆叠的层间金属都没有金属交叉(DRC宽度<= 2um金属线,并检查所有层间金属投影空间> 0um )。

IOpad 由多层金属连续堆叠,连续堆叠,就会有堆叠的via阵列;

TV 是指:

2.由于在ICC布局布线时,由于一些不可抗力的影响 无法完成 VDD VSS的pad和power ring的连接,现在ICC输出的版图只对VSS pad 和VSS 连上了,使用的M1和M3,由于电源pad的特殊性 现在看是6层金属都有用.

(driver_pg_pin 无法连接VDD VSS的小伙伴,可以尝试在coarse placement之后,使用 preroute_instance命令,分析问题的原因,可能与floorplan时, VSS VDDpad的摆放有关,可尝试在crate_floorplan 时添加 -pad_limite 在粗布局之后再次执行preroute_instance 可能会造成placement无法执行,由于pad的坐标未指定)

由于VDD pad未连接,似乎所有的pad,在LVS时 都未指定port脚,出现的问题如下:

要将pad 头 打lable(标签) 将port与pad一一对应起来;像txt层一样,标识器件和端口;

解释一下pin与label的关系。pin是一个cadence内部数据,标示了层次之间的逻辑连接,并且有其对应的物理位置信息。label仅仅是逻辑概念,为对应的金属连线加入一个线网名称。

你使用calibre做lvs,而calibre输入为GDS,GDS中是没有pin这样的定义的,只有label。所以在做lvs的时候必须加入label。

至于label使用的层,这个不一定,需要看lvs rule中如何定义。并不是使用什么层做pin就必须使用一样的层做label。一般来说text层可以对应全部金属层,而金属层做的label需要lvs rule中指定对应关系才可以。

pin定义物理与逻辑关系,label只有逻辑。只有在virtuoso环境内才能识别pin,所以我们在做版图时候既要画pin也要写label。这是为了保证我们使用其他工具如calibre时候可以识别端口。如果你只用calibre做lvs,那text是必须的,pin没有作用。

除了所有的33个IO pad之外,由于VDD未连接也要将power ring上的VDD 打上 lable;

notice: 上面所说的打 port的lable 是为了LVS的通过,DRC 检查之前将 未连接的VDD 连接出来就好了;在LVS时 可以根据LVS的报告 对layerout进行修改;

LVS

在virtuoso中调用calibre的lvs

在进行LVS之前 通过v2lvs

将.v的网表转化成 spec网表

v2lvs -v aestop_io_pred.v -l ../MPW180TECHFILE/STC/verilog/scc018ug_hd_rvt.v \

-l ../MPW180TECHFILE/IO/verilog/SP018W_V1p8.v -o aestop_io.spi \

-s ../MPW180TECHFILE/STC/cdl/scc018ug_hd_rvt.cdl \

-s ../MPW180TECHFILE/IO/lvs/SP018W_V1p8a.sp

在v2lvs产生的网表,需要做一下修改,这个修改可以在.v的时候修改,也可以在吐出spi网表之后,

- 由于在rtl网表中并未声明VDD VSS等电源信息;

要在spi网表中添加:

.GLOBAL VDD VSS

.GLOBAL VNW

.GLOBAL VPW

.GLOBAL FP

*.CONNECT VDD VNW

*.CONNECT VSS VPW

*VPW VNW为N井 P井的供电

工艺库IO lvs文件夹下一般会有对应的sp网表 会有助于检查错误.

在工艺库中给的IO中, 还有FP pin

2. 注释掉网表中生成的filler的实例:

*XPCORNER cornernl

除此之外要将 pad的sp文件和标准单元的cal文件 include进来;

.INCLUDE "../MPW180TECHFILE/IO/lvs/SP018W_V1p8a.sp"

.INCLUDE "../MPW180TECHFILE/STC/cdl/scc018ug_hd_rvt.cdl"

包括标注单元的filler tapfiller Corner IOfiller

endcap好像不用注释;

Xxoendcap!FDCAPHD4!229 FDCAPHD4

以下filler要注释掉:

Xxxofiller

Xtapfiller

Xcorner

Xpfiller

在LVS的rule的选择,读入工艺库文件中给定的LVS规则

输入input的选择:hierarchical,layerout VS netlist,在 H-cells选项中 可以勾选 match cells by name;

在LVS option中勾选 connect all nets by name

可以将未连接的VDD 通过LVS检查;

下面就可以run LVS 查看其它的一些错误;

下图为为VDD VSS的power ring添加的

lable;

下图为为IO的lable

下图为pad FP连线,

notice: 那一层layer的器件 打那一层的txt;