【DRAM存储器十七】DDR2介绍-DDR2的新增技术-Post CAS、ODT、RDQS、OCD

个人主页:highman110

作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容

参考资料:《镁光DDR数据手册》

目录

Post CAS

ODT

RDQS

OCD

Post CAS

再提一下这里几个重要的时序参数:

tRCD:RAS to CAS delay,行激活到读写命令下发的时间间隔;

tRRD:不同bank间的行激活间隔。

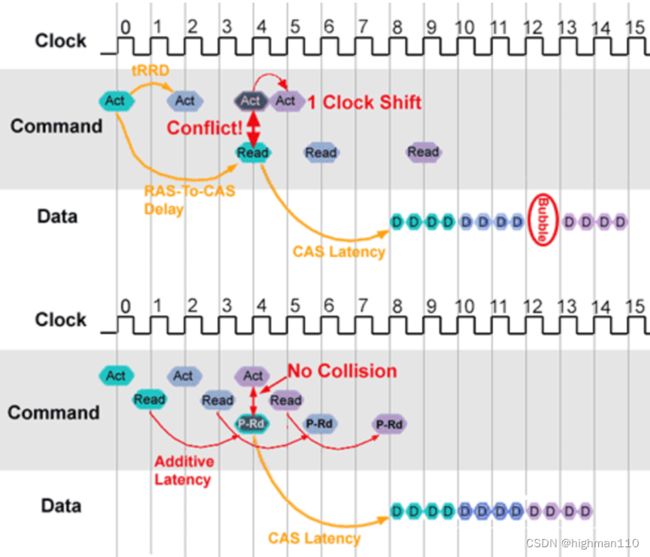

不同bank间是可以支持interleaving操作的,读写操作很频繁的时候,下一个行激活命令就可能与当前已激活行的读写命令发生冲突,毕竟命令线是公共的嘛,这时就只能把被冲突的行激活命令往后移一个时钟周期,这就降低了interleaving的效率,于是想个办法就是把CAS前移,行激活之后一个时钟周期就把读写命令先发了,发一个ACT紧接着就发读写命令,这样就永远不会有命令冲突了,毕竟tRRD的间隔肯定不止一个时钟周期。如下示意图:

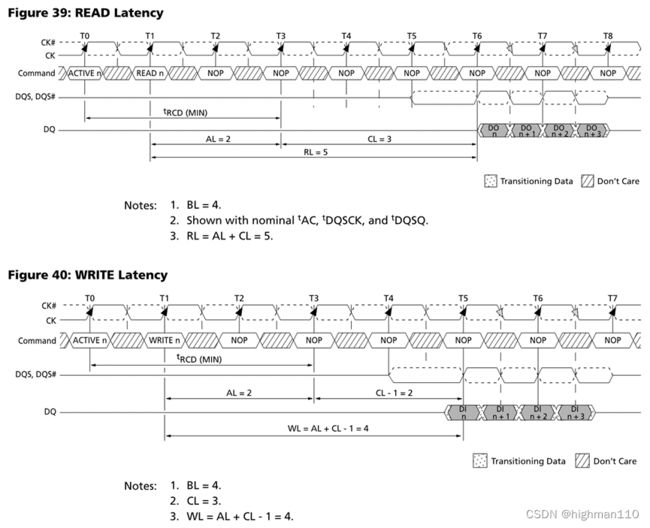

另外,需要注意,CAS前置后引入了一个新的延迟参数AL,可以理解为CAS下发后隔多久才在颗粒内部真正生效,通过配置EMR寄存器,可设置AL=0~6个时钟周期,这个AL不是0~6随便设的,要根据所选颗粒的tRCD时间决定,需要小于等于tRCD的最小值,很好理解如果AL比tRCD还大,那显然会降低总线效率,读和写的CAS前置时序图如下:

ODT

DDR的终端匹配电阻做在主板上,DDR2把它做到颗粒里面了,匹配电阻值可以通过EMR调节,有75Ω、150Ω、50Ω可选,调整原理就是配置电阻网络中一些开关的通断,如下原理图。ODT有两种使用场景,一种是控制器与颗粒的数据线是点对点的,如板贴颗粒,或者一个通道只设计了一个DIMM插槽,这个时候就是写数据时需要使能颗粒ODT,因为只有写数据,颗粒端才是终端。另一种是一个通道设计了多了DIMM插槽,这是DQ、DQS线就不是点对点了,而是点对多点,在访问其中一个DIMM时,其他的DIMM槽走线就成了STUB,所以这些槽位即使没有被访问,其ODT也应该使能来吸收反射。

RDQS

如果EMR寄存器bit11=1,则使能RDQS(Redundant data strobe),在读的时候,RDQS的功能与DQS一样,在写的时候,RDQS引脚忽略。如果bit11=0,RDQS则为DM功能。如下图:

此功能是为了X4和X8颗粒混用的场景设计的,由于X4颗粒是每4个DQ对应一个DQS,X8是8个DQ对应一个DQS,如果X4和X8混用,相应的X4多的这个DQS总要在X8颗粒上找一个引脚对应上,且这个引脚需要终端匹配来减少反射,这就是RDQS。如下图,后面的DDR3、DDR4把这个引脚名称改为了TDQS,更强调了terminate终端匹配作用。

有同学可能会问,为什么DDR没有这个引脚,到DDR2才有?因为DDR还没有ODT功能,做了这个引脚也没用,还是要在片外加终端匹配电阻。另外,DDR的速率还不算高,因stub引入的信号完整性问题还不明显,不过,还是不建议X4和X8混用。

OCD

OCD 是DDR2的可选功能,OCD的主要作用在于调整 I/O 接口端的电压,来补偿上拉与下拉电阻值,从而调整DQS与DQ之间的同步确保信号的完整与可靠性。调校期间,分别测试DQS高电平和DQ高电平,以及DQS低电平和DQ 高电平的同步情况。如果不满足要求,则通过设定突发长度的地址线来传送上拉/下拉电阻等级(加一档或减一档),直到测试合格才退出 OCD 操作,通过OCD操作来减少DQ与DQS间的skew从而提高信号的完整性。

上面这段话网上复制的,没说清楚,还有细节错误,现在再来尝试详细分析一下。

首先说OCD的目的,说白了就是希望DDR输出的DQ与DQS是完全同步的,也就是上升下降斜率尽量一致,每个0、1 UI的电平宽度尽量一致。

那为什么这个DQ与DQS的同步为什么需要校准呢?理论上DQ与DQS可以理解为是相同输出diver出来的,都与全局时钟CK是同步的,那为什么斜率有可能不一致呢?首先我们知道上升下降斜率,它与驱动电流是强相关的,那DDR2 IO的驱动电流与什么相关呢,我们从SSTL电平的输入输出结构来看:

节省点时间借用的网图,大家别介意,RS和RT阻值不一定是上图的值。左边是输出结构,通过控制上管和下管的通断来输出0和1,。输出1时,上管导通,电流路径为上图红色线:VDDQ》上管》RS》RT》VTT,输出为0时,下管导通,电流路径为上图绿色线。图中的RS通常是集成在DDR芯片内部的,在外部环境变化时,管子的导通电阻和RS会发生变化,导致输出电流变化,最终表现为信号跳变斜率变化。

那这个斜率通过调什么来校准呢?显然通过控制上管和下管的栅极电压来调整导通电阻是比较好实现的,调内部串阻RS也可以,不过要调这个电阻的话就要用电阻网络,档位越多,网络越复杂,不太方便。OCD的基本原理就是调输出驱动器的输出阻抗。

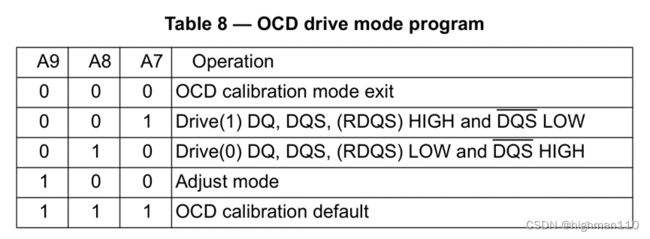

先说一下规范定义的EMR寄存器的bit[9:7]关于OCD操作的模式有如下几种:

1、000,退出OCD校准模式,在进入校准模式前和校准完毕后,都需要配置退出校准。

2、001,驱动1,DQ、DQS驱高,DQS#驱低,用来检测校准是否OK;

3、010,驱动0,DQ、DQS驱低,DQS#驱高,用来检测校准是否OK;

4、100,校准模式,在此模式下,通过所有DQ发送BL=4的校准操作码,具体的操作码如下,表中的DT0表示时间0处的所有DQ位、DT1表示时间1处的所有DQ位,依次类推,一共是4次突发。调整之后所有DQ的输出电阻将会调整成相同的值。调整的最大步数为16,当达到极限时,进一步的递增或递减代码无效。

5、111,OCD默认模式,这种模式下驱动器的默认输出阻抗为18Ω。

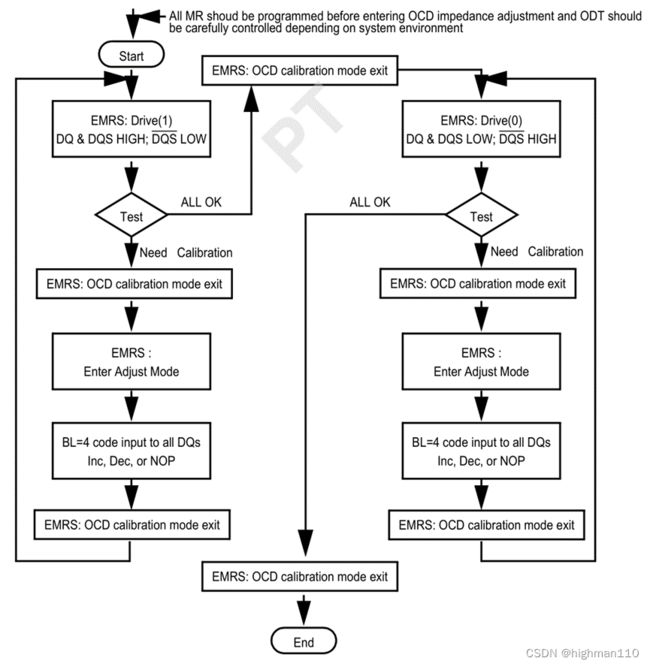

OCD校准的流程图如下:

对照上图大概描述一下OCD操作步骤:

a、在校准之前需要把所有MR配好;

b、配置EMRS进入OCD驱动模式,驱动1,检测DQ与DQS是否对齐同步;

c、若已对齐,配置EMRS退出OCD校准,然后再配置EMRS进入OCD驱动模式,驱动0;

d、若未对齐,同样先配置EMRS退出OCD校准,然后配置EMRS进入调整模式,然后通过DQ发送调整码,一次调一个step;

e、配置EMRS退出OCD校准;

f、回到b步骤。

g、驱动0的检测与调整流程与驱动1一样。