学习日记之VHDL(1)

context:

- a new design method and logic of FSM(finite state machine)

- two different kinds of reset

- safe FSM

- some trifles

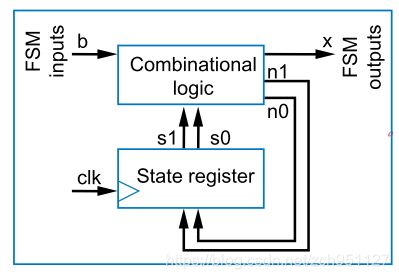

1. the structure of FSM can be divided into 2 parts: combinational logic and register logic

combinational logic describes the relationship between input and output

register logic is used to take states of FSM into control and its process is driven by CLK signal.

the module of FSM can be described in the following figure. (we assumed that this FSM has 4 different states)

to design an FSM, we may have steps below.

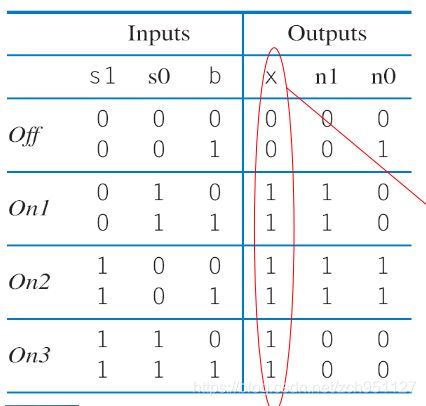

1> use truth table of input and output to design combinational logic

e.g.

according to this table, we can get the formula which can be used to describe relationships between input and output

![]()

![]()

![]()

(use Karnaugh map)

2> state register just has to transmit the new state to the input terminal of the combinational logic part which can be a simple register.

2. two different types of reset: synchronous and asynchronous

synchronous:

...

if (clk='1' and clk'event) then

if(rst='1') then

--add handler here

...asynchronous:

...

if (rst='1') then

--add handler here

elsif (clk='1' and clk'event) then

...asynchronous can still reset even if the clock is not functioning, synchronous avoids timing analysis problems sometimes accompanying asynchronous designs.

3. safe FSM

it can be a problem if there were some states that were not used in the project. so we have to set a path that can lead our process to go back to the normal state.

4. some trifles

1> How to define a new type

type 数据类型名 is 数据类型定义 of 基本数据类型;

type example1 is array(15 downto 0) of std_logic;

--an array that has 16 elements whose type is std_logic

type example2 is (a,b,c,d);

--a new enumerate set that include 4 different typessubtype 子类型名 is 基本数据类型 range 约束范围;

(subtype cannot be used to define a new type)

subtype example1 is integer range (9 downto 0);

--

subtype example2 is std_logic_vector(7 downto 0);

--

2> for and while loop

[loop label:] for 循环变量 in 循环次数范围 loop

--sequential statement

end loop [loop label];

e.g.

FOR n IN 0 TO 7 LOOP

tmp <= tmp XOR a(n);

END LOOP ;[标号 ] WHILE 循环控制条件 LOOP

顺序语句

END LOOP [标号]

e.g.

L1 : WHILE n<=8 LOOP

outputx(n)<=inputx(n + 8) ;

n := n+1;

END LOOP L1;3> about omit assignment

in general, we use "others" to assignment remaining bits or signals in a vector. and we also can use it to assign another vector.

d1<=(1=>'1', 4=>'1', others=>0)

--in the d1, the bit with index 1 and 4 assigned to 1 while others are '0'

f<=(1=>e(3), 3=>e(5), others=>e(1))

--in the vector f, the second and the third bits are assigned by e(3) and e(5) which are come from other vector e, while other bits are assigned to the value e(1).