FPGA时序分析与约束(10)——生成时钟

一、概述

最复杂的设计往往需要多个时钟来完成相应的功能。当设计中存在多个时钟的时候,它们需要相互协作或各司其职。异步时钟是不能共享确定相位关系的时钟信号,当多个时钟域交互时,设计中只有异步时钟很难满足建立和保持要求。我们将在后面的内容中介绍这部分问题,同步时钟则会共享固定相位关系。往往同步时钟产生自同一个时钟源。

如今的Soc在同一个芯片内包含多种异构设备。同一个芯片内可能包含高速的处理器和低速的存储器。这些工作在不同频率下的器件通常由不同的时钟触发。每个部分的运行是基于各自时钟的,这些会带来异步性的设计问题。这可能导致几个时钟都源于同一个主时钟,这些时钟称为生成时钟(衍生时钟、派生时钟)。

在FPGA设计中,生成时钟(Generated Clock)有两种类型:第一种是由FPGA的专用时钟管理模块(PLL/MMCM)产生的时钟(这种时钟可以由时序引擎自动推断出来);第二种是由用户通过LUT或寄存器产生的时钟(这种时钟必须由用户手动约束)。

二、如何进行生成时钟约束

2.1 约束方式

生成时钟的定义取决于主时钟的特性,生成时钟约束必须指定时钟源,这个时钟源可以是一个已经约束好的主时钟或者另一个生成时钟。生成时钟并不直接定义频率、占空比等参数,而是定义与其时钟源的相对关系,如分配系数、倍频系数、相移差值、占空比差值等。

生成时钟的约束定义能够帮助时序工具进行准确的时序分析。生成时钟约束时必须指定某个源时钟或某个已知的时钟传输扇出节点,由此时序工具才能准确地计算生成时钟相对于源时钟的插入时延。

2.2 生成时钟约束语法create_generated_clock

SDC中约束生成时钟create_generated_clock。该指令的BNF是:

create_generated_clock [source_objects]

-source clock_source_pin

[-master_clock master_clock_name]

[-name generated_clock_name]

[-edges edge_list]

[-divide_by factor]

[-multiply_by factor]

[-invert]

[-edge_shift shift_list]

[-duty_cycle percent]

[-combinational]

[-add]

[-comment comment_string]2.2.1 定义生成时钟的源

设定生成时钟的源引脚可利用-source选项,这个选项可以指明生成时钟是由哪个主时钟的源引脚派生的。

这里我们理解一下源对象和生成时钟源之间的区别,源对象指的是生成时钟(或者时钟)设定在哪个位置,而生成时钟源指的是具体是哪个获得生成时钟的参考信号。

一个源对象可以具有多个时钟。如果主时钟源引脚有多个时钟扇出,则生成时钟必须表明是由哪个主时钟派生来的。其功能可以通过-master_clock实现,这个选项采用了SDC时钟名称,该时钟已经被定义为驱动主时钟源引脚。只要定义了生成时钟,则开发工具将基于源的波形特性派生时钟特性。(如波形、周期等)

对于通过特定源生成的时钟,重要的一点是源必须能够通过某种方式保持与生成时钟的相关性。一种常见的错误是将生成时钟指定于一个并未扇出生成时钟的特定源。实际上这意味生成时钟的波形被设定在一个源引脚处的波形函数上,它与生成时钟无关。开发工具不能捕获这种情况,从而导致在静态时序分析期间将错误的时钟波形用于生成时钟。

2.2.2 时钟命名

像主时钟一样,生成时钟也需要通过名称来标识。可通过-name选项设定一个名称。若没有定义-name时,开发工具会自动指派一个名称。于生成时钟建立依赖关系后,任何SDC指令都将引用该名称。

2.2.3 设定生成时钟的特性

设定生成时钟的特性可以利用以下3个选项中的1个:

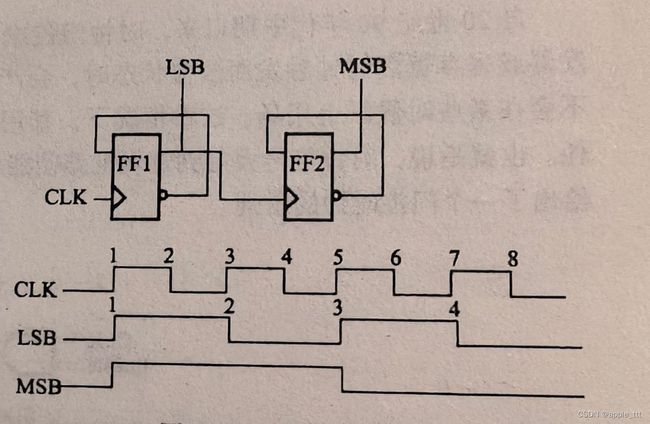

1、-edges ——作为一个对应源时钟边沿的整数数列,它表明了是从哪个生成时钟而产生的时钟边沿。时钟沿是指生成时钟交替的上升沿和下降沿。时钟沿的个数必须为奇数个整数,并且应当至少由3个整数表示一个完整生成时钟的周期。时钟沿计数由“1”开始,这个“1”表示源时钟的第一个上升沿。我们以下图为例:

create_clock -period 10 -name CLK [get_ports CLK]

create_generated_clock -name LSB -source [get_ports CLK]

-edges {1 3 5}{get_pins FF1/Q}

//用FF1/Q约束FF2/Q

create_generated_clock -name MSB -source [get_ports FF1/Q]

-edges {1 3 5}{get_pins FF2/Q}

//用CLK约束FF2/Q

create_generated_clock -name MSB -source [get_ports CLK]

-edges {1 5 9}{get_pins FF2/Q}2、-divide_by——这表示生成时钟通过某个因子而分频,周期则通过这个因子而加倍。

3、-multiply_by——这表示产生时钟通过某个因子而倍频,周期则要除以这个因子。应当注意的是,尽管时钟通过周期特性来定义,但要记住multiply_by和divide_by则是通过频率特性来设定的(即周期的倒数)。

总的来说,任何使用 -divide_by 或 -multiply_by 来表示的生成时钟也可以使用-edges来表示。反之则未必正确。

使用 -divide_by 或 -multiply_by 生成时钟有时需要进行取反,可以使用-invert选项来设定这个功能。

当定义的时钟需要倍频的时候占空比可以用-duty_cycle来设定,该选项指可以配合 -multiply_by来使用,并以表示倍频时钟为1时脉冲宽度的百分比。

2.2.4 时钟沿位移

生成时钟的时钟沿可能受到时间的影响而发生位移。-edge_shift 选项选取一组浮点数来表示在时间单元内每一个时钟沿的位移。该选项必须具有与时钟沿数量相同的参数来表示每个生成时钟沿的位移。我们举个例子进行说明:

create_generated_clock -name PLUSE -source [get_ports clk]

-edges {1 1 3} -edge_shift{0 2 0}{get_pins AN1/Z}

这段指令表示,在生成时钟上:

- 在第一个源时钟沿产生上升沿

- 在第一个源时钟沿达到后2ns后产生下降沿

- 在第三个源时钟沿产生下一个上升沿

三、总结

与主时钟相同,对生成时钟正确建模也很重要。否则可能导致时序收敛的迭代增加。由SDC约束定义的生成时钟,若其特性电路与实际功能不匹配,这很难通过调试发现。许多情况下,设计虽然与时序相符,但硬件却呈现出完全不一致的状态。

当定义生成时钟时,时钟的特性基于源时钟的特性而构成。通常可以直接通过create_clock在对象上定义相同的特性,而不利用生成时钟。从时序分析的角度来看,只要特性一致,时钟由create_generated_clock还是由create_clock设定并不重要。然而,若时钟是另一个时钟派生的,则无论何时都建议使用create_generated_clock,而非create_clock。这样做更易于维护和改进,因为修改源时钟的特性将直接影响生成时钟的特性。

同样,利用正确的约束可更好地模拟设计意图,当修改或改进约束时会减少产生错误的概率——包括移植技术和设计。

此外,当设计中多个时钟交互工作时,仅正确地定义时钟并不能满足要求,同样需要准确地定义各个时钟之间的关系。