邸老师STA笔记(二)

这里写目录标题

- 七、STA环境

-

- 7.1 create_clocks

- 7.2 clocks_uncertainy

- 7.3 clocks_latency

- 7.4 generated_clocks

- 7.5 path_delay

- 7.6 路径组

-

- 7.6.1 drive

- 7.6.2 transition

- 7.6.3 set_load

- 7.7 Design Rule Checks

- 7.8 Virtual Clocks

- 7.9 Refining the Timing Analysis

-

- 7.9.1 set_case_analysis

- 7.9.2 set_disable_timing

- 7.9.3 set_false_timing

- 7.9.4 set_multicyle_timing

- 八、时序检查

-

- 8.1 建立时间

-

- 8.1.1 Reg to Reg

- 8.1.2 Input to Reg

- 8.1.3 Reg to Output

- 8.1.4 Input to Output

- 8.2 保持时间

- 九、特殊时序检查

-

- 9.1 多周期路径

- 9.2 半周期路径

- 9.3 伪路径

书接上文,接下来是STA环境。

七、STA环境

在分析STA结果时,确定正确的约束条件是很重要的。这可以准确指定设计环境约束信息,以便STA分析能够识别所有设计中的时序问题。

STA环境包括设置时钟、指定I/O特征、伪路径和多周期路径。需要明确的是STA只能处理同步时钟。

7.1 create_clocks

要定义时钟,我们需要定义以下信息:

1、时钟源:它可以是设计的一个输入端口(input_port),也可以是设计内部单元的一个引脚(net);

2、周期:时钟的周期;

3、占空比:持续高电位时间(正相位)和低电位持续时间(负相位)。

4、边缘时间:上升沿和下降沿的时间。

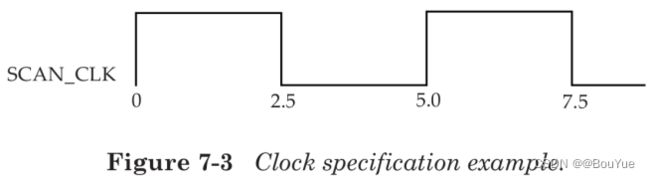

create_clock -name SYSCLK -period 20 -waveform {0 5} [get_ports SCLK]

create_clock -period 5 [get_ports SCAN_CLK]

create_clock -name BDYCLK -period 15 -waveform {5 12} [get_ports GBLCLK]

7.2 clocks_uncertainy

一个时钟周期的时序不确定性可以使用set_clock_uncertainty来指定规范。不确定性可以用来模拟各种可以减少有效时钟周期的因素。这些因素可以是时钟抖动和任何其他悲观情况。

set_clock_uncertainty -setup 0.2 [get_clocks CLK_CONFIG]

set_clock_uncertainty -hold 0.05 [get_clocks CLK_CONFIG]

set_clock_uncertainty -from VIRTUAL_SYS_CLK -to SYS_CLK -hold 0.05

set_clock_uncertainty -from VIRTUAL_SYS_CLK -to SYS_CLK -setup 0.3

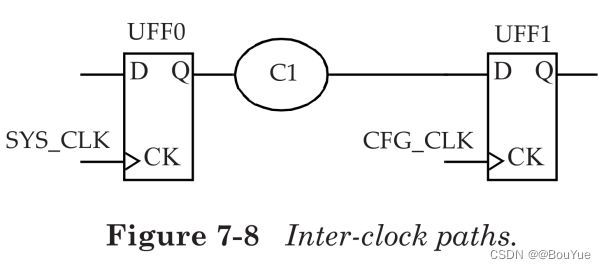

set_clock_uncertainty -from SYS_CLK -to CFG_CLK -hold 0.05

set_clock_uncertainty -from SYS_CLK -to CFG_CLK -setup 0.1

7.3 clocks_latency

时钟延迟有两种类型:网络延迟和源延迟。

源时延:也叫插入时延,是指时钟源到时钟的时延。

网络延迟:是指从时钟定义点(create_clock)到触发器的时钟引脚的延迟。

源延迟可以表示芯片上或芯片外延迟。触发器时钟引脚上的总时钟延迟是源延迟和网络延迟的和。

# Specify a network latency (no -source option) of 0.8ns for rise, fall, max and min:

set_clock_latency 0.8 [get_clocks CLK_CONFIG]

# Specify a source latency:

set_clock_latency 1.9 -source [get_clocks SYS_CLK]

# Specify a min source latency:for hode time check

set_clock_latency 0.851 -source -min [get_clocks CFG_CLK]

# Specify a max source latency: for setup time check

set_clock_latency 1.322 -source -max [get_clocks CFG_CLK]

区分源延迟和网络延迟之间的一个重要指标是时钟树,一旦设计中构建了时钟树,网络延迟就可以被忽略掉(比如set_propagated_clock)但是,即使构建了时钟树,源延迟仍然存在。网络延迟是在时钟树合成之前对时钟树延迟的估计。 综合时钟树后,触发器从时钟源到时钟引脚的总时钟时延为源延迟加上时钟树从时钟定义点到节点的实际延迟。

7.4 generated_clocks

生成时钟是由主时钟派生而来的。主时钟是用create_clock产生。当设计中基于主时钟产生一个新时钟时,新时钟可以定义为生成的时钟。且这个定义包括周期在内等一切信息,因为STA不知道输出端的时钟周期已经改变。

现在考虑是否可以在触发器的输出端定义一个新的时钟,即用create_clock另定义一个主时钟,而不是create_generated生成一个时钟?

答案是肯定的,但是也存在一些缺点。再定义一个新时钟即创建了一个新的时钟域。但实际电路中产生的新时钟并不会创建一个新的时钟域,并且产生的时钟和它的主时钟存在某种联系,即这两个时钟本质上其实是一个时钟域,生成的时钟不需要额外的延迟等约束。但create_clock的结果是产生了一个异步电路,当然也可以用伪路径进行修正,但很麻烦且得不偿失。因此,必须尝试从主时钟的基础上内部生成一个时钟,而不是决定将其声明为另一个主时钟。

主时钟和生成时钟之间的另一个重要区别是时钟源的概念。在主时钟中,时钟的源点位于主时钟的定义点。在一个生成的时钟中,时钟源是主时钟的时钟源,而不是生成的时钟源。这意味着在时钟路径报告中,时钟路径的起点总是主时钟定义点。与定义一个新的主时钟相比,这是一个生成的时钟的巨大优势,因为在新的主时钟的情况下,源延迟不会自动包括在内。

还可以为生成的时钟指定时钟延迟。在生成的时钟上指定的源延迟指定从主时钟定义到生成的时钟定义的延迟。

因此,由生成的时钟驱动的触发器的总时钟延迟 = 是总主时钟的源时延+生成时钟的源时延 + 生成时钟的网络时延。

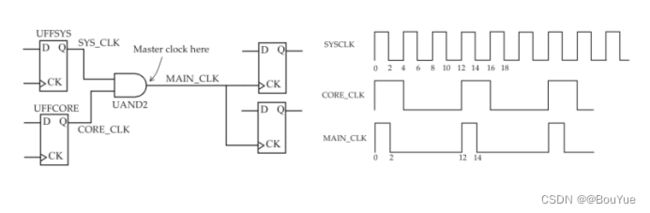

如果与单元的输入都是时钟,那么在与单元的输出处定义一个新的主时钟是安全的,因为单元的输出与任何一个输入时钟都不太可能有任何相位关系。如下图:

7.5 path_delay

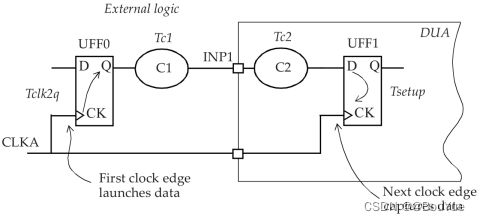

与clock相关的tcl命令只能约束clk的输入输出端口port到寄存器时钟输入输出pin的延迟,那数据输入输出的延迟用什么来考量—path_delay。例如考察输入路径的延迟,如下图:

set_input_delay -clock CLKA -max [expr Tclk2q + Tc1] [get_ports INP1]

首先此路径延迟是输入端口延迟;指的是针对于CLKA的时钟域来讲的;设置最大延迟为Tclk2 + Tcl;对应输入的引脚是INP1。

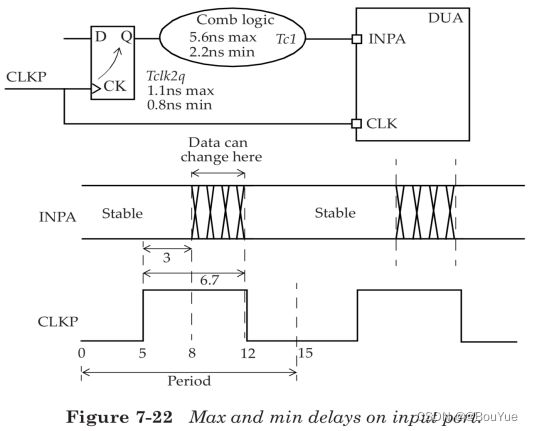

create_clock -period 15 -waveform {5 12} [get_ports CLKP]

set_input_delay -clock CLKP -max 6.7 [get_ports INPA]

set_input_delay -clock CLKP -min 3.0 [get_ports INPA]

也可以分别对路径设置最大最小延迟,用来检查建立时间和保持时间。

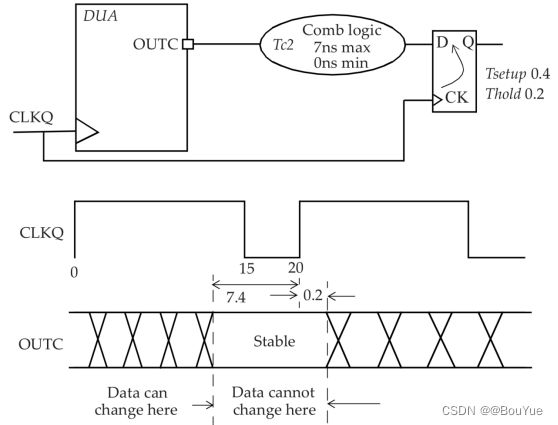

set_output_delay -clock CLKQ -max [expr Tc2 + Tsetup] [get_ports OUTB]

首先此路径延迟是输出端口延迟;指的是针对于CLKQ的时钟域来讲的;设置最大延迟为Tc2 + Tsetup;对应的输出端口是OUTB。

create_clock -period 100 -waveform {5 55} [get_ports MCLK]

set_input_delay 25 -max -clock MCLK [get_ports DATAIN]

set_input_delay 05 -min -clock MCLK [get_ports DATAIN]

set_output_delay 20 -max -clock MCLK [get_ports DATAOUT]

set_output_delay -5 -min -clock MCLK [get_ports DATAOUT]

7.6 路径组

对于路径的输入输出端口,需要设置相应的端口属性,对于输入有三个命令:set_drive、set_driving_cell、set_input_transition对于输出,需要指定输出引脚的容性负载。这是由set_load指定的。

7.6.1 drive

set_drive指定了DUA输入引脚可驱动的电阻值,也就是驱动能力。驱动值越小,驱动强度越高。阻值为0意味着理想无穷的。细分可设置上升驱动和下降驱动。

# Specifies a drive resistance of 100 on input UCLK

set_drive 100 UCLK se rved.

# Rise drive is different from fall drive:

set_drive -rise 3 [all_inputs]

set_drive -fall 2 [all_inputs]

输入端口的驱动强度用于计算第一个单元的翻转时间。指定的驱动值还用于计算从输入端口到任何RC互连的第一个单元的延迟。

Delay_to_first_gate = (drive * load_on_net) + interconnect_delay

set_driving_cell提供了一种更方便和准确的方法来描述端口的驱动强度,即把链接库里面某一个端口的驱动强度赋给此端口。

# The input INPB is driven by an INV3 cell from library slow.

set_driving_cell -lib_cell INV3 -library slow [get_ports INPB]

# Specifies that the cell INV2 from a library tech13g is the driving cell for all inputs.

set_driving_cell -lib_cell INV2 -library tech13g [all_inputs]

# The input testmode[3] is driven by a BUFFD4 cell from library tech90gwc.

set_driving_cell -lib_cell BUFFD4 -library tech90gwc [get_ports {testmode[3]}]

7.6.2 transition

Transition 翻转时间除了上面计算可以直接设置,使用set_input_transition。

# Specifies an input transition of 850ps on port INPC.gh

set_input_transition 0.85 [get_ports INPC]

# Specifies a transition of 600ps on all input ports.

set_input_transition 0.6 [all_inputs]

# Specifies a transition of 250ps on all ports with pattern SD_DIN*.

# Min and max values can optionally be specified using the -min and -max options.

set_input_transition 0.25 [get_ports SD_DIN*]

总之,需要在输入处设置一个翻转值来确定输入路径中第一个单元格的延迟。在没有此规范的情况下,假设理想的翻转值为0,这是不现实的。

7.6.3 set_load

set_load规范在输出端口上放置容性负载,以模拟由输出端口驱动的外部负载的情况。 缺省情况下,端口的容性负载为0。负载可以指定为显式电容值或cell的输入引脚值。

# Places a 5pF load on output port OUTX.

set_load 5 [get_ports OUTX]

# Sets 25pF load capacitance on all outputs.

set_load 25 [all_outputs]

# Place 7fF pin load on the specified output port.

# A load on the net connected to the port can be specified using the -wire_load option.

# If neither -pin_load nor -wire_load option is used, # the default is the -pin_load option.

set_load -pin_load 0.007 [get_ports {shift_write[31]}]

指定输出负载非常重要,因为此值会影响驱动的单元的延迟输出。在没有这样的规范的情况下,负载为0可能是不现实的。

set_load [get_attribute [get_lib_pins tech_lib/NAND2/A] pin_capacitance] [all_outputs]

7.7 Design Rule Checks

STA的两个常用设计规则是最大跃迁和最大电容max transition and max capacitance。检查设计中的所有端口和引脚是否满足 transition and max capacitance的要求。主要使用两条命令:set_max_transition & set_max_capacitance 。示例:

# Sets a limit of 600ps on IOBANK.

set_max_transition 0.6 IOBANK

# Max capacitance is set to 0.5pf on all nets in current design

set_max_capacitance 0.5 [current_design]

7.8 Virtual Clocks

虚拟时钟是一个存在但不与设计的任何引脚或端口相关联的时钟。它被用作STA分析中的参考,以指定相对于时钟的输入和输出延迟。

create_clock -name VIRTUAL_CLK_SAD -period 10 -waveform {2 8}

create_clock -name VIRTUAL_CLK_CFG -period 8 -waveform {0 4}

create_clock -period 10 [get_ports CLK_CORE]

set_input_delay -clock VIRTUAL_CLK_SAD -max 2.7 [get_ports ROW_IN]

set_output_delay -clock VIRTUAL_CLK_CFG -max 4.5 [get_ports STATE_O]

7.9 Refining the Timing Analysis

为了使时序分析更加精细化,常用到四个命令:

1、set_case_analysis:指定单元的引脚或输入端口上的常数值。

2、set_disable_timing:中断单元格的时序弧。

3、set_false_path:指定伪路径,这意味着这些路径不被检查。

4、set_multicycle_path:指定可以超过多周期周期的路径。

7.9.1 set_case_analysis

在设计中,某些信号在芯片的特定模式下具有常数值。例如,如果芯片中有DFT逻辑,那么在正常功能模式下,芯片的TEST引脚应该是0。在STA中指定这种情况。

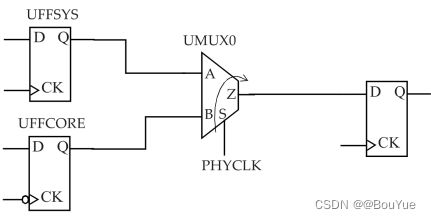

另一个常见应用是设计有多个时钟,而时钟的选择由多路选择器控制。为了简化STA分析并减少CPU运行时间,故在STA阶段对每个时钟选择器执行此功能。例如:

set_case_analysis 1 UCORE/UMUX0/CLK_SEL[0]

set_case_analysis 1 UCORE/UMUX1/CLK_SEL[1]

set_case_analysis 0 UCORE/UMUX2/CLK_SEL[2]

7.9.2 set_disable_timing

在某些情况下,穿过cell的特定路径可能不会发生。可以使用set_disable_timing SDC命令来中断这条时序弧。

set_disable_timing -from S -to Z [get_cells UMUX0]

7.9.3 set_false_timing

set_false_path -from [get_clocks USBCLK] -to [get_clocks MEMCLK]

7.9.4 set_multicyle_timing

create_clock -name CLKM -period 10 [get_ports CLKM]

set_multicycle_path 3 -setup -from [get_pins UFF0/Q] -to [get_pins UFF1/D]

八、时序检查

静态时序分析的时序检查分为建立时间检查和保持时间检查,检查的时序路径有四种,最常见的是寄存器到寄存器的时序,即前一个寄存器的clk到下一个寄存器的D端。

8.1 建立时间

8.1.1 Reg to Reg

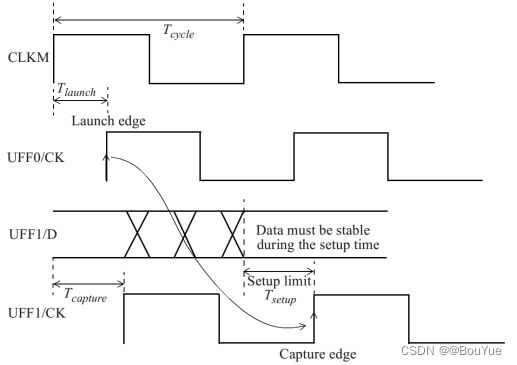

如下图所示:

UFF1的数据传输路径是:首先时钟CLKM经过时钟树Tlaunch延迟到达UFF0的CK端;然后UFF0的CK经过Tck2q延迟到达Q;最后经过组合逻辑延迟Tdp到达UFF1的D。

UFF1的时钟沿传输路径是:CLKM经过Tcapture到达UFF1的CK端。

那么对于UFF1来讲,时钟上升沿和数据有效能否成功“匹配”就是建立时间检查的本质。结合前文反复提到的概念再次深刻理解。

建立时间:数据再时钟上升沿到来之前,数据要稳定的时间。即数据要想传输必须先稳定不变,时钟才能采到正确的值。建立时间是发生在数据传输前,也就是寄存器D端接受数据数据前。

如何用公式表征这一关系?看如下波形图:

由上述分析可得:

数据到达UFF1的D 端所花时间为:Tlaunch + Tck2q + Tdp;

时钟到达UFF1的CK端所花时间为:Tcapture + Tcycle – Tsetup;

数据提前到达,即:

Tlaunch + Tck2q + Tdp < Tcapture + Tcycle – Tsetup;

8.1.2 Input to Reg

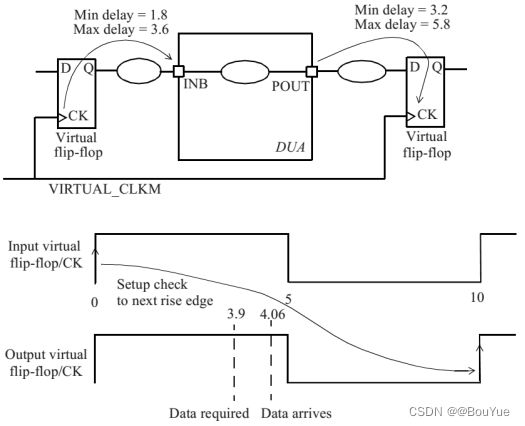

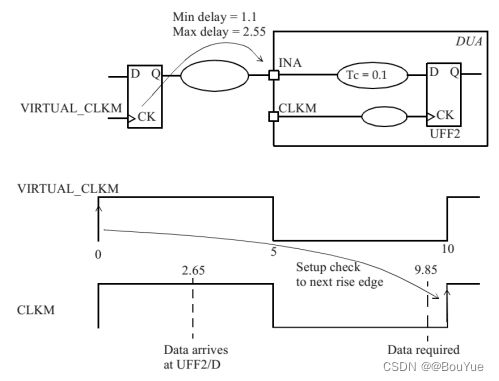

如上图,对方框括起来的进行STA,首先对待分析模块加约束,max用于检查建立时间,min用于检查保持时间。此时需要用到虚拟时钟:

creat_clock –name VIRTUAL_CLKM –period 10 –waveform {0 5}

set_input_delay –clock VIRTUAL_CLKM –max 2.55 [get_ports INA]

8.1.3 Reg to Output

8.1.4 Input to Output

8.2 保持时间

保持时间:数据在时钟上升沿之后,依然能保持稳定的时间。即数据接受后依然能保持一段时间,确保把数据传给下一级。保持时间是发生在数据接收后,也就是寄存器D端接收数据之后,要把数据给Q传递。

由上述分析可得:

数据下传需要最少时间:Tcapture + Thode;

新数据到来时间: Tlaunch + Tck2q + Tdp;

新数据到来的慢一点,即 Tlaunch + Tck2q + Tdp > Tcapture + Thode.

九、特殊时序检查

9.1 多周期路径

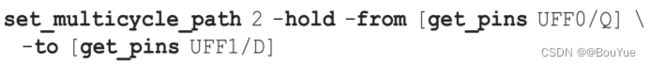

在某些情况下,两个触发器之间的组合逻辑路径可能需要一个以上的时钟周期才能到达。在这种情况下,组合逻辑路径被声明为多周期路径。 我们指示STA 相关的时钟捕获边缘在指定的时钟周期数之后开始捕获。

施加的时序约束如下:

波形如下:

通常在大多数设计中,指定为N的多周期路径设置应该伴随着设置N-1的保持时间检查周期。

9.2 半周期路径

当两个触发器的触发沿不同就有可能出现半周期,如下图:

两个电路传数据,使用半周期电路,这样建立时间非常短,但保持时间非常宽松。DDR双数据传输。